作者:李玉童、張飛

Cadence 公司 DSG Product Validation Group

InterposerBus Routing with

Integrity 3D-IC

2.5D/3D-IC 目前常見的實(shí)現(xiàn)是基于中介層的 HBM-CPU/SOC 設(shè)計(jì),Integrity 3D-IC 將以日和周為單位的手動(dòng)繞線加速到秒級(jí)和分鐘級(jí),輕松滿足性能、信號(hào)電源完整性與設(shè)計(jì)迭代的多重要求,為高帶寬高數(shù)據(jù)吞吐量的機(jī)器學(xué)習(xí)、超算、高性能移動(dòng)設(shè)備、端計(jì)算等應(yīng)用提供最佳設(shè)計(jì)支持。

在邁向先進(jìn)制程的進(jìn)程中,硬件功能的擴(kuò)展不斷地受到挑戰(zhàn),使得超大規(guī)模計(jì)算中心和人工智能(AI)設(shè)計(jì)對(duì)運(yùn)算效能和數(shù)據(jù)傳輸?shù)囊蟛粩嗟靥岣摺O冗M(jìn)系統(tǒng)單晶片(SoC)在尺寸上已經(jīng)到了光罩的極限,因此需要找到創(chuàng)新的解決方案來(lái)延續(xù)摩爾定律,并且降低功耗、提高效能。

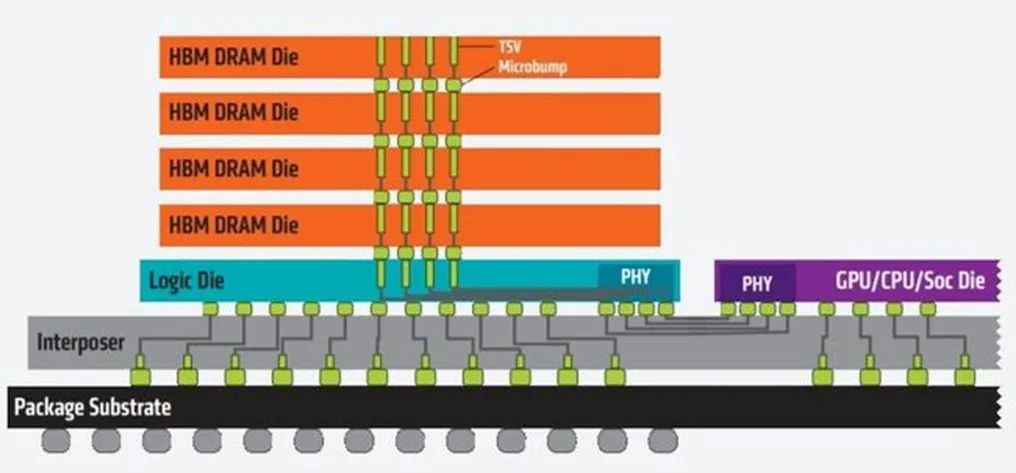

在同一封裝中將晶片做 3D 立體堆疊,和使用硅中介層的多小晶片系統(tǒng) 2.5D 封裝,已經(jīng)成為新的解決方案。當(dāng)然,這兩種方式也面臨著各自的挑戰(zhàn)。

如今,許多設(shè)計(jì)使用硅中介層連接多個(gè)晶粒來(lái)實(shí)現(xiàn) 2.5D 整合。中介層的物理實(shí)現(xiàn)涉及晶片之間的布線(如 HBM 和 ASIC 之間)或晶片和封裝基板之間的布線。空間擁塞和有限布線層數(shù)帶來(lái)極大挑戰(zhàn)。此外,片間互連通常須要經(jīng)過比片上互連更長(zhǎng)的距離,因此它們必須盡可能直線連接,減少轉(zhuǎn)折及跳層次數(shù),并且必須滿足信號(hào)完整性和長(zhǎng)距離走線特殊的要求。

傳統(tǒng)手動(dòng)布線為應(yīng)對(duì)上述挑戰(zhàn)需耗費(fèi)海量人工時(shí)間,而 Cadence Integrity 3D-IC 能以更高的完成質(zhì)量大大加速這一流程:

Cadence Integrity 3D-IC

自動(dòng)布線解決方案的優(yōu)勢(shì)

極短的運(yùn)行時(shí)間(以分鐘為單位)

近乎 100% 的屏蔽率

均勻分布的線長(zhǎng)

盡量少的過孔數(shù)量

1Integrity 3D-IC 平臺(tái)

可以實(shí)現(xiàn)最佳自動(dòng)布線

不同類型的產(chǎn)品對(duì)于 HBM 的數(shù)量和擺放位置有著不同的需求。無(wú)論 HBM 的擺放的位置如何,HBM 和 SoC 的連接都有如下共同的設(shè)計(jì)挑戰(zhàn)。

設(shè)計(jì)挑戰(zhàn)

1總線布線 – HBM 設(shè)計(jì)是為了滿足高帶寬高數(shù)據(jù)吞吐量的要求,為了使得高位寬的各個(gè)位數(shù)據(jù)同步到達(dá),HBM 和中央 SoC/CPU/ASIC 的數(shù)據(jù)必須以物理總線模式連接。

2線長(zhǎng)限制 – 晶粒間互聯(lián)本來(lái)就很可能遠(yuǎn)長(zhǎng)于晶粒內(nèi)連線長(zhǎng)度,所以要盡可能縮短布線長(zhǎng)度。

3同層繞線 – 為了提高更好的信號(hào)均一特性以及減少跳層,需要盡可能多在同層繞線。

4靈活的信號(hào)線與屏蔽線配置 – 設(shè)計(jì)者有靈活配置信號(hào)線和屏蔽線的寬度以及間距甚至所用層的需求。

下圖是一個(gè)比較常見的 2.5DIC HBM 和 SoC 平面布局圖, SoC 居中布置,左右兩邊各放兩個(gè) HBM:

這些復(fù)雜的設(shè)計(jì)挑戰(zhàn)使得后端工程師、封裝工程師和系統(tǒng)設(shè)計(jì)工程師在使用傳統(tǒng)工具進(jìn)行中介層手動(dòng)設(shè)計(jì)時(shí)不得不花費(fèi)海量的時(shí)間和人力不斷進(jìn)行調(diào)整,而調(diào)整之后的結(jié)果也未必最佳,不得不進(jìn)行大量的高時(shí)間成本和工具成本的設(shè)計(jì)迭代修正。一個(gè)典型的中介層設(shè)計(jì)常常需要數(shù)周之久。

為了解決傳統(tǒng)工具手動(dòng)設(shè)計(jì)中介層布線的痛點(diǎn),Cadence 推出 Integrity 3D-IC 平臺(tái)中介層全自動(dòng)布線流程:

Integrity 3D-IC 可以方便的讀入 Bump 擺放數(shù)據(jù)并以總線模式將來(lái)自不同晶片的 Bump 進(jìn)行最佳布線連接。下圖展示了針對(duì)中介層的 Integrity 3D-IC 設(shè)計(jì)流程,該流程已被廣泛應(yīng)用于各種 2.5D/3D-IC 設(shè)計(jì)流程中并已得到流片驗(yàn)證。

2Integrity 3D-IC 平臺(tái)

提供簡(jiǎn)明直觀的交互式用戶界面

如前文所述,中介層設(shè)計(jì)中用戶會(huì)根據(jù)實(shí)際產(chǎn)品對(duì)信號(hào)線和屏蔽線的寬度、間距、布線層提出各種各樣復(fù)雜變化的定制化需求。

為此,Cadence Integrity 3D-IC 平臺(tái)提供簡(jiǎn)明直觀的交互式用戶界面:

中介層自動(dòng)布線的交互界面

1用戶只需鍵入 Bump 區(qū)域范圍和布線參數(shù)工具就會(huì)自動(dòng)抓取指定區(qū)域的 Bump,并根據(jù)指定的參數(shù),對(duì) Bump 自動(dòng)分組,并選取優(yōu)化的布線組合。

2如果用戶沒有指定 Bump 區(qū)域,Integrity 3D-IC 會(huì)掃描整個(gè)芯片,把符合 HBM 形式的 Bump 全部抓取出來(lái)并自動(dòng)分類。

3信號(hào)線的寬度和間距可以通過設(shè)計(jì)規(guī)則指定,也可以由用戶直接指定。屏蔽線的寬度和間距可由用戶界面指定,也可以由 Integrity 3D-IC 根據(jù)屏蔽參數(shù)在信號(hào)線中間自動(dòng)計(jì)算預(yù)留空間以確保屏蔽的有效和完全。

此外批處理布線模式允許用戶生成腳本文件,以便保存和復(fù)現(xiàn)。Integrity 3D-IC 還可以根據(jù)布線的資源自動(dòng)計(jì)算寬度和間距,在需要的時(shí)候還可以考慮 45 度連接。最終通過超級(jí)命令 Route Design-Bump 將所有 Bump 連接布線自動(dòng)完成。

3Integrity 3D-IC 平臺(tái)

中介層自動(dòng)布線實(shí)例

在主干(Trunk)部分,Integrity 3D-IC 嚴(yán)格地使用總線模式布線,并用同一層金屬盡可能的延伸到 Bump 附近。為了減少過孔的使用,即使在 Bump 附近,Integrity 3D-IC 也是用同一層金屬拐彎而不跳線,盡可能保證線上電阻和電容的均一性。在 Trunk 部分,屏蔽率是 100%,在接近 Bump 的布線,短線部分缺省不加屏蔽。用戶可以選擇是否要把高層的短線和引腳一起都加上屏蔽。

Trunk 部分的屏蔽率是 100%

Bump 區(qū)域布線

兩側(cè) Bump 區(qū)域有偏移

當(dāng)用戶使用多于 6 個(gè) HBM 時(shí),由于 SoC 尺寸小。HBM 的 Bump 無(wú)法和 SoC 的 Bump 完全對(duì)齊。如果采用 90 度的折線拐彎,既浪費(fèi)布線資源,又會(huì)造成線長(zhǎng)差異。Integrity 3D-IC 檢測(cè)到這種情況會(huì)自動(dòng)采用 45 度布線方式:

45 度折線局部細(xì)節(jié)

雖然我們強(qiáng)烈推薦用戶使用全自動(dòng)布線以實(shí)現(xiàn)分鐘級(jí)的快速布線,Integrity 3D-IC 也提供強(qiáng)大友好的編輯復(fù)制功能。但在一組 Bump 布線完成后,用戶可以對(duì)這組布線進(jìn)行眼圖仿真,當(dāng) SI/PI 都達(dá)到指標(biāo)后,用戶可以選中這一組的線和過孔,通過靈活的平移、翻轉(zhuǎn)、旋轉(zhuǎn)的動(dòng)作把線和過孔復(fù)制到另一組 Bump 上,Integrity 3D-IC 會(huì)自動(dòng)對(duì)目標(biāo) Bump 完成同樣的布線連接。

Cadence Integrity 3D-IC 能將日趨復(fù)雜的 2.5D/3D 中介層布線速度提高上萬(wàn)倍(周分鐘),從而大大加快設(shè)計(jì)的迭代速度,為復(fù)雜電子系統(tǒng)的設(shè)計(jì)者們提供了無(wú)限優(yōu)化的可能!

原文標(biāo)題:3D-IC 設(shè)計(jì)之中介層自動(dòng)布線

文章出處:【微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

3D

+關(guān)注

關(guān)注

9文章

2950瀏覽量

109430 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1346瀏覽量

105231 -

Cadence

+關(guān)注

關(guān)注

66文章

963瀏覽量

143811 -

布線

+關(guān)注

關(guān)注

9文章

790瀏覽量

84887

原文標(biāo)題:3D-IC 設(shè)計(jì)之中介層自動(dòng)布線

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Cadence推出HBM4 12.8Gbps IP內(nèi)存系統(tǒng)解決方案

Cadence攜手臺(tái)積公司,推出經(jīng)過其A16和N2P工藝技術(shù)認(rèn)證的設(shè)計(jì)解決方案,推動(dòng) AI 和 3D-IC芯片設(shè)計(jì)發(fā)展

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

基于TSV的3D-IC關(guān)鍵集成技術(shù)

Cadence宣布收購(gòu)Secure-IC

Cadence收購(gòu)Secure-IC強(qiáng)化嵌入式安全布局

加特蘭集成Cadence DSP,升級(jí)汽車成像雷達(dá)解決方案

加特蘭與Cadence合作開發(fā)下一代汽車成像雷達(dá)解決方案

Cadence與Samsung Foundry開展廣泛合作

Cadence展示完整的PCIe 7.0 IP解決方案

剖析 Chiplet 時(shí)代的布局規(guī)劃演進(jìn)

Samsung 和Cadence在3D-IC熱管理方面展開突破性合作

Cadence與Intel Foundry的戰(zhàn)略合作取得重大成果

借助云計(jì)算加速3D-IC可靠性的機(jī)械應(yīng)力模擬

Cadence Integrity 3D-IC自動(dòng)布線解決方案

Cadence Integrity 3D-IC自動(dòng)布線解決方案

評(píng)論