DP1363F是高度集成的收發(fā)器芯片,用于13.56Mhz的非接觸式通訊。DP1363F收發(fā)器DP1363F支持下列操作模式

? 兼容CLRC663/RC663

? 讀寫模式支持 ISO/IEC 14443A/MIFARE

? 讀寫模式支持 SO/IEC 14443IB

? JIS X 6319-4 讀寫模式支持(等效于FeliCa1方案)

? 相應(yīng)于 ISO/IEC 18092 的被動(dòng)發(fā)起方模式

? 讀寫模式支持 ISO/IEC 15693

? 讀寫模式支持 ICODE EPC UID/EPC OTP

? 讀寫模式支持 ISO/IEC 18000-3 mode 3/ EPC Class-1 HF

DP1363F芯片特性

? 高射頻輸出功率的前端IC,傳輸速度高達(dá)848 kbit/s

? 支持ISO/IEC 14443A/MIFARE,ISO/IEC 14443B和FeliCa

? 相符于ISO/IEC 18092的P2P被動(dòng)發(fā)起方模式

? 支持ISO/IEC 15693,ICODE EPC UID和ISO/IEC 18000-3模式3/ EPC Class-1 HF

? 以讀寫模式支持MIFARE經(jīng)典加密

? 低功耗卡片檢測(cè)

? 符合“EMV非接觸式協(xié)議規(guī)范V2.0.1“所要求的發(fā)射功率

? 天線連接僅需用用最少量的外部元件

? 支持的主機(jī)接口:

- SPI高達(dá)10 Mbit/s

- I2C總線接口,高速模式可達(dá)400 kBd,超高速模式則可高達(dá)1000 kBd

- RS232串行UART,最高至1228.8 kBd,電壓水平由引腳電源電壓決定

? 獨(dú)立 I2C總線接口用于連接安全訪問模塊(SAM)

- 512字節(jié)大小的FIFO緩沖器提供最高通信性能

- 靈活和高效的省電模式,包括斷電模式,待機(jī)模式和低功耗卡片檢測(cè)

? 由27.12 MHz晶振源通過集成的PLL產(chǎn)生系統(tǒng)時(shí)鐘,從而節(jié)省成本

? 3.3V 至 5V 的電源

? 多達(dá)8個(gè)可自由編程的輸入/輸出引腳

? 與ISO/IEC 14443A/MIFARE卡的讀寫通信模式典型操作距離可達(dá)12厘米,取決于天線的尺寸和調(diào)諧

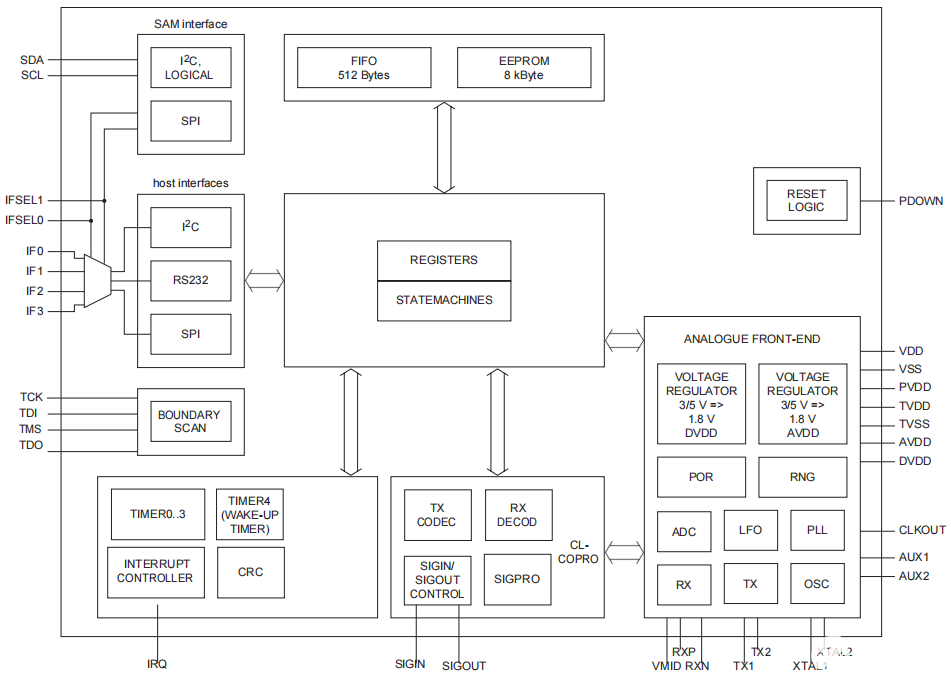

DP1363F結(jié)構(gòu)框圖

-

讀寫器

+關(guān)注

關(guān)注

3文章

699瀏覽量

39534 -

收發(fā)器芯片

+關(guān)注

關(guān)注

0文章

13瀏覽量

8404

發(fā)布評(píng)論請(qǐng)先 登錄

THA1024T具有待機(jī)模式的高速CAN收發(fā)器英文手冊(cè)

光纖收發(fā)器與IO-Link收發(fā)器的區(qū)別

DP1363F是一款非接觸讀寫芯片,高性能、多協(xié)議NFC讀卡IC

單端K總線收發(fā)器DP9637兼容L9637

常用于OBD系統(tǒng)的CSM9241總線收發(fā)器芯片選型

AFE77xx集成收發(fā)器中的時(shí)分雙工(TDD)模式

DP1332E國(guó)產(chǎn)NFC讀卡芯片,兼容替代PN5321

光纖收發(fā)器pwr是什么意思

DP83847 DsPHYTER II單通道10/100以太網(wǎng)收發(fā)器數(shù)據(jù)表

DP83865全功能物理層收發(fā)器數(shù)據(jù)表

DP83849C以太網(wǎng)物理層收發(fā)器數(shù)據(jù)表

DP83849ID以太網(wǎng)物理層收發(fā)器數(shù)據(jù)表

DP83848x以太網(wǎng)收發(fā)器數(shù)據(jù)表

DS36277主導(dǎo)模式多點(diǎn)收發(fā)器數(shù)據(jù)表

DP83640協(xié)議收發(fā)器數(shù)據(jù)表

DP1363F收發(fā)器芯片的操作模式及特性

DP1363F收發(fā)器芯片的操作模式及特性

評(píng)論