引言

近年,隨著半導(dǎo)體工藝技術(shù)的持續(xù)發(fā)展,大量手機、物聯(lián)網(wǎng)、人工智能、高性能計算等領(lǐng)域所應(yīng)用的專業(yè)芯片陸續(xù)采用FinFET先進工藝來實現(xiàn),以滿足高性能設(shè)計需求。面對先進工藝技術(shù)、高復(fù)雜度產(chǎn)品設(shè)計等方面的挑戰(zhàn),如何保證產(chǎn)品達成靜電防護能力的需求指標(biāo)?本文將分享芯耀輝靜電防護團隊的經(jīng)驗及應(yīng)對策略。

先進工藝帶來的挑戰(zhàn)

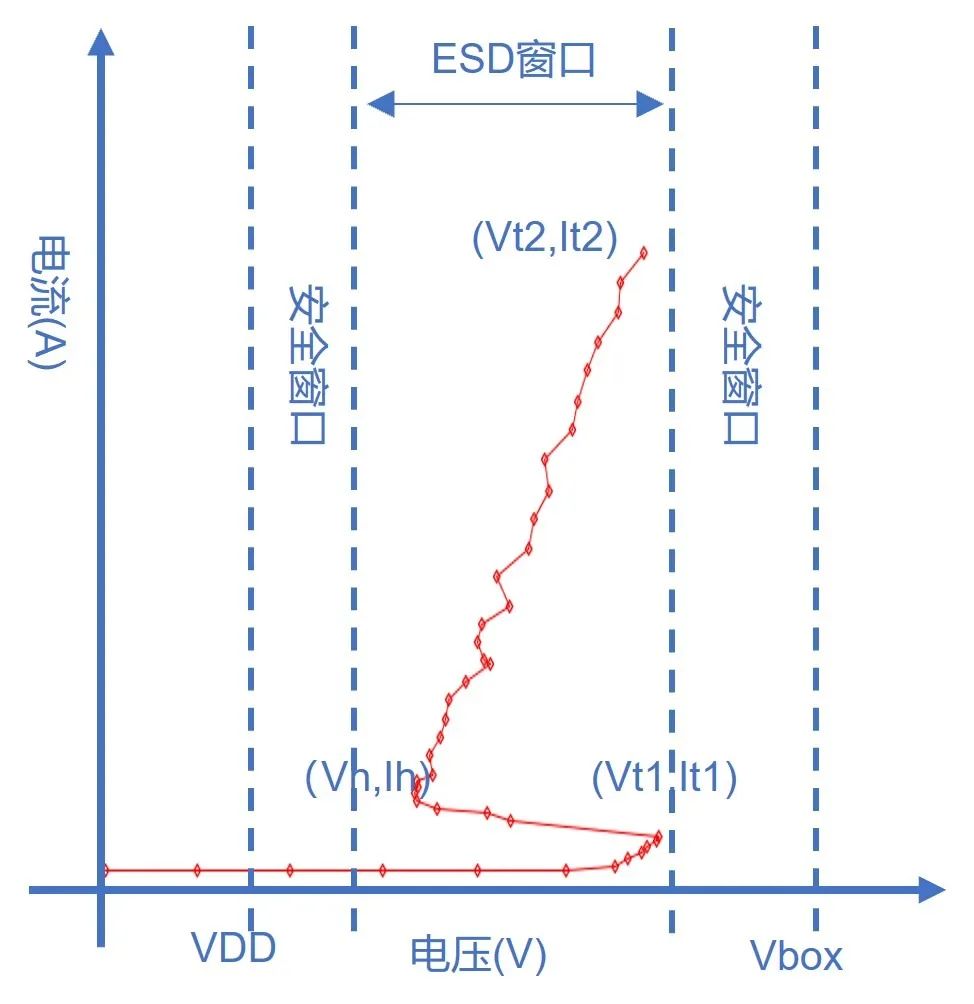

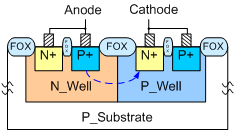

芯片級別的靜電防護,我們通常是指HBM(人體放電模式),MM(機器放電模式)和CDM(充電放電模式),其中MM在JESD22-A115標(biāo)準(zhǔn)中不再推薦測試。對于HBM/CDM傳統(tǒng)的設(shè)計方式是為被防護的內(nèi)部電路(例如Gate Oxide)添加靜電防護電路(例如GGNMOS ESD device),這些位于IO pad或者內(nèi)部電路的防護器件通常具備相比Gate oxide Breakdown Voltage(Vbox)較低的開啟電壓(Vt1),并留有一定的電壓安全余量,以保證內(nèi)部電路的安全,如下圖1所示。

圖1:GGNMOS TLP IV-Curve&防護窗口

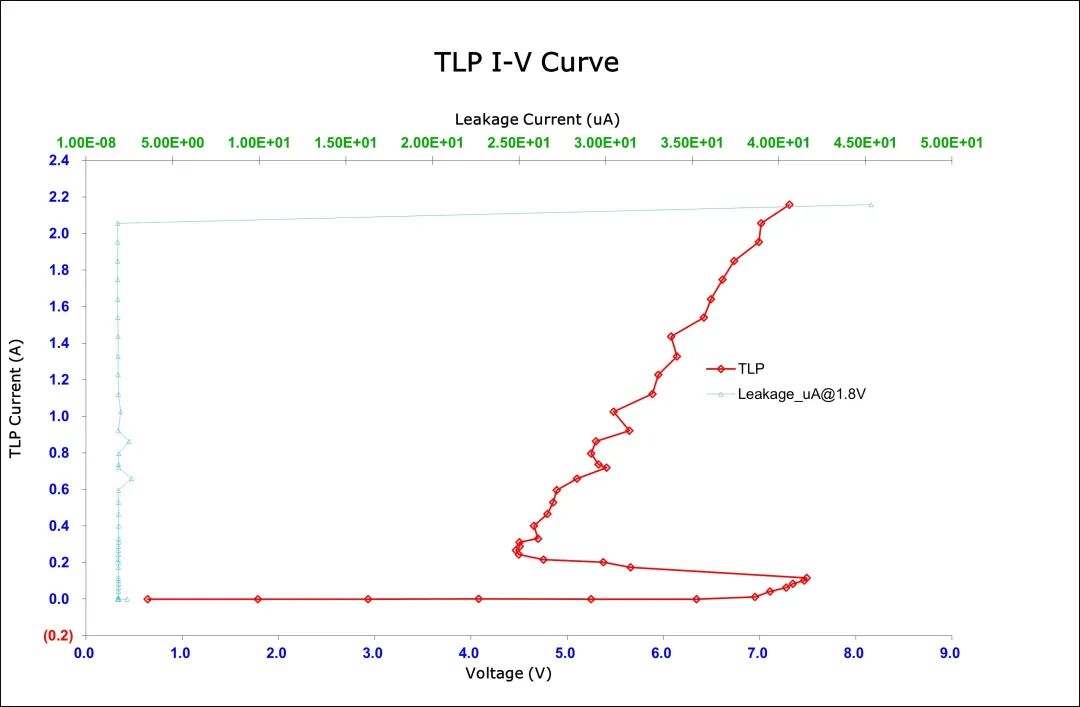

如下圖2實際管腳的TLP IV curve圖所示,可以看到GGNMOS在Vt1=8V左右觸發(fā)防護,并且提供了It2=2.0A左右的防護能力,根據(jù)HBM靜電放電模型(R=1.5KΩ),大致可以推算等效HBM 3KV(2A*1.5K=3KV)的HBM靜電防護能力。

圖2:實測GGNMOS TLP IV-Curve

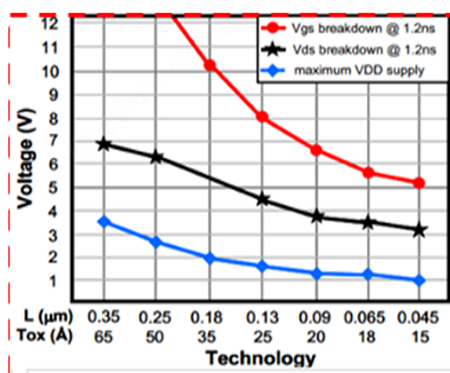

28nm以下的先進工藝,器件channel length/oxide厚度持續(xù)縮減,對應(yīng)的Breakdown電壓也一再持續(xù)降低。過往0.35um~40nm工藝時代,無論IO器件或是相對脆弱的Core器件,盡管Vgs breakdown/Vds breakdown電壓持續(xù)走低,但其特性基本都延續(xù)了Vgs_bv> Vds_bv的趨勢,并且保留了一定的安全設(shè)計余量,使得靜電放電事件發(fā)生時,防護器件可以比被防護器件更先啟動,達成保護被防護器件的功能。

圖3:成熟工藝節(jié)點Breakdown Voltage

(來源:Industry Council on ESD Target Levels)

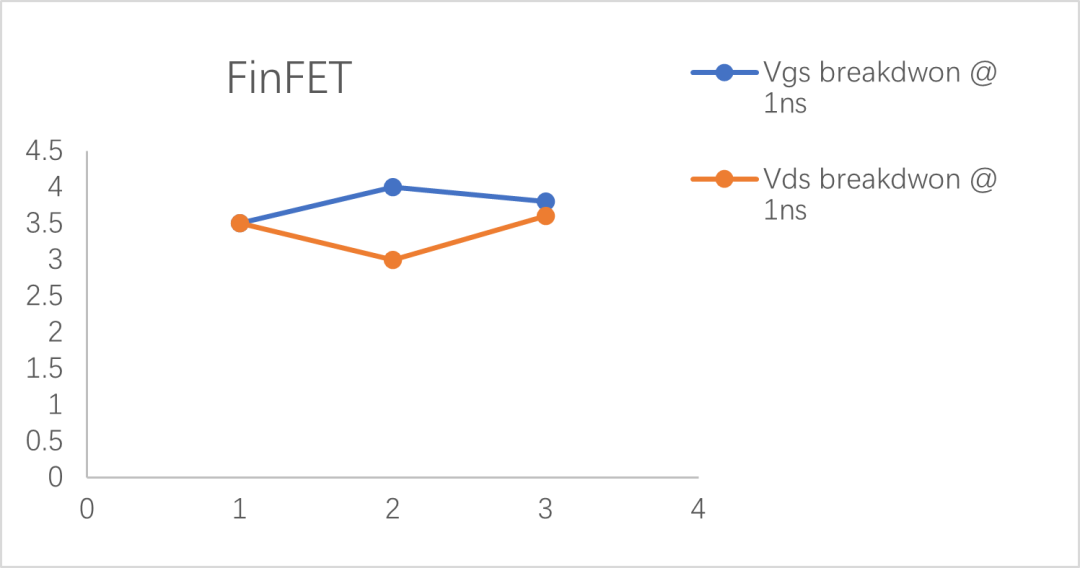

圖4:FinFET高級工藝節(jié)點Breakdown Voltage

然而來到FinFET工藝時代,如圖4所示,Vds/Vgs Breakdown電壓不僅降低到3.0V附近,遠低于65nm時代的6V,并且Vgs breakdown/Vds breakdown已經(jīng)非常接近,“安全余量”窗口消失不見了,這就使傳統(tǒng)的防護結(jié)構(gòu)特別是CDM防護受到了挑戰(zhàn)。

芯耀輝靜電防護設(shè)計團隊基于測試結(jié)構(gòu)表現(xiàn)的實際Silicon數(shù)據(jù)、靜電防護和電路設(shè)計,通過防護器件選型、防護電路結(jié)構(gòu)調(diào)整等方面的共同創(chuàng)新,達到促進防護器件提前Breakdown、降低被防護器件在放電發(fā)生時遭受的電壓降、恢復(fù)具備足夠余量的“安全窗口”,從而使得基于FinFET工藝的IP擁有了幾乎接近成熟工藝的表現(xiàn),并且不會帶來漏電或者過大面積的開銷。

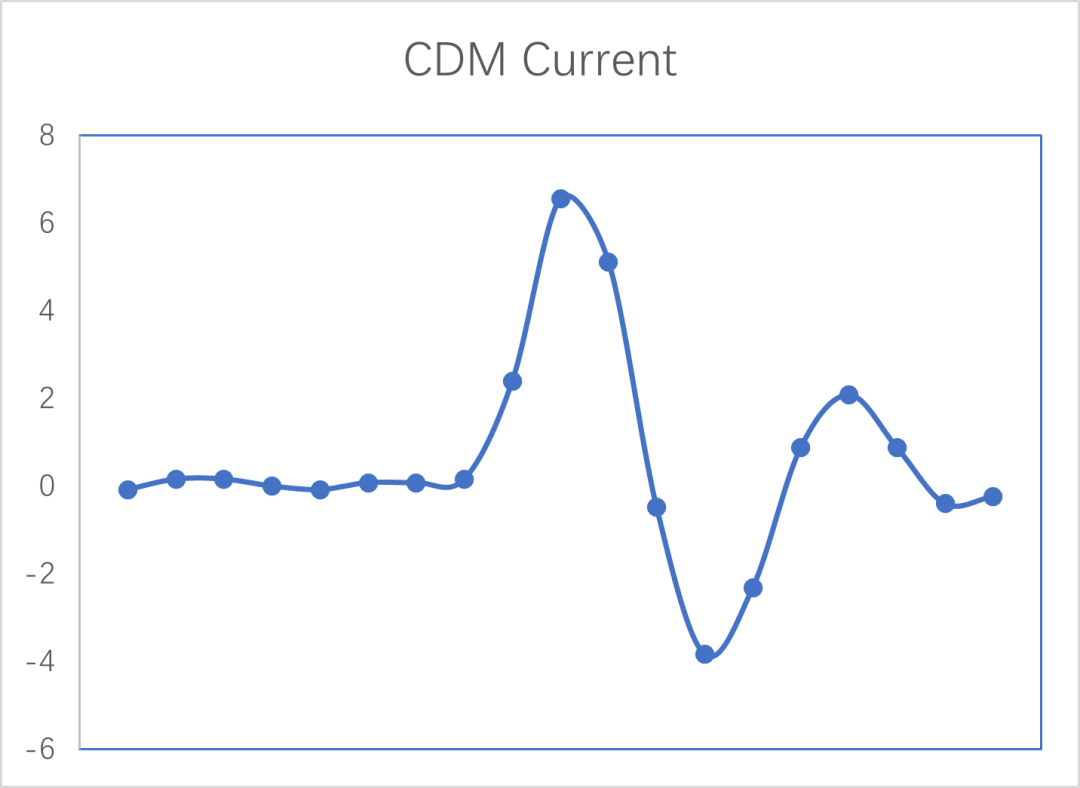

“TEST-TO-FAIL”的理念也深入貫徹在芯耀輝的靜電防護設(shè)計中。通常芯片級ESD測試按照J(rèn)EDEC或者AECQ-100的標(biāo)準(zhǔn)執(zhí)行完成后,出于測試芯片數(shù)量或者成本的考慮,靜電防護測試就算完成了。但芯耀輝靜電防護團隊的測試方案不會止步于此,秉承“TEST-TO-FAIL”的理念,團隊會盡力收集每類實測結(jié)構(gòu)的最大值。如圖5所示,例中的芯片CDM+500V下,某一管腳放電波形Ipeak可以達到6A。有些尺寸較小的芯片CDM+500V對應(yīng)的放電電流可能只有1~2A,如僅簡單復(fù)用1~2A 的方案,6A 產(chǎn)品將無法達標(biāo)。得益于“TEST-TO-FAIL”的測試支出帶來的數(shù)據(jù)積累,靜電設(shè)計人員在項目開始之初就能選用合適的設(shè)計規(guī)格,確保IP開發(fā)的成功。

圖5:CDM測試電流

高度集成SoC的復(fù)雜度

所帶來的挑戰(zhàn)

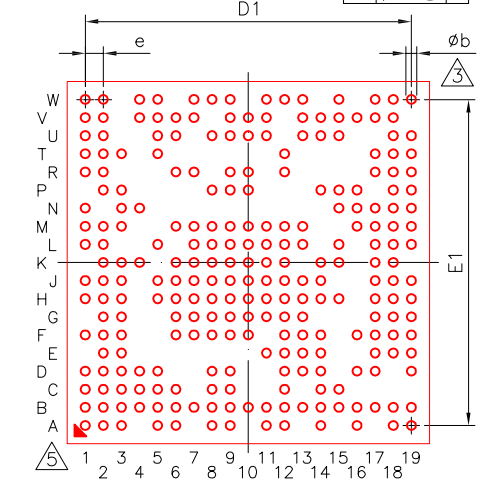

先進的SoC芯片不僅采用FinFET高級工藝以持續(xù)提升產(chǎn)品性能和競爭優(yōu)勢,而且集成度、復(fù)雜度也越來越高,如圖6為芯耀輝科技的一款測試芯片Ball POD,就具備幾百個Ball。

ESD需要處理眾多不同Ball間跨電壓域的防護問題,相比單一器件級的產(chǎn)品會復(fù)雜很多。

圖6:測試芯片Ball POD

系統(tǒng)級靜電防護

設(shè)計帶來的挑戰(zhàn)

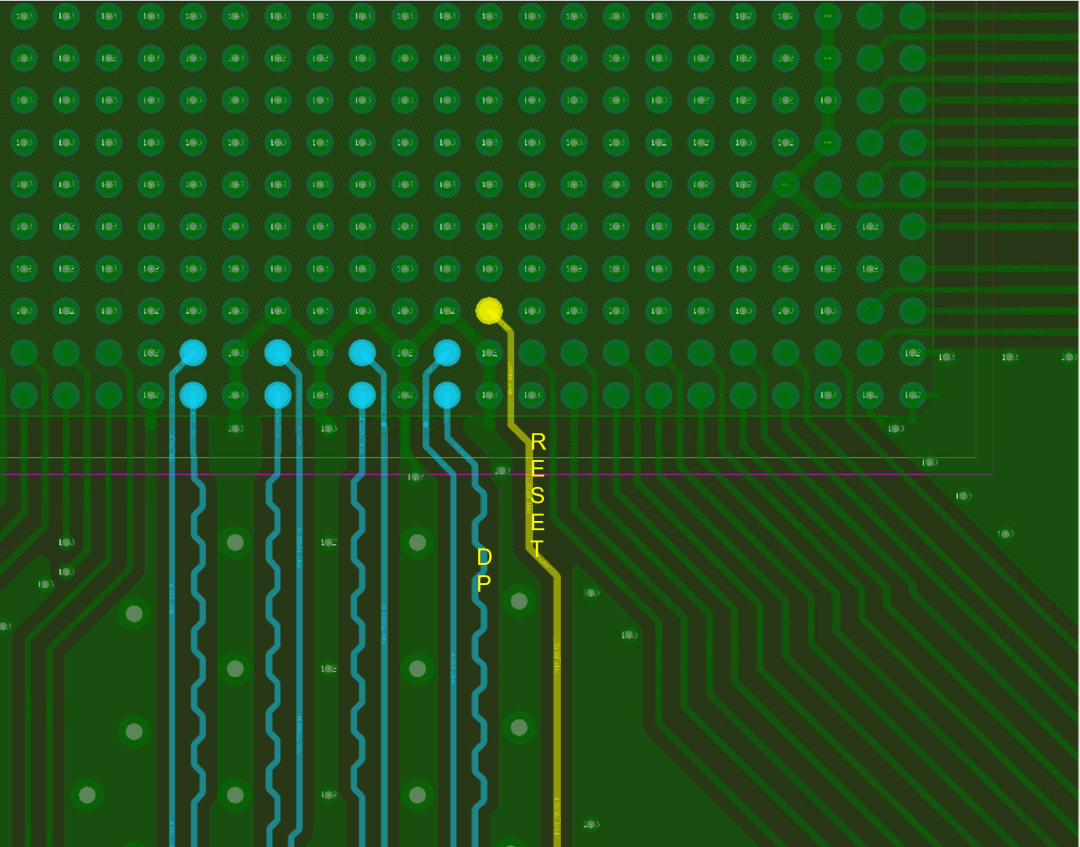

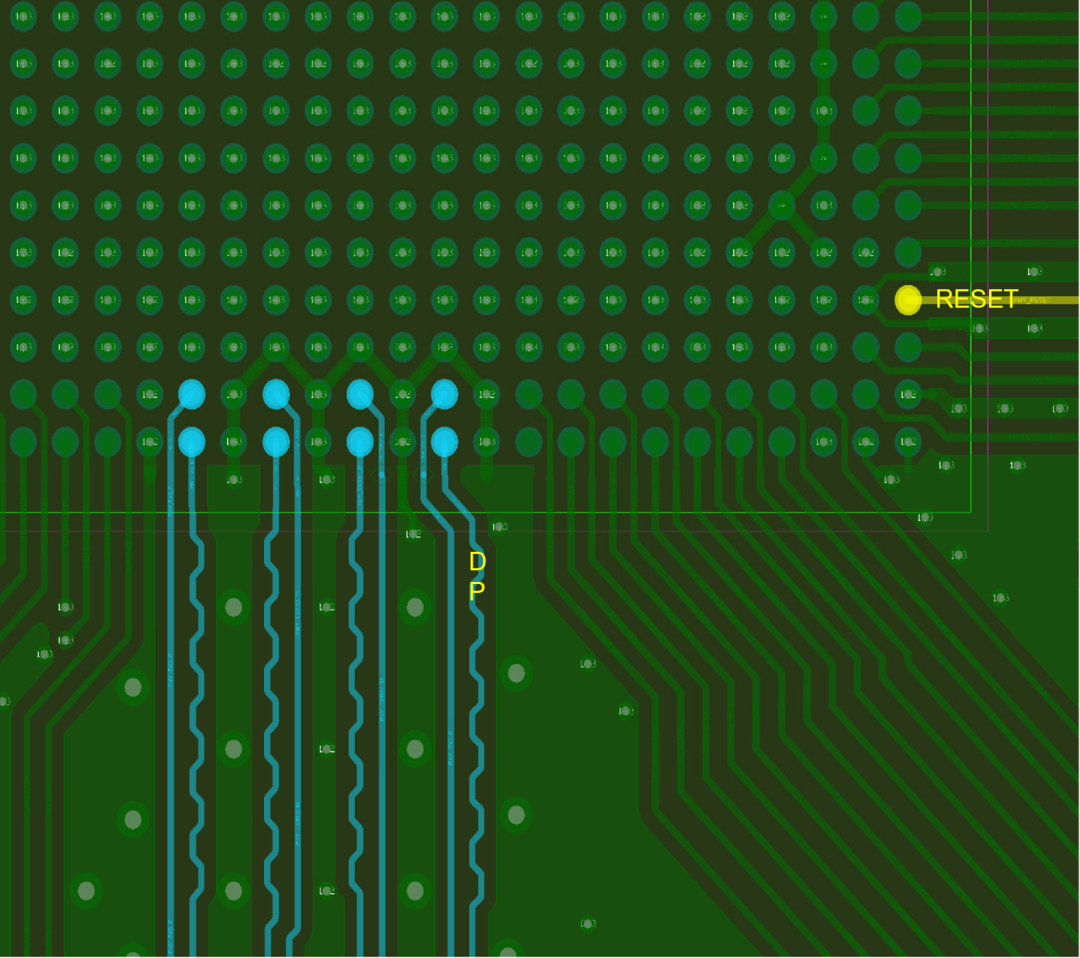

SoC芯片組裝系統(tǒng)后,按照IEC-61000-4-2標(biāo)準(zhǔn)進行電子槍接觸放電或者空氣放電測試的時候,還會有芯片重啟、芯片管腳電路燒壞等現(xiàn)象出現(xiàn),有些現(xiàn)象可以通過串聯(lián)外接電阻,并聯(lián)TVS防護器件解決。傳統(tǒng)的防護觀念認(rèn)為這是系統(tǒng)級別防護的問題,需要系統(tǒng)級別進行優(yōu)化。但在芯片設(shè)計階段也應(yīng)有相應(yīng)的方式給予提升,比如在芯片F(xiàn)loorPlan設(shè)計階段,可以對于芯片敏感信號例如CLOCK/Reset信號進行隔離,IO/ESD單元庫設(shè)計階段對特定管腳提高耐壓度等,可以使得系統(tǒng)級別實現(xiàn)達標(biāo)更為容易,這些需要靜電防護設(shè)計團隊結(jié)合芯片級、封裝級、系統(tǒng)級等各設(shè)計階段給予考慮,圖7、圖8演示了一個跨部門協(xié)同共同優(yōu)化設(shè)計的實例,標(biāo)黃色的Reset信號遠離了主信號通路,從而增強了系統(tǒng)級的靜電防護能力。

圖7:管腳位置優(yōu)化前

圖8:管腳位置優(yōu)化后

高速接口性能需求所帶來的靜電防護設(shè)計挑戰(zhàn)

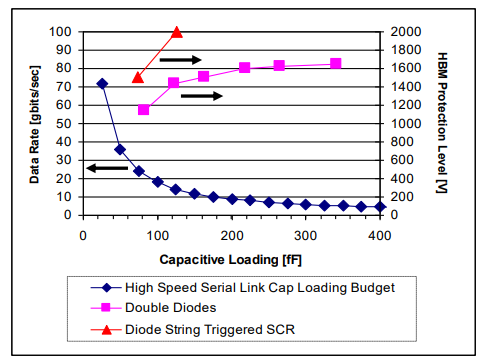

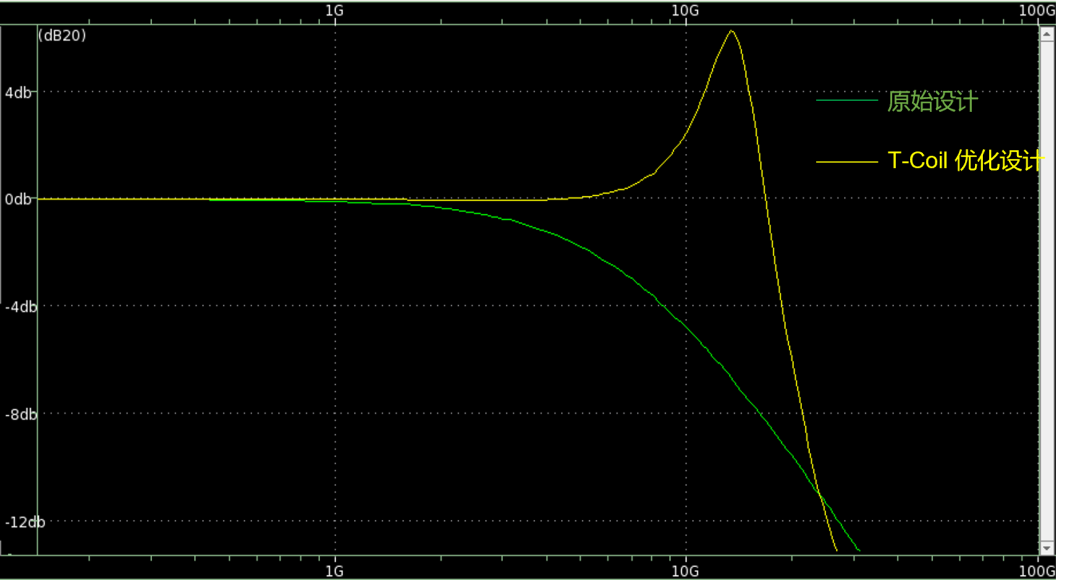

先進工藝的使用,使得高速接口設(shè)計指標(biāo)可以不斷攀升,ESD防護電路中過大的寄生電容將會使得電路帶寬受損,影響性能。實際設(shè)計中我們使用T-Coil防護結(jié)構(gòu),ESD和模擬電路設(shè)計,經(jīng)過多次的迭代,在不損失靜電防護性能的情況下保證了電路帶寬性能的達標(biāo),圖10展示了我們協(xié)同設(shè)計的效果。

圖9:High Speed Serial Link Data Rates and HBM Protection levels vs Capacitive Loading requirements

(來源:Industry Council on ESD Target Levels)

圖10:T-Coil結(jié)構(gòu)優(yōu)化前后仿真對比

完善而先進的SoC靜電防護

設(shè)計方法和流程

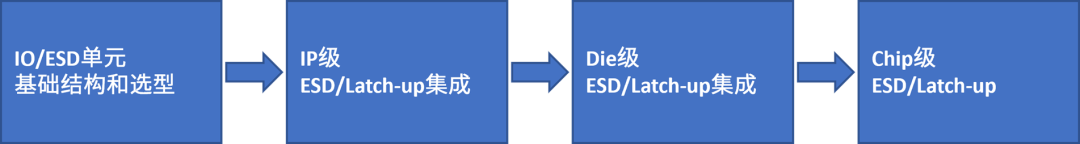

大型復(fù)雜SoC項目的實現(xiàn)往往是由不同團隊共同協(xié)作完成,從基礎(chǔ)的模塊設(shè)計到芯片頂層集成各開發(fā)節(jié)點,如何把靜電防護相關(guān)的各環(huán)節(jié)(如圖11所示)嵌入到整個項目的開發(fā)流程中,是一個巨大的挑戰(zhàn)。芯耀輝有完整的SoC靜電防護設(shè)計方法、流程和工具,讓各個設(shè)計團隊可以逐層確保IP/Die/Chip的靜電防護能力,從而保證SoC Chip系統(tǒng)芯片靜電防護順利達標(biāo)。

圖11:SoC ESD設(shè)計流程環(huán)節(jié)

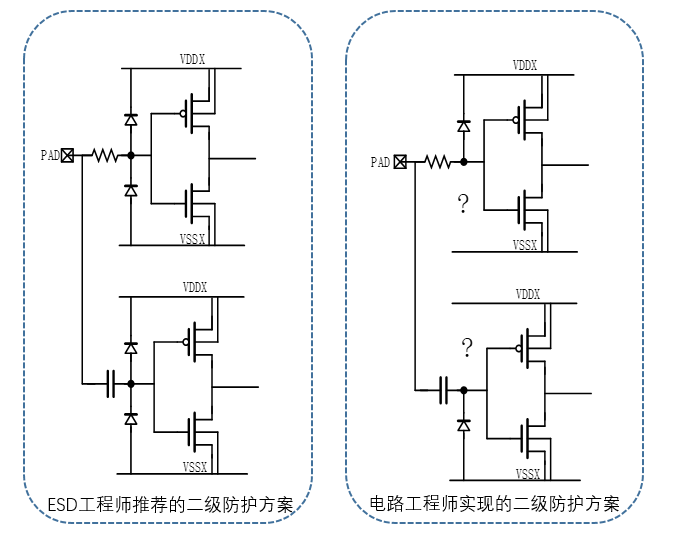

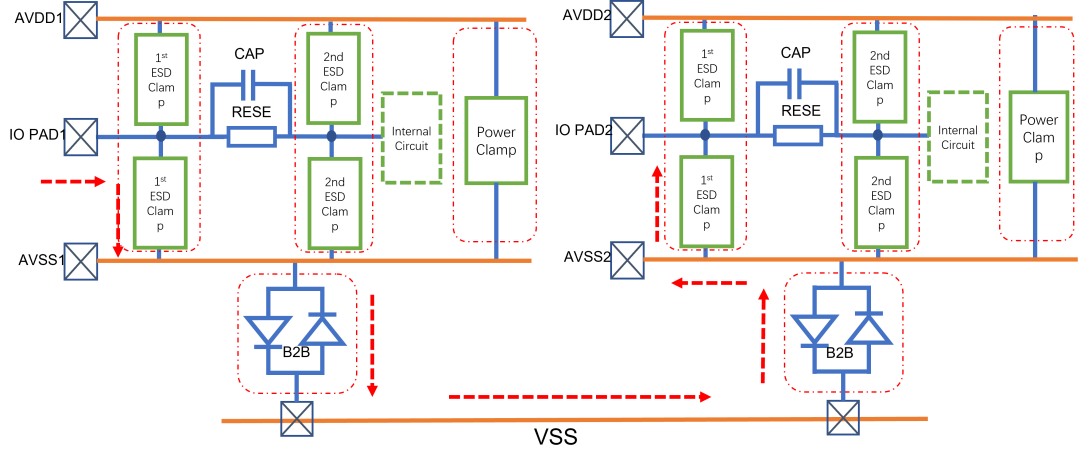

以實際設(shè)計為例,靜電防護設(shè)計工程師推薦的防護方案,在實際的電路實現(xiàn)中有可能會有偏差,如圖12所示,以致無法完全達到理想的防護效果。完善的防護流程則可以有效的避免此類偏差的出現(xiàn)。

圖12:推薦方案和實際實現(xiàn)之間的不符合

自主開發(fā)的靜電防護可靠性

設(shè)計的自動檢查流程和工具

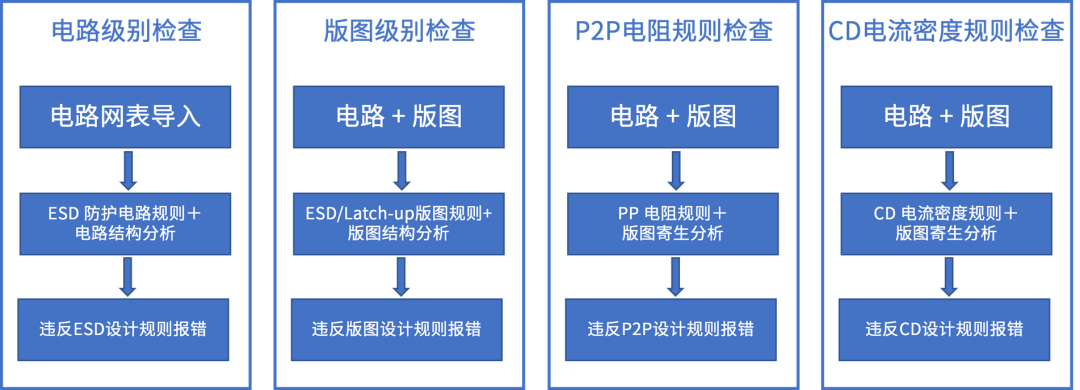

為應(yīng)對設(shè)計的高復(fù)雜度和巨大工作量,基于EDA工具的ESD自動化檢查方案應(yīng)運而生,芯耀輝科技ESD團隊總結(jié)大量的量產(chǎn)實戰(zhàn)經(jīng)驗后形成規(guī)則建議,并由公司CAD團隊自主開發(fā)了ESD可靠性設(shè)計的自動檢查流程方案,分別覆蓋:(1)電路級別檢查(2)版圖級別檢查(3)靜電防護通路寄生電阻(P2P)和電流密度檢查(CD)

圖13:自主開發(fā)的ESD可靠性設(shè)計自動檢查流程方案

圖14是電流密度(CD)檢查的一條示例,以HBM 2KV為例,注入的ESD電流等效為1.33A,如果放電路徑Diode Metal寬度或者VIA個數(shù)不能支撐2KV需求,則會報出該處坐標(biāo)位置。另外需要提及的是,大封裝規(guī)模SoC芯片CDM 500V對應(yīng)的電流超過了6A,HBM 1.33A有時候并不能覆蓋CDM的要求,需要設(shè)定更大的注入電流,芯耀輝自行開發(fā)的CAD Flow可以根據(jù)實際需求賦予不同的激勵電流,以保證覆蓋規(guī)格要求。

圖14:CD path check示例

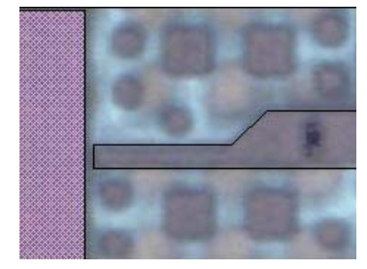

除了包含Chip level ESD/Latch-up相關(guān)的檢查和設(shè)計規(guī)則以外,在量產(chǎn)階段,ESD失效也經(jīng)常包含了RDL/Package等相關(guān)的設(shè)計問題而導(dǎo)致的靜電防護失效,芯耀輝的靜電防護設(shè)計團隊也在這些方面積累了大量的失效分析和處理經(jīng)驗。一些實際量產(chǎn)中的失效案例在相關(guān)文獻中也有過許多報道,如圖15所示為一典型的浮接金屬導(dǎo)致的失效。透過芯耀輝的靜電防護設(shè)計流程和工具檢查,RDL/Package等影響靜電防護設(shè)計的問題也能夠提前在設(shè)計階段就被排查和處理。

圖15:測試結(jié)構(gòu)圖片,右側(cè)為接地金屬層,左側(cè)為浮接到的大面積金屬層(來源:IEEE:在互連制造過程中防止工藝引起ESD損壞的設(shè)計解決方案)

靜電防護防護規(guī)則自動化檢查流程的建立,一方面使得靜電防護工程師免于人工檢查面對的巨大工作量,也使得集體經(jīng)驗?zāi)軌虻靡苑e累和傳承,使得產(chǎn)品質(zhì)量能夠以精確的量化數(shù)據(jù)來支撐。

總結(jié)

靜電防護設(shè)計在之前一直被認(rèn)為是半導(dǎo)體設(shè)計中的煉金術(shù)和黑魔法,高度依賴實踐的經(jīng)驗,但實際更需要扎實的理論支撐以及系統(tǒng)性的設(shè)計方法。大量的實際工藝器件的試驗數(shù)據(jù)仍然是重要的靜電防護設(shè)計基礎(chǔ);復(fù)雜的設(shè)計和需求使得靜電防護設(shè)計和模擬電路、硬件系統(tǒng)之間的聯(lián)合設(shè)計也越來越多,完善而先進的SoC靜電防護設(shè)計方法和流程使得SoC設(shè)計的各團隊能夠有明確的實現(xiàn)方法來保障芯片級及系統(tǒng)級的靜電防護能力;自動化檢查的方法和流程作為實際測試數(shù)據(jù)、團隊經(jīng)驗的總結(jié),使得芯片的靜電防護性能在Tapeout之前就具備扎實的設(shè)計理論數(shù)據(jù)作為支撐。

芯耀輝的靜電防護設(shè)計團隊擁有完整的靜電防護解決方案,結(jié)合靜電防護技術(shù)、自動化工具的檢查方法和流程、聯(lián)合設(shè)計的方法和流程,以保證芯片靜電防護的達標(biāo)。當(dāng)復(fù)雜度越來越高、速度越來越快的SoC設(shè)計給芯片設(shè)計帶來了巨大的挑戰(zhàn),芯耀輝已經(jīng)具備為客戶提供解決先進工藝下所涉及的各項挑戰(zhàn)的能力,用高質(zhì)量IP和完整的SoC前后端服務(wù),幫助合作伙伴加速SoC開發(fā),助力客戶SoC量產(chǎn)。

注釋

ESD(Electro-Static discharge)——靜電放電HBM( Human Body Model)——人體放電模式MM(Machine Model)——機器放電模式CDM(Charged Device Model)——充電放電模式GGNMOS(Gate Grounded NMOS)——柵極接地NMOSTLP(Transmission Line Plus)——傳輸線脈沖P2P(Point to Point Resistor)——點對點電阻CD(Current Density)——電流密度

原文標(biāo)題:面對高復(fù)雜性IP產(chǎn)品設(shè)計,如何保證達成靜電防護能力需求指標(biāo)?

文章出處:【微信公眾號:芯耀輝科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52115瀏覽量

435570 -

FinFET

+關(guān)注

關(guān)注

12文章

255瀏覽量

90917 -

靜電防護

+關(guān)注

關(guān)注

11文章

207瀏覽量

47823 -

芯耀輝

+關(guān)注

關(guān)注

3文章

44瀏覽量

10070

原文標(biāo)題:面對高復(fù)雜性IP產(chǎn)品設(shè)計,如何保證達成靜電防護能力需求指標(biāo)?

文章出處:【微信號:AkroStar-Tech,微信公眾號:芯耀輝科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

概倫電子芯片級HBM靜電防護分析平臺ESDi介紹

動力電池測試中的直流負載挑戰(zhàn)與應(yīng)對策略

軟件定義汽車(SDV)開發(fā)有哪些挑戰(zhàn)?SDV開發(fā)策略分享:福特汽車采用Jama Connect提升開發(fā)效率與質(zhì)量

軟件定義汽車(SDV)開發(fā)有哪些挑戰(zhàn)?SDV開發(fā)策略分享:福特汽車采用Jama Connect提升開發(fā)效率與質(zhì)量

芯片的失效性分析與應(yīng)對方法

變頻器的應(yīng)用誤區(qū)和弊端及應(yīng)對策略

物聯(lián)網(wǎng)精益轉(zhuǎn)型中的挑戰(zhàn)與應(yīng)對策略

海外HTTP安全挑戰(zhàn)與應(yīng)對策略

人工智能在精益轉(zhuǎn)型中的挑戰(zhàn)與應(yīng)對策略

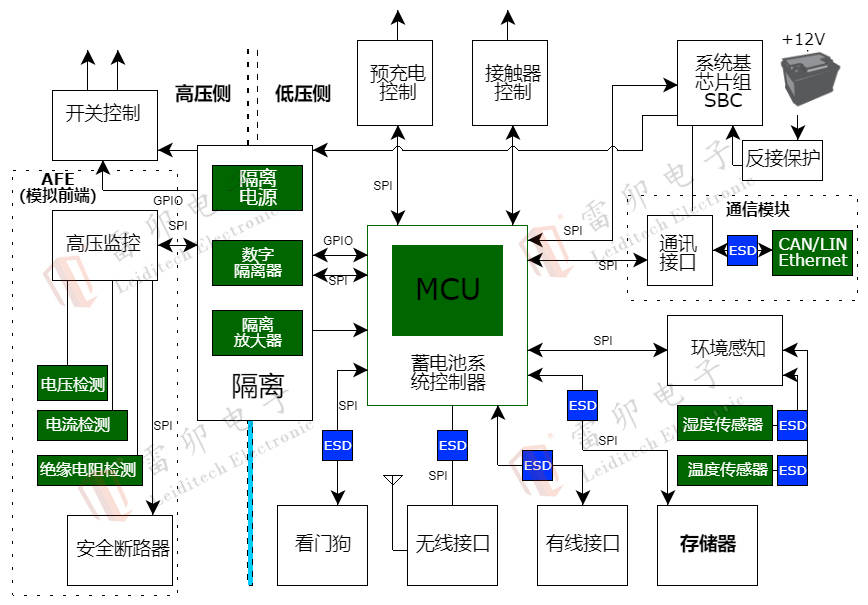

BMS系統(tǒng)中的靜電防護策略與實踐

BMS系統(tǒng)中的靜電防護策略與實踐

低觸發(fā)電壓可控硅結(jié)構(gòu)靜電防護器件

芯片級別靜電防護設(shè)計的挑戰(zhàn)及應(yīng)對策略

芯片級別靜電防護設(shè)計的挑戰(zhàn)及應(yīng)對策略

評論