不久前,我們剛對RISC-V的GPU生態(tài)進行了分析,也談及了目前的進展。雖然仍處于起跑狀態(tài),但越來越多的人開始意識到GPU是RISC-V的一塊短板,并決心打破這個僵局。畢竟GPU憑借圖形處理器能力以及在AI/ML應用上得天獨厚的優(yōu)勢,已經(jīng)讓其在部分領域擁有了超越CPU的趨勢。

而RISC-V想要在消費電子領域進入下一個階段,比如智能手機和個人電腦等,GPU是不得不跨過的難關。不過對Arm來說,通用GPU都還沒能做到高性能,即便是蘋果的M1系列芯片,也只是靠著媒體處理引擎和堆核心數(shù)提升一定性能而已。要想推動RISC-V的GPU生態(tài)發(fā)展,單靠廠商、院校與研究機構還不夠,RISC-V作為開源架構,也得利用好來自開源社區(qū)的力量。

RISC-V GPU再迎新玩家

近日,一個開源RISC-V項目引起了大家的注意,那就是VeriGPU。作者是來自人工智能呼叫中心自動化公司ASAPP的一名研究工程師Hugh Perkins。由于作者選用了Verilog這種硬件描述語言,想必這也是該項目名的來由了。

Hugh是一個資深的開發(fā)者了,擁有多年的機器學習和Python開發(fā)經(jīng)驗,從劍橋大學畢業(yè)的他選擇了來到中國繼續(xù)深造,最終在清華大學獲得了CS碩士學位。然而,在這個新項目上,他選擇了打造一款開源RISC-V GPU,專門面向機器學習,并計劃讓其支持PyTorch深度學習框架。

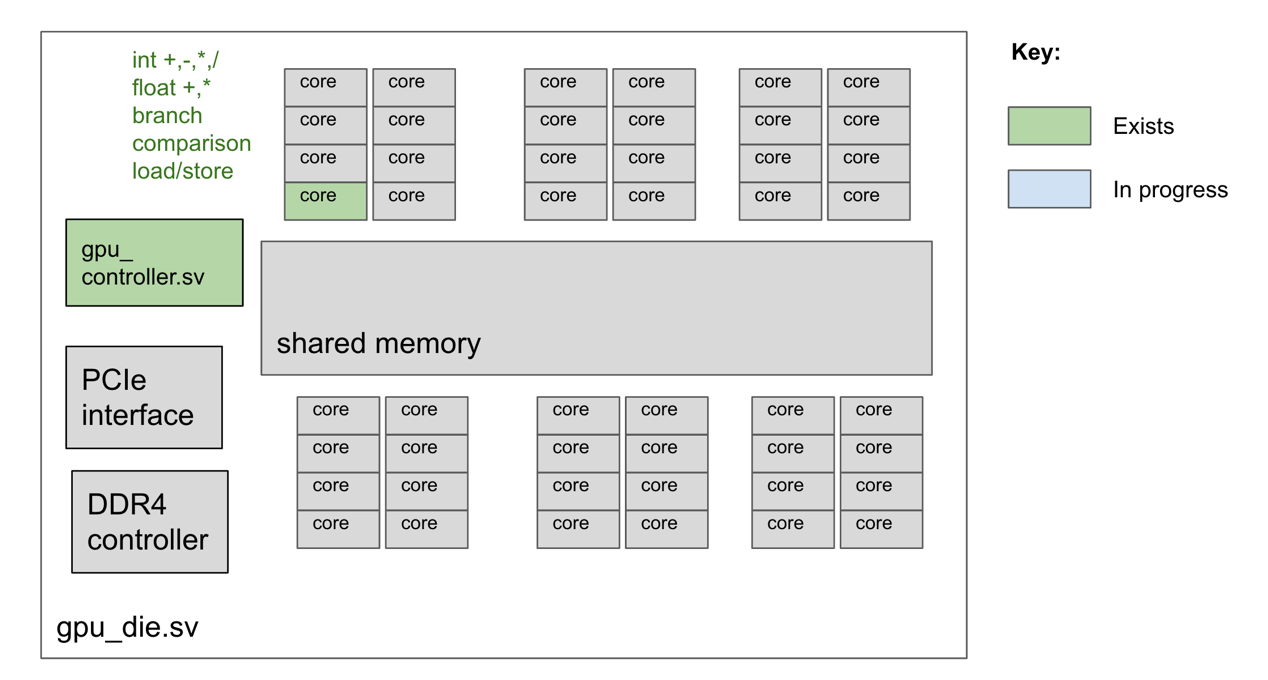

VeriGPU核心架構 / VeriGPU

為了兼容PyTorch,VeriGPU計劃利用去年剛獲得PyTorch官方支持的AMD HIP API,但VeriGPU也不排斥其他API,比如SYCL和英偉達的CUDA等。為了確保GPU核心專注于機器學習,VeriGPU像谷歌的TPU芯片一樣,全部選用了BF16浮點格式,如此一來也可以降低GPU核心裸片的面積,從而減少單個核心的成本。

而且VeriGPU也不打算采用亂序執(zhí)行,不僅是因為亂序執(zhí)行在單指令多線程(SIMT)下的復雜性,也因為這會使得GPU核心占用更多的面積,要么只能減少核心數(shù)量,要么就只能接受成本的增加了,所以VeriGPU還是選擇了輕量級的并行指令執(zhí)行。

值得一提的是,雖然是一款RISC-V GPU,VeriGPU內(nèi)部的GPU核心架構并不算完全遵守RISC-V ISA。Hugh表示當RISC-V與GPU設計出現(xiàn)沖突時,會選擇打破RISC-V的規(guī)范。這種情況會出現(xiàn)也不奇怪,畢竟RISC-V的擴展還在完善中,難以估計到所有用例。

開源下的流片問題

既然選用了Verilog,是否可以在FPGA實現(xiàn)原型,并利用FPGA已有的資源加速開發(fā)過程,并完成最終的流片呢?但我們在上文也提到了,這并非一個通用GPU,而是專門針對機器學習的GPU,作者也表示目標是ASIC流片。

更何況FPGA完成流片本身成本也不低,而且目前來看,若將FPGA只是用于訓練機器學習模型的話,在成本效益上不算優(yōu)秀。Hugh表示,他并不打算自己去做流片,但他會盡力驗證流片后的GPU是否時序無誤可以正常運作等等。

考慮到如果是個人開發(fā)的話,流片成本確實不可小覷,如果沒有公司、學校或研究機構的支持,一人完成流片可謂難于登天,至少大晶圓廠們通常不會浪費這個時間。這或許也是Hugh不選擇自己流片的原因,但開源項目的好處就在于,VeriGPU的流片工作可以交給那些愿意一試的參與者。

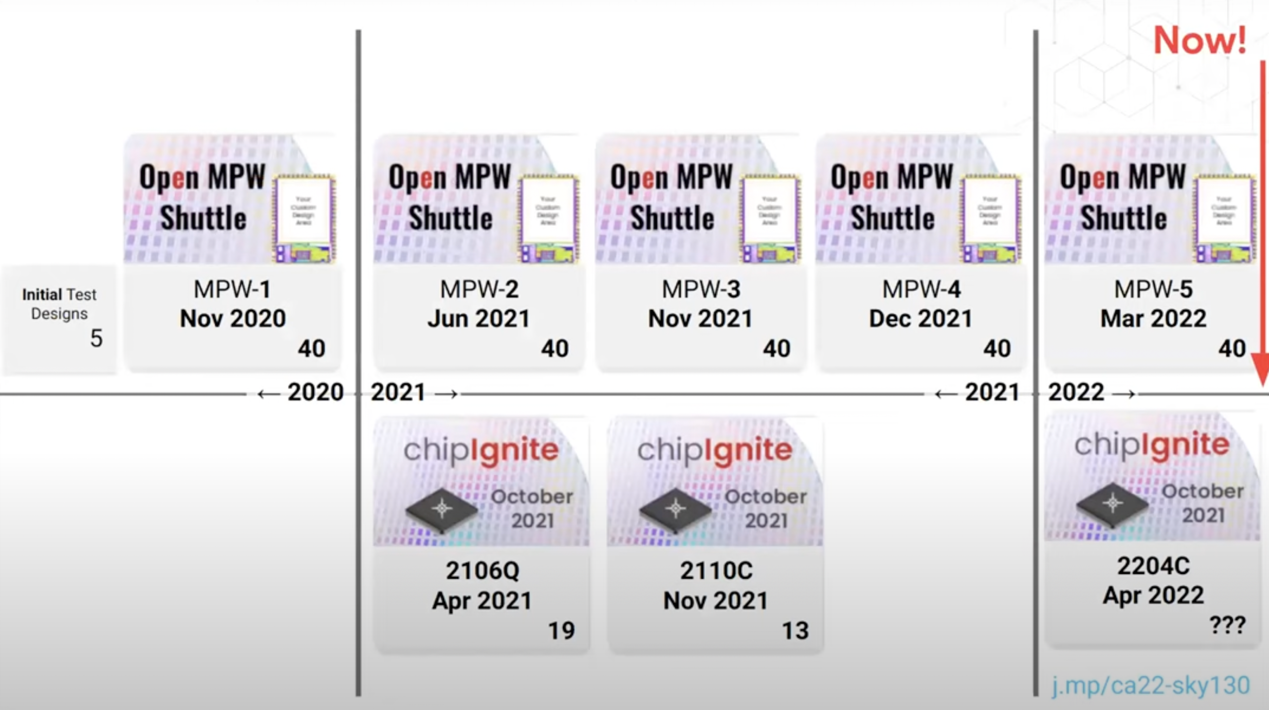

但開源項目的流片也并非總是如此困難,至少他們現(xiàn)在多出了新的選擇。在谷歌的出資下,SkyWater晶圓代工廠和眾包設計平臺Efabless推出了多項目晶圓(MPW)穿梭機項目。在不久前的芯片聯(lián)盟(ChipAlliance)半年度技術更新上,谷歌分享了該項目去年的進展。

去年MPW項目進行了3次項目征集,總提交設計數(shù)達到了200個以上,谷歌計劃今年繼續(xù)支持更多的設計,所以如果開源芯片開發(fā)者打算拿到自己設計的芯片,一定不要錯過這個“白嫖”谷歌的機會。

MPW穿梭機項目的進展 / 谷歌

這一計劃的推出對于開源芯片開發(fā)者來說可謂福音了,首先提供的PDK不僅可以直接用于生產(chǎn),而且是開源的,不需要簽署保密協(xié)議之類的合同或條約。而且在集成了部分開源工具鏈的情況下,工程師的開發(fā)流程將更加順暢。更不用說最重要的生產(chǎn)環(huán)節(jié)了,谷歌已經(jīng)為了這個項目自掏腰包,所以參與該項目無需花一分錢。

但對于開源GPU的開發(fā)而言,這可能也就是他們目前能做到的最大限度了。目前市面上的GPU都會選擇較為先進的工藝,而MPW只能提供130nm的工藝,所以在性能上肯定會大打折扣。驗證自己的設計,為硬件工程師提供更多實操的機會,這才是該項目的初衷。

-

處理器

+關注

關注

68文章

19813瀏覽量

233615 -

gpu

+關注

關注

28文章

4912瀏覽量

130681 -

RISC-V

+關注

關注

46文章

2502瀏覽量

48294

發(fā)布評論請先 登錄

FPGA與RISC-V淺談

SOPHGO RISC-V SoC Linux Kernel 社區(qū)郵件列表建立,歡迎加入開源社區(qū)為RISC-V生態(tài)完善添磚加瓦

關于RISC-V芯片的應用學習總結

關于RISC-V學習路線圖推薦

《RISC-V能否復制Linux 的成功?》

RISC-V,即將進入應用的爆發(fā)期

RISC-V近期市場情況調(diào)研

RISC-V擁有巨大市場潛力的原因

risc-v的發(fā)展歷史

rIsc-v的缺的是什么?

RISC-V在中國的發(fā)展機遇有哪些場景?

建設進展 | 全球首家 RISC-V 開源創(chuàng)新中心落地深圳

又一開源RISC-V GPU面世,流片或成最大問題

又一開源RISC-V GPU面世,流片或成最大問題

評論