本篇整理自Adam Taylor的設(shè)計(jì)教學(xué)博客。

在我寫的大多數(shù)博客里,都演示或解釋了FPGA/SoC的設(shè)計(jì)細(xì)節(jié)技術(shù)。但是這篇文章將有所不同,因?yàn)樵谶@里我要提出另外一個(gè)問(wèn)題。

你該如何開始做可編程邏輯設(shè)計(jì)的架構(gòu)?

在我有一次同時(shí)在為三個(gè)FPGA項(xiàng)目設(shè)計(jì)架構(gòu)(作為衛(wèi)星開發(fā)的一部分)時(shí),這個(gè)問(wèn)題浮現(xiàn)在我的腦海中。當(dāng)然,由于最終應(yīng)用場(chǎng)景的原因,該架構(gòu)受到了主承包商和航天局的多次審查。因此,我將盡可能詳細(xì)的畫出架構(gòu)圖,以便讓我的設(shè)計(jì)團(tuán)隊(duì)可以很輕松地從中進(jìn)行工作。

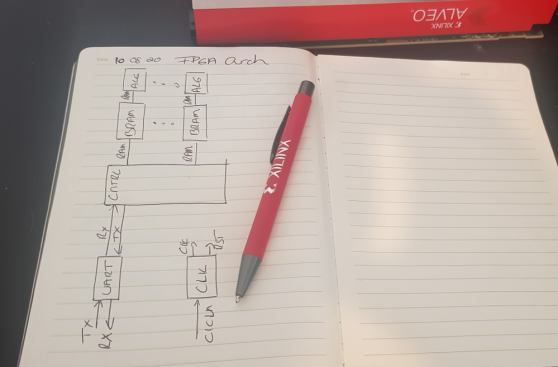

盡可能詳細(xì)地畫出架構(gòu)圖,在本子上就可以

可編程邏輯的架構(gòu)設(shè)計(jì)可能非常復(fù)雜,因此好的架構(gòu)通常要定義以下幾個(gè)元素:

1.模塊需要實(shí)現(xiàn)所需的功能,當(dāng)然,這些模塊也可以包含層次結(jié)構(gòu)。

2.每個(gè)模塊接收時(shí)鐘和時(shí)鐘使能,必須考慮如果信號(hào)跨越多個(gè)時(shí)鐘域時(shí)的跨時(shí)鐘域需求。

3.每個(gè)模塊收到的復(fù)位。就像時(shí)鐘一樣,必須考慮每個(gè)模塊的復(fù)位要求。

4.架構(gòu)中每個(gè)模塊接口信號(hào)相互連接

高效的架構(gòu)和實(shí)現(xiàn)應(yīng)盡可能利用供應(yīng)商的現(xiàn)有IP核。確定可以在整個(gè)體系結(jié)構(gòu)中重用的模塊也是明智的,例如控制算法或通信總線。我的設(shè)計(jì)中有3個(gè)FPGA需要構(gòu)建,因此識(shí)別可以通用的模塊將在開發(fā)和驗(yàn)證過(guò)程中節(jié)省大量時(shí)間。

接口重用十分劃算,因?yàn)樗菢?biāo)準(zhǔn)化模塊。使用標(biāo)準(zhǔn)接口(例如AXI,AXI Stream和APB)作為模塊接口,可以在多個(gè)設(shè)計(jì)中輕松復(fù)用。在我的這個(gè)項(xiàng)目中,可能不需要復(fù)用IP核,但在將來(lái)的開發(fā)中可能需要相同的功能。

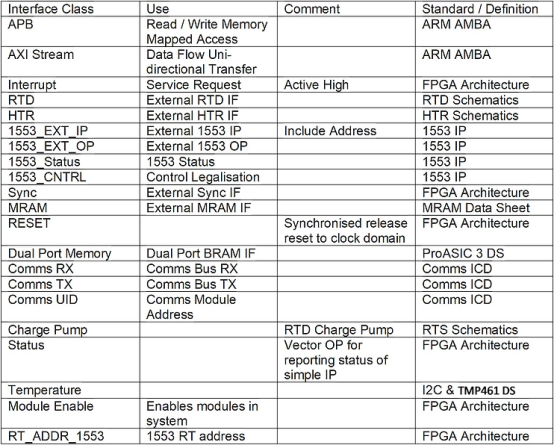

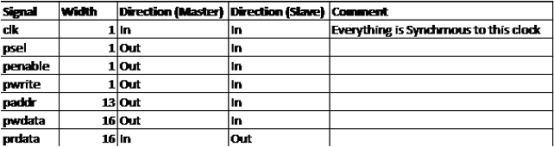

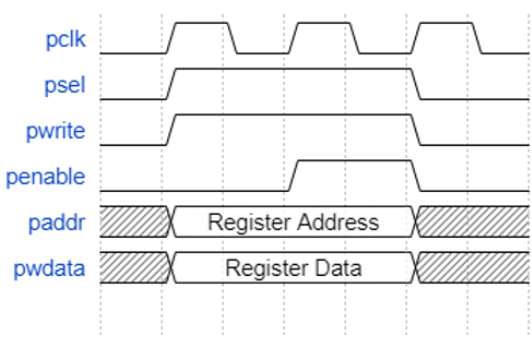

在我的復(fù)雜接口(如ADC/DAC接口、AXI或存儲(chǔ)接口)架構(gòu)圖中,我更喜歡使用一類接口類型,該類型包含所有較低級(jí)別的信號(hào)。然后可以在體系結(jié)構(gòu)文檔中定義接口類和所有信號(hào)。這種方法有幾個(gè)優(yōu)點(diǎn):它使架構(gòu)圖更簡(jiǎn)單,并使修改(例如 信號(hào)添加或重命名)只需要在一個(gè)位置進(jìn)行。

各種接口類型的定義

信號(hào)列表和時(shí)序圖

在創(chuàng)建架構(gòu)時(shí),我的傳統(tǒng)方法是從筆和紙開始,勾勒出主要的設(shè)計(jì)模塊和關(guān)鍵界面。完成此操作后,我將使用Visio將其電子圖形化,以使其添加在文檔中時(shí)看起來(lái)更加專業(yè)。

當(dāng)然,此圖需要顯示塊之間的所有信號(hào)和信號(hào)類別。理想情況下,工程師應(yīng)能夠拾取架構(gòu)和架構(gòu)文檔,并根據(jù)其角色開始開發(fā)或驗(yàn)證。

在研究架構(gòu)時(shí),我對(duì)其他工程師如何開發(fā)可編程邏輯架構(gòu)感到好奇,因此我在多個(gè)FPGA討論板/論壇上提出了問(wèn)題并收到了很多有趣的回答。大多數(shù)受訪者表示他們使用了常見的圖紙?jiān)O(shè)計(jì)套件,包括:

· Microsoft Visio (https://www.microsoft.com/en-gb/microsoft-365/visio/flowchart-software

· draw.io (https://app.diagrams.net/)

· yED (https://www.yworks.com/products/yed)

· Dia (http://dia-installer.de)

· OmniGraffle (https://www.omnigroup.com/omnigraffle)

· LibreOffice Draw (https://www.libreoffice.org/discover/draw/)

· Gliffy Diagrams for Confluence (https://marketplace.atlassian.com/apps/254/gliffy-diagrams-for-confluence)

· Lucidchart (https://www.lucidchart.com/)

· XMind (https://www.xmind.net/)

我們可以使用這里所有的繪圖包創(chuàng)建漂亮的架構(gòu)圖,有趣的是,有幾個(gè)人回答說(shuō)他們使用Symbolator,而我并不熟悉。

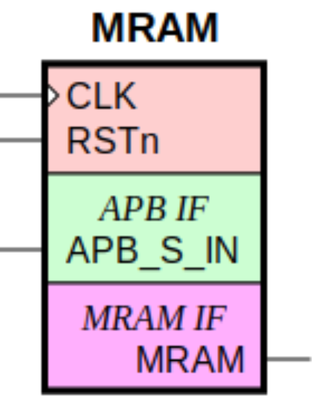

Symbolator是Windows和Linux中的命令行工具,它將讀取VHDL、Verilog和組件聲明然后生成組件圖。然后可以在您首選的圖紙包中使用這些symbol。

直接安裝Symbolator。我們可以使用pip進(jìn)行安裝,并注意您安裝的時(shí)候可能需要安裝一些其他軟件,包括Pycairo,PyGObject和Python-gi-cairo。完成此操作后,您可以使用各種不同格式和表示樣式的組件聲明創(chuàng)建組件symbol。

自從我學(xué)習(xí)到有關(guān)Symbolator的知識(shí)以來(lái),我感覺(jué)這工具還挺好用,于是決定將它用到我正在設(shè)計(jì)的三個(gè)架構(gòu)工作中。

用Symbolator進(jìn)行block設(shè)計(jì)

Symbolator的介紹地址:https://kevinpt.github.io/symbolator/

我非常喜歡使用清晰的時(shí)鐘和數(shù)據(jù)接口組定義來(lái)創(chuàng)建block。這一次,我使用Symbolator和Visio完成了架構(gòu)設(shè)計(jì),但對(duì)于各位架構(gòu)師來(lái)說(shuō),每個(gè)人都有每個(gè)人的習(xí)慣。大家更習(xí)慣如何開展FPGA/SoC架構(gòu)設(shè)計(jì)工作呢?

原文標(biāo)題:你一般如何做可編程邏輯設(shè)計(jì)的架構(gòu)?

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614263 -

soc

+關(guān)注

關(guān)注

38文章

4344瀏覽量

221745 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

526瀏覽量

44581

原文標(biāo)題:你一般如何做可編程邏輯設(shè)計(jì)的架構(gòu)?

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于直方圖算法進(jìn)行FPGA架構(gòu)設(shè)計(jì)

soc fpga架構(gòu)下的讀心術(shù)

【W(wǎng)EBENCH 大賽作品】WEBENCH FPGA 電源架構(gòu)設(shè)計(jì)

例說(shuō)FPGA連載15:硬件整體架構(gòu)設(shè)計(jì)

【設(shè)計(jì)技巧】FPGA架構(gòu)設(shè)計(jì)漫談

如何有效地開展FPGA/SoC架構(gòu)設(shè)計(jì)工作?

如何有效地開展FPGA/SoC架構(gòu)設(shè)計(jì)工作?

ARM推薦的SOC架構(gòu)設(shè)計(jì)是各自獨(dú)立復(fù)位?還是關(guān)聯(lián)同時(shí)復(fù)位?

ARM嵌入式應(yīng)用程序架構(gòu)設(shè)計(jì)工具-DLTools

ARM嵌入式應(yīng)用程序架構(gòu)設(shè)計(jì)工具-字庫(kù)

ARM嵌入式應(yīng)用程序架構(gòu)設(shè)計(jì)工具

基于ARMCortex_M3核的SoC架構(gòu)設(shè)計(jì)及性能分析

介紹WEBENCH 電源架構(gòu)設(shè)計(jì)工具使用方法與技巧

based SmartFusion2 SoC FPGA設(shè)計(jì)的System Builder設(shè)計(jì)工具

如何開展FPGA/SoC架構(gòu)設(shè)計(jì)工作?

如何開展FPGA/SoC架構(gòu)設(shè)計(jì)工作

如何開展FPGA/SoC架構(gòu)設(shè)計(jì)工作

評(píng)論