第二章 FPGA知識大串講02_知識串聯

作者:潘文明

本文為明德揚原創文章,轉載請注明出處!

在上一篇文章中,我們概括地講述了FPGA的一些學習誤區。本文我們將FPGA的關鍵知識串聯起來,系統地介紹各個知識點所處的層次和位置,為后面幾仿篇文章的詳細講解做好鋪墊。

第1節 FPGA的基本電路結構

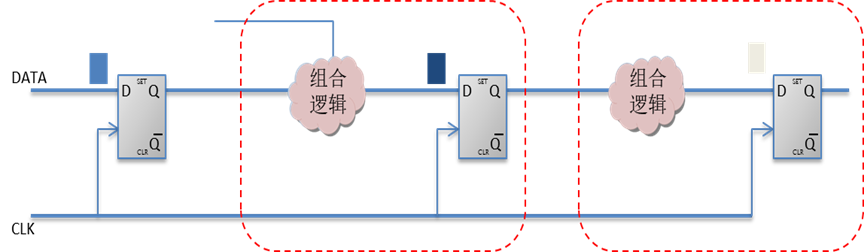

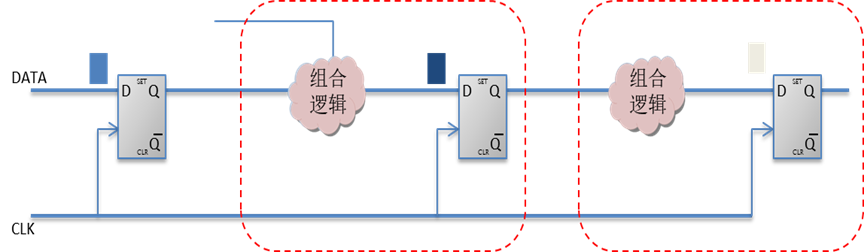

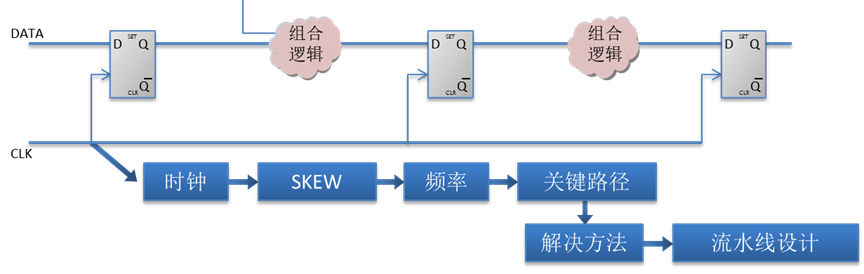

首先,我們來講解一下FPGA的基本電路結構。請看上圖中左邊紅色方框,該方框內包含了組合邏輯電路以及一個D觸發器。組合邏輯里可能是加法器、減法器、選擇器,甚至是什么都沒有,就是連線;組合邏輯的輸出將連接到D觸發器的輸入端;D觸發器在時鐘的驅動下,將組合邏輯的運算結構,輸出到D觸發器的輸出端。

這就是一個FPGA的基本電路結構,而這個電路結構則與VERILOG中的一個ALWAYS對應,如下面的代碼

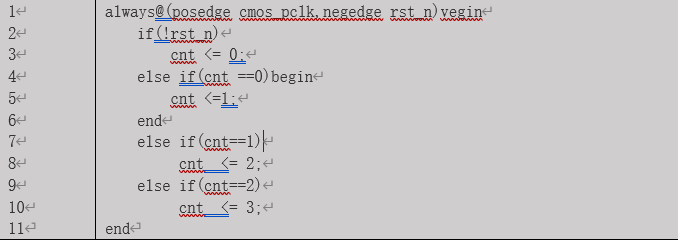

上面代碼在綜合器的作用下,其綜合的FPGA電路結構,也是組合邏輯+D觸發器的形式。其中組合邏輯由比較器(cnt==0、cnt==1、cnt==2就是比較器)、選擇器(從1、2、3或者保持不變中選擇)等組成;D觸發器的時鐘就是代碼中的clk,輸入則是組合邏輯的結果,輸出則是信號cnt。

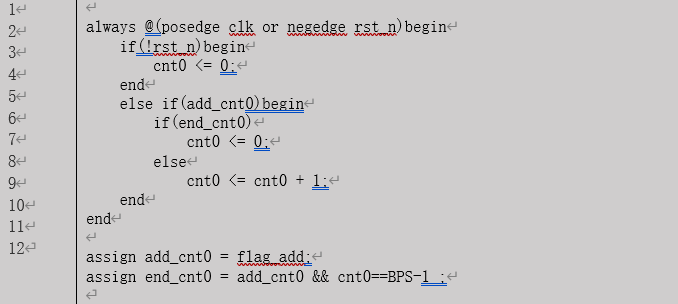

有讀者可能會對基本電路結構有疑問,難道所有代碼都這樣結構嗎?例如下面代碼中的add_cnt0和end_cnt0信號,它是由assign設計的,它們就沒有D觸發器。

單純只看add_cnt0和end_cnt0的代碼,貌似是沒有D觸發器,但仔細看第5行和第6行,這個兩個信號是參與了判斷(事實就是選擇器),決定了D觸發器的輸出cnt0。即從add_cnt0到cnt0之間,就是組合邏輯+D觸發器的結構。

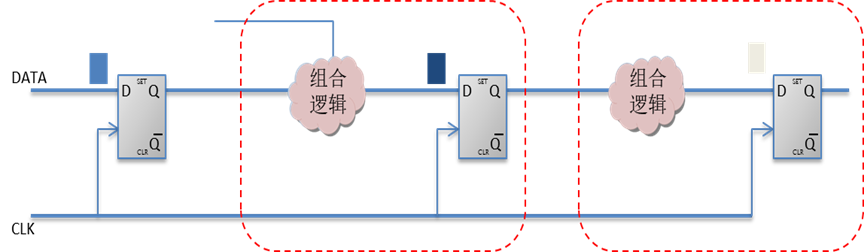

FPGA代碼是由一個又一個ALWAYS代碼組成的,這說明FPGA的絕大部分電路,就是由一個又一個“組合邏輯+D觸發器”的電路組合起來的,如下圖

上面這種結構是我們設計的基本單位。這種結構還有一種隱含的意思:組合邏輯決定電路的運算及功能,D觸發器就像一個節點,將運算結果保存下來,為下一級運算作準備。FPGA代碼設計過程,就像是設計一個功能,保存一下,設計下一個功能,保存一下。文字難以描述,請讀者認真體會體會。

還有注意的是,上面推薦的是“組合邏輯+D觸發器”結構思維,不要使用“D觸發器+組合邏輯”思維,這種思維是不正確的。

再看上圖,為什么說FPGA代碼里,各個ALWAYS是并行的呢?從上圖就很容易理解了。圖中可以看到,三個D觸發器都連接時鐘CLK。當時鐘CLK的上升沿的時候,這三個D觸發器將同時受到此信息,同時將D觸發器的輸入值給到輸出。這些電路都是同時工作的,不存在誰先誰后的。沒有所謂說這個電路在工作,另一個不在工作的情況。

這個就是FPGA 的基本電路結構,讀者務必做到非常清楚這個電路結構,這是我們后面描述的一個重要基礎。

第2節 FPGA的知識點

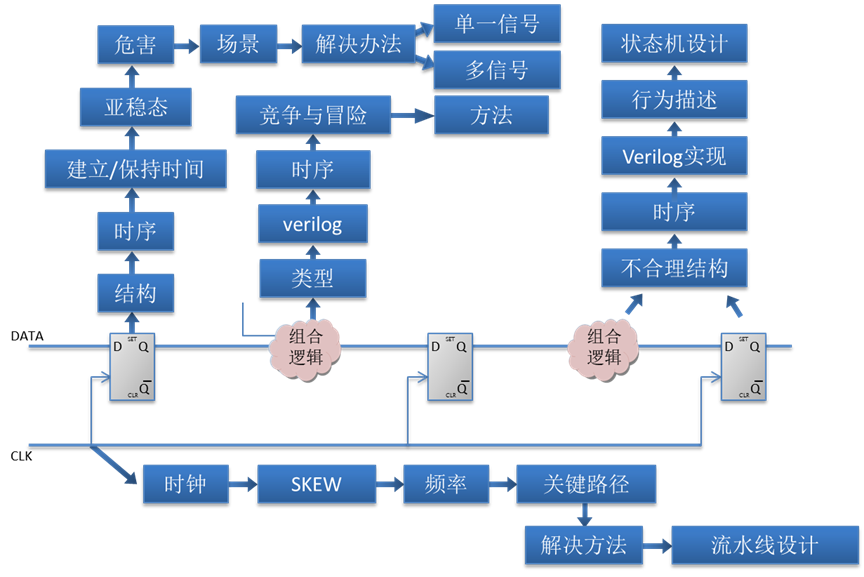

我們在FPGA基礎電路結構圖的基礎,將FPGA的所有知識點串聯起來,然后通過4篇文章,逐一進行詳細的講解。

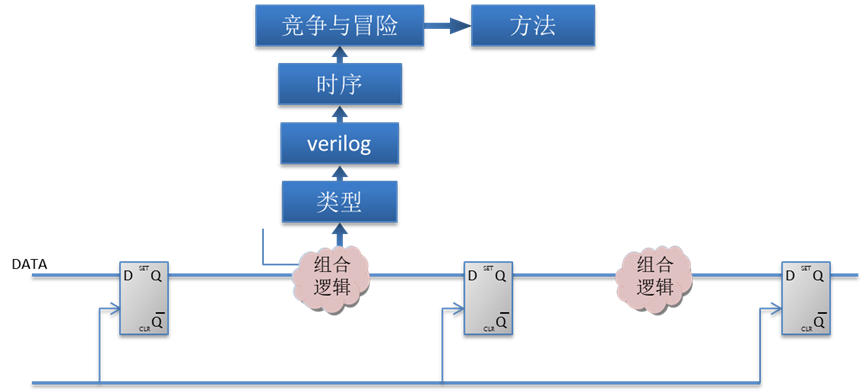

1. 先講述組合邏輯部分。組合邏輯是由加法器、減法器、比較器、選擇器等電路組成的,所以一開始我們要理解組合邏輯的電路有哪些類型;然后據此掌握這些類型的VERILOG代碼的寫法;接下來討論這些組合邏輯的時序,引出組合邏輯才有的競爭和冒險現象,最后提出競爭和冒險的解決方法。

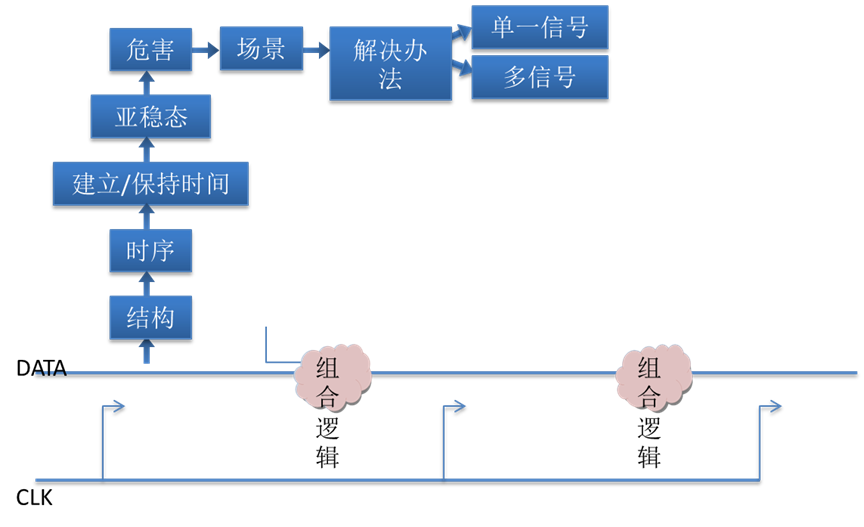

2. 完成組合邏輯的講述后,我們將討論D觸發器。首先會講解D觸發器的結構,進而會講述D觸發器的時序,討論D觸發器時序與組合邏輯的異同。從D觸發器時序中,有一個非常重要的概念:建立時間和保持時間。如果建立時間和保持時間不滿足,就會有一個叫亞穩態的情況。亞穩態有什么危害,亞穩態出現的場合有哪些。在明確了出現的場合后,就要想辦法解決亞穩態問題,提出了亞穩態的解決方法。其解決方法分兩種:一種是單一信號,也就是一比特信號的解決方法;還有一種是多比特信號的解決方法。

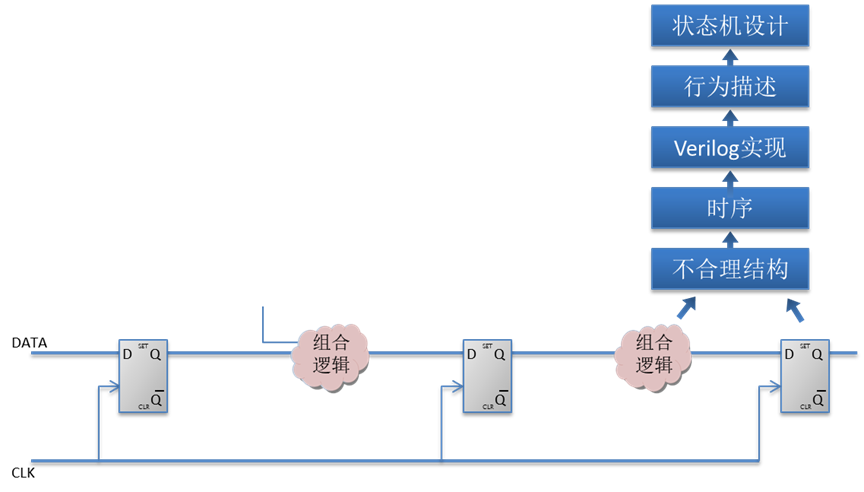

3. 講完了D觸發器之后,我們將把組合邏輯和D觸發器聯合起來。前面已經講魔神,組合邏輯+D觸發器是一個正確的的電路結構。有正確,那么就不正確,根據收集讀者的反饋情況,我們列出了一些經常會犯的、不合理的結構。之后將討論這個基本結構的時序;接下來是講述如何用VERILOG來實現。實現的話,就有行為描述以及狀態機的實現這幾種方法了。

4. 最后一部分,我們將單獨對時鐘進行講解。時鐘是FPGA的一個基礎,是一個很重要的概念,是FPGA設計的重點和難點。首先我們將講述時鐘的概念;然后是時鐘抖動SKEW和時鐘頻率。經常有被問到:我這個電腦CPU能跑1G,他那個電腦CPU能跑2G,這就是使用頻率。那這個頻率取決于什么因素,為什么有些跑得快,有些跑得慢?這個問題將引出關鍵路徑的概念。為了提高時鐘頻率,我們可以怎么做?流水線的設計!!!

以上就是我們FPGA 的所有知識點,將其展示到一張圖,方便讀者使用。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613898 -

電路

+關注

關注

173文章

6022瀏覽量

174374 -

結構

+關注

關注

1文章

117瀏覽量

21894

發布評論請先 登錄

FPGA芯片的概念和結構

放大器電路原理及放大器電路圖內容詳解

【國產FPGA入學必備】國產FPGA權威設計指南+配套FPGA圖像視頻教程

buck電路的組成元件詳解 buck電路與線性穩壓器的區別

FPGA復位的8種技巧

詳解FPGA的基本結構

FPGA與傳統DAC的比較

FPGA電路設計的一些技巧

一文了解FPGA比特流的內部結構

詳解FPGA的基本電路結構

詳解FPGA的基本電路結構

評論