在多個第三方IP核、外部接口和低功耗設計驅動下,數(shù)十億門級的專用集成電路(ASIC)已具備幾十甚至數(shù)百個異步時鐘域,而要解決跨時鐘域(CDC)問題,RTL仿真和靜態(tài)時序分析(STA)都不是最理想的解決方案。

對數(shù)字開發(fā)者而言,CDC問題主要源于以下四種常見的跨時鐘域場景。

如果沒有合適的時鐘同步器,由異步時鐘域之間的抖動引起的亞穩(wěn)態(tài)可能會導致功能故障。此外,設計中還存在更復雜的路徑和場景,例如多條同步后的路徑經過組合邏輯匯聚在一起可能會由于同步器的不確定性而導致時序不匹配。此類缺陷通常無法在流片前解決,因此出錯后可能會導致芯片設計返工,從而付出高昂的代價!

CDC驗證是流片前的關鍵簽核標準。那么要實現(xiàn)這一標準,ASIC開發(fā)團隊將會面臨哪些挑戰(zhàn)呢?

周轉時間

CDC違規(guī)清零是芯片簽核的必要條件。

解決CDC問題的難度與芯片的設計規(guī)模成正比。在數(shù)十億門級的ASIC設計中可能存在數(shù)百個異步時鐘和數(shù)百萬個跨異步路徑。開發(fā)者通常需要消耗萬億字節(jié)內存,并花費數(shù)天時間才能完成全芯片的扁平級CDC分析。在此過程中,周轉時間非常重要。

在進行CDC分析時,開發(fā)者們可采取自下而上的分層分析法,就像進行綜合和靜態(tài)時序分析那樣,每次分析一個模塊,逐個模塊解決CDC錯誤。在向上一個層級移動的過程中,開發(fā)者們可以用抽象的CDC模型替換CDC違例已經清理干凈的模塊。這一模型將只包含與上一層相關的時鐘路徑,而不考慮所有內部跨異步路徑,每清理完一個層級,就會繼續(xù)進行下一層級的CDC清理,以此類推。

通過這種方式,CDC分析可左移到開發(fā)流程的早期階段,而無需等到流片前才完成。如果在臨近流片時還在修復CDC錯誤,會對設計造成極大的破壞性,代價極其高昂!

新思科技VC SpyGlass CDC擁有CDC簽核以及層次化驗證流程,采用高效的分層方法,在不改變結果質量(QoR)的情況下,減少了內存需求,將周轉時間提高至少3倍。

誤報問題

CDC分析的另一個重大挑戰(zhàn)是誤報問題。

當設計中有數(shù)以百萬計的CDC跨異步路徑時,出現(xiàn)的違例數(shù)量也會非常龐大,那么要確定問題究竟出在哪就會如同大海撈針一般,非常困難,這就導致開發(fā)者可能會遺漏一些十分重要的CDC違例從而沒有進行bug修復。因此,對于大型ASIC開發(fā)者來說,CDC分析十分棘手。

幸運的是,數(shù)據(jù)科學為我們提供了解題思路──機器學習(ML)技術可以成為解決這一問題的關鍵。ML技術可以根據(jù)問題根源對違例行為進行分類,我們會發(fā)現(xiàn),很多違例行為都可以歸因為同一個問題,且歸類的前五大問題幾乎可以覆蓋95%以上的違例行為,只要解決這五大問題,就可以極大減少違例誤報,對開發(fā)者來說,發(fā)現(xiàn)并解決剩余5%的問題也將容易不少。

VC SpyGlass CDC通過采用ML技術對違例誤報執(zhí)行根本原因分析(RCA)來解決誤報問題。這種ML RCA方法不僅可以分門別類地識別違例,還可以通過調試線索提示根本原因,助力開發(fā)者高效找到解決方案。例如,由于缺少同步機制,開發(fā)者們可以通過更改RTL來糾錯,但更常規(guī)的做法是對CDC約束文件進行優(yōu)化或補充。這種約束優(yōu)化過程能夠快速迭代,大幅減少違例行為,并快速識別需要在設計中修復的真正的CDC問題。

約束是否正確

CDC分析是由約束驅動的,約束由開發(fā)者編寫,不正確的約束可能會導致不正確的CDC分析,比如約束錯誤可能會導致真正的CDC違例沒有被發(fā)現(xiàn),因此沒有被修復并最終導致流片失敗。當芯片設計中需要輸入約束文件(如新思科技設計約束(SDC)文件)時,檢查這些輸入文件的正確性至關重要。確保這些約束文件正確的方法之一是將約束轉化為斷言并把他們放到動態(tài)仿真環(huán)境里去驗證。這種方法將為開發(fā)者們提供更高級別的約束驗證。

豁免是否正確

除約束外,還可以運用違例豁免。豁免也是CDC分析工作流所需的輸入文件,通過分析手動生成。錯誤地運用豁免可能會導致CDC的真實錯誤被掩蓋。即使豁免最初是正確的,但為解決功能或性能問題,開發(fā)者也可能需要修改RTL或網(wǎng)表ECO。在這種情況下,開發(fā)者需要對豁免進行核查,因為之前有效的條件可能不再成立。

更困難的收斂問題

大多數(shù)CDC問題都可以進行靜態(tài)結構性分析,但在某些情況下動態(tài)分析也是有必要的,比如在設計中存在很復雜的匯聚問題,尤其是時序匯聚深度很深并且工具默認檢查深度不夠的話,就會遺漏這類問題。

所以比較好的解決辦法是使用亞穩(wěn)態(tài)注入進行仿真。VC SpyGlass CDC將生成亞穩(wěn)態(tài)模型的CDC數(shù)據(jù)庫,該數(shù)據(jù)庫將在仿真運行時動態(tài)注入隨機抖動。

新思科技的VCS仿真可在運行時進行本地數(shù)據(jù)庫讀取,新思科技的Verdi自動調試系統(tǒng)可以對故障進行調試,并對亞穩(wěn)態(tài)注入信號進行監(jiān)控,生成覆蓋率報告注入了多少次亞穩(wěn)態(tài)抖動。

處理第三方IP核

大多數(shù)數(shù)十億門級ASIC會集成多個第三方IP核,這些IP核可能提供了CDC約束,但沒有提供簽核CDC抽象模型。開發(fā)者們肯定不希望對所有IP核都進行扁平化CDC分析,因此開發(fā)者們可以針對IP生成其對應的SAM 抽象模型并把它集成到頂層的CDC驗證流程。

調試效率

與驗證一樣,調試工具的有效性也會極大地影響開發(fā)者的工作效率。以CDC調試為例,最有效的解決方案是將良好的圖形可視化與波形分析相結合。此外,熟悉的調試環(huán)境和在多個驗證平臺使用統(tǒng)一的調試工具對開發(fā)者來說也十分重要。新思科技的Verdi調試器能夠確保跨平臺一致性,提高CDC的調試效率。

如何處理MBIST

最后一個要考慮的問題是如何處理MBIST插入。

MBIST通常在產品開發(fā)生命周期要結束時完成,可能占最終設計總邏輯的3%左右。MBIST的插入可能會導致芯片設計中CDC跨異步路徑大幅增加。這一點在流片前的CDC簽核過程中一定不能忽略。開發(fā)者們可以先單獨對MBIST做CDC分析,清理CDC違例,之后再插入MBIST,從而減少設計迭代。

結 語

VC SpyGlass CDC是新思科技在Verification Continuum平臺上集成的靜態(tài)分析解決方案之一,可提供全面的CDC簽核方法,實現(xiàn)高效能、大容量和高調試效率。該方法原生地與VCS仿真工具等其他工具協(xié)同工作,并通過與Verdi調試器集成為開發(fā)者們提供高效的調試體驗。

原文標題:CDC驗證:數(shù)十億門級ASIC設計的最大挑戰(zhàn)之一

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52169瀏覽量

436123 -

集成電路

+關注

關注

5420文章

11947瀏覽量

367137 -

asic

+關注

關注

34文章

1242瀏覽量

121984

原文標題:CDC驗證:數(shù)十億門級ASIC設計的最大挑戰(zhàn)之一

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

如何用AN75779實現(xiàn)CDC通信?

智慧路燈的推廣面臨哪些挑戰(zhàn)?

英偉達組建ASIC團隊,挖掘臺灣設計服務人才

蘋果無邊框OLED iPhone開發(fā)面臨挑戰(zhàn)

機器視覺要面臨的挑戰(zhàn)及其解決方法

需求管理工具Jama Connect:與Jira/Slack/GitHub無縫集成,一站式解決復雜產品開發(fā)中的協(xié)作難題

快速部署原型驗證:從子卡到調試的全方位優(yōu)化

【?嵌入式機電一體化系統(tǒng)設計與實現(xiàn)?閱讀體驗】+磁力輸送機系統(tǒng)設計的創(chuàng)新與挑戰(zhàn)

康謀分享 | 在基于場景的AD/ADAS驗證過程中,識別挑戰(zhàn)性場景!

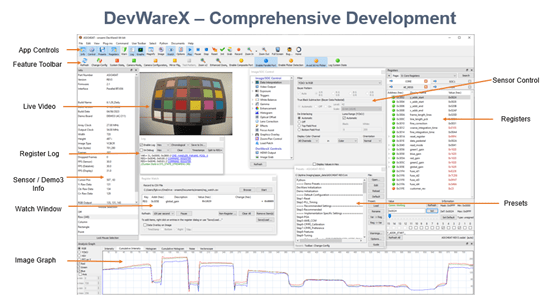

安森美圖像傳感器開發(fā)工具DevWareX介紹

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務!

請問如何安裝Espressif CDC Device驅動?

如何實現(xiàn)ESP32-S2 CDC與PC端的通信?

ESP32-C3調試USB CDC-ACM,不希望putchar后邊必須跟上換行符\"n\",要怎么實現(xiàn)?

大規(guī)模 SoC 原型驗證面臨哪些技術挑戰(zhàn)?

要實現(xiàn)CDC驗證標準,ASIC開發(fā)團隊將會面臨哪些挑戰(zhàn)

要實現(xiàn)CDC驗證標準,ASIC開發(fā)團隊將會面臨哪些挑戰(zhàn)

評論