1. 接口約束類型

2. Tready或Tvalid不連續問題

修改代碼,使綜合后的啟動時間間隔為1;

3. 兩個HLS IP核不能之間數據流對接不上

3.1 問題描述

前提:各個IP核的初始化和配置過程確認正確。

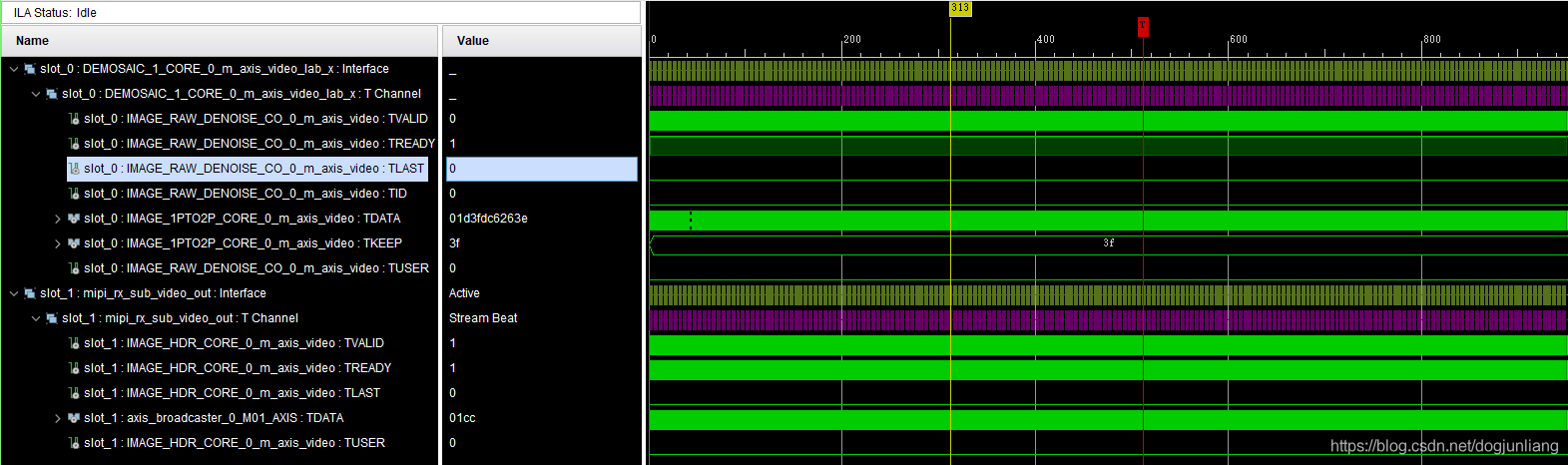

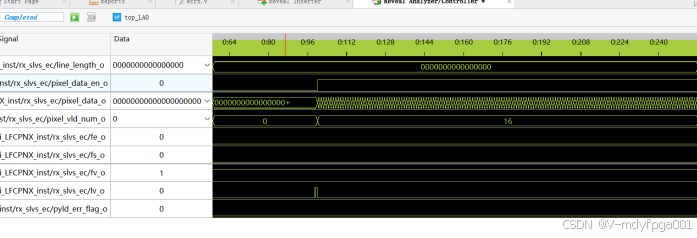

單獨添加一個自定義HLS IP核,IP核的master axistream端口的輸入Tready全部置1,上板測試后,DEMOSAIC_1_CORE_0的輸出總線上是有正常的數據數據流,如圖2所示:

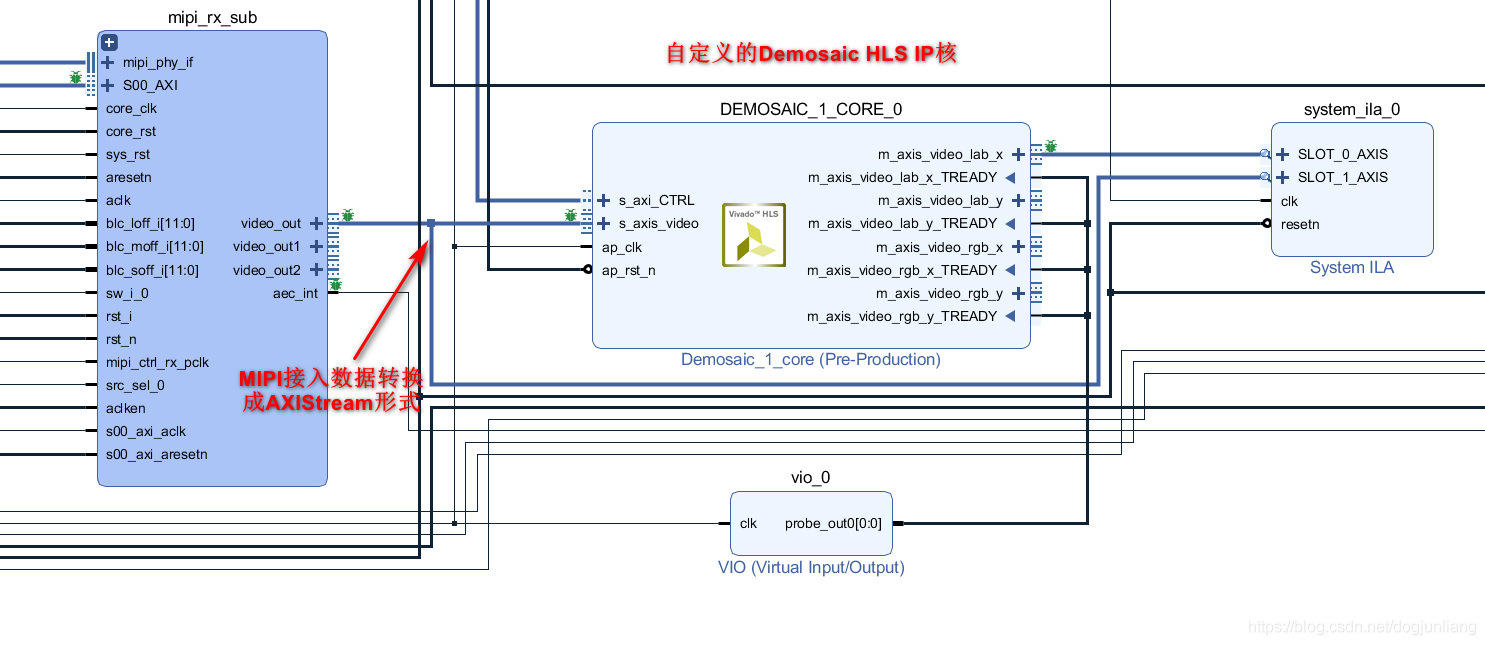

圖1 添加HLS DEMOSAIC1 IP核電路連接

圖2 添加HLS DEMOSAIC1 IP核板級波形

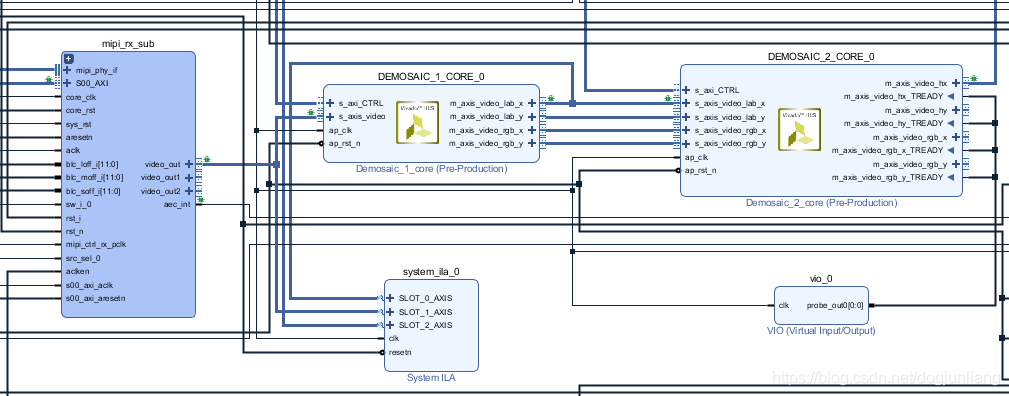

在上述平臺上接入自定義HLS IP核DEMOSAIC_2_CORE,DEMOSAIC_2_CORE的MASTER端口Tready輸入全部拉高,以便有效數據可以一直輸出,硬件電路如下:

圖3 添加HLS DEMOSAIC2 IP核電路連接

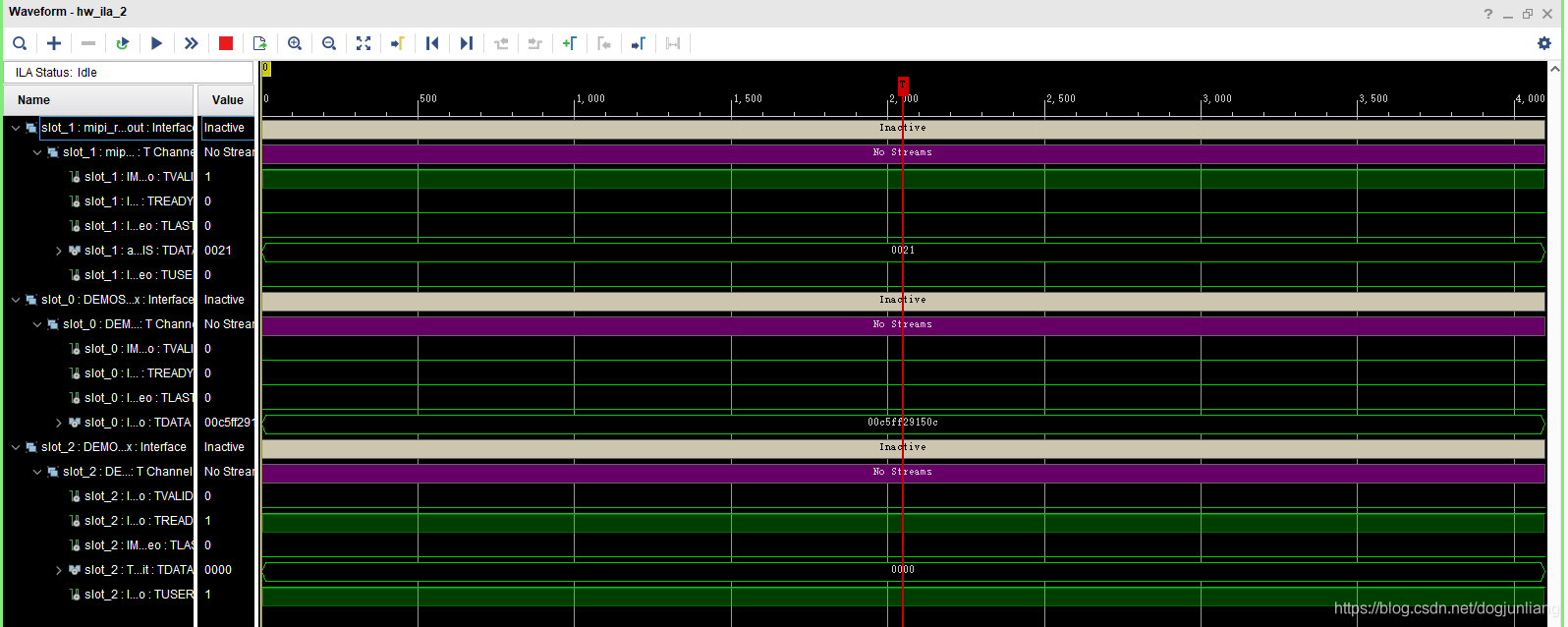

圖4 添加HLS DEMOSAIC2 IP核板級波形

3.2 解決方法

UG902 214頁,增加RTL FIFO深度,對輸出的hls::Stream類型的數據進行約束,約束成Stream類型FIFO的深度選擇合適。具體為什么要這樣操作,本人目前還未找到原因,有想法的歡迎留言!!!

4. AXIStream與Video類型接口之間的轉換

4.1 問題描述

兩個AXIStream接口類型的IP核之間有時候需要加入一個Video(具有HS\VS)接口的IP核,這就需要將AXIStream類型的數據轉換為Video類型,通過Video接口的IP核之后,又要將Video接口轉換為AXIStream,以下是其中一種解決方案。

4.2 解決方案

AXIStream類型的數據流時鐘大于PCLK;

AXIStream to Video IP核選擇異步模式,FIFO的深度為8192;

Video to AXIStream IP核選擇異步模式,FIFO的深度為8192;

VTC的FULL FRAME的W和H要配置、ACTIVE的W和H要和輸入Video的格式相同,否則AXIStream to Video IP無法鎖定。

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8918瀏覽量

153134 -

配置

+關注

關注

1文章

190瀏覽量

18776 -

HLS

+關注

關注

1文章

131瀏覽量

24618

發布評論請先 登錄

NVMe控制器IP設計之接口轉換

一文詳解Video In to AXI4-Stream IP核

AXI 接口設計避坑指南:AXI接口筆記

ALINX發布100G以太網UDP/IP協議棧IP核

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

AMBA AXI4接口協議概述

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

一種在HLS中插入HDL代碼的方式

HLS IP核AXI Stream接口問題匯總

HLS IP核AXI Stream接口問題匯總

評論