1、為什么要設(shè)計(jì)復(fù)位?

首先回想一下,在平常的設(shè)計(jì)中我們是不是經(jīng)常采用同步復(fù)位或者異步復(fù)位的寫法,這一寫法似乎都已經(jīng)形成了肌肉記憶----每次我們寫always塊的時(shí)候總是會(huì)對(duì)所有的寄存器寫一個(gè)復(fù)位賦初值的語句。

這樣設(shè)計(jì)的目的是什么?似乎是為了給寄存器一個(gè)初值,避免仿真不定態(tài)或初始化操作錯(cuò)誤。又似乎是為了在調(diào)試時(shí)能方便地使用按鍵進(jìn)行復(fù)位(最常用的全局復(fù)位)。這么一看復(fù)位似乎是蠻重要的。

2、復(fù)位是否有必要?

似乎在平常的設(shè)計(jì)中,多數(shù)會(huì)使用異步復(fù)位的方式,異步復(fù)位由于是異步信號(hào),所以不可避免地引入了亞穩(wěn)態(tài)的可能,這一可能性隨著時(shí)鐘頻率的提高而增加。好像在平常的設(shè)計(jì)與使用中,異步復(fù)位電路也不會(huì)引發(fā)什么問題。這是因?yàn)殡S著器件工藝的提升,現(xiàn)在器件的上升時(shí)間在0.0x 納秒級(jí),而一般設(shè)計(jì)的時(shí)鐘周期可能在100~200M。只要復(fù)位的釋放不是剛好在這0.0x 納秒內(nèi)就不會(huì)引發(fā)亞問題問題,顯然這個(gè)概率極小(比例--0.0x:10),基本可以說是99.99不會(huì)有問題。但是著名的墨菲定律高速我們:再小概率的事情都會(huì)發(fā)生。所以不管怎樣這種事情我們都應(yīng)該要想辦法避免。

再來看我們使用復(fù)位的主要目的:為了給寄存器一個(gè)初始值,從而避免仿真或使用錯(cuò)誤。然而實(shí)際上,Xilinx的FPGA的內(nèi)部資源(觸發(fā)器和RAM)等都會(huì)在上電后默認(rèn)賦初值,一般是0,或者可以在定義寄存器時(shí)手動(dòng)賦值,如:

reg [1:0] test = 2'b01; //定義時(shí)即賦初值

這么看的話僅僅為了賦初值而存在的賦值就沒有意義的。數(shù)據(jù)鏈路上有初值就夠了,因?yàn)楹髞淼臄?shù)據(jù)總會(huì)沖走之前的數(shù)據(jù),數(shù)據(jù)仍然能穩(wěn)步傳遞。但是控制鏈路就一定需要被復(fù)位后一定要恢復(fù)到初始狀態(tài),不然會(huì)“亂跑‘從而導(dǎo)致代碼運(yùn)行異常。其中最經(jīng)典的例子就是狀態(tài)機(jī)了,顯然,如果狀態(tài)機(jī)的狀態(tài)模塊沒有復(fù)位的話,那么可能在出現(xiàn)異常后永遠(yuǎn)無法恢復(fù)到正常狀態(tài)了。

最后,復(fù)位所使用的資源遠(yuǎn)超你的想象:

3、應(yīng)該怎樣設(shè)計(jì)復(fù)位?

說了這么多,那到底要怎么設(shè)計(jì)復(fù)位?

同步or異步?

在一文中探討過同步復(fù)位與異步復(fù)位的特點(diǎn)。

同步復(fù)位:

有利于仿真

由于只在時(shí)鐘有效電平到來時(shí)才有效,所以可以濾除高于時(shí)鐘頻率的復(fù)位毛刺,沒有亞穩(wěn)態(tài)問題

可以使所設(shè)計(jì)的系統(tǒng)成為 100%的同步時(shí)序電路,有利于時(shí)序分析

復(fù)位信號(hào)的有效時(shí)長必須大于時(shí)鐘周期,才能真正被系統(tǒng)識(shí)別并完成復(fù)位任務(wù)。同時(shí)還要考慮延時(shí)因素

大多數(shù)的FPGA的DFF都只有異步復(fù)位端口,采用同步復(fù)位的話,綜合器就會(huì)在寄存器的數(shù)據(jù)輸入端口插入組合邏輯,這樣會(huì)耗費(fèi)邏輯資源

異步復(fù)位

大多數(shù)目標(biāo)器件庫的dff都有異步復(fù)位端口,因此采用異步復(fù)位可以節(jié)省資源

設(shè)計(jì)相對(duì)簡(jiǎn)單,異步復(fù)位信號(hào)識(shí)別方便,而且可以很方便的使用FPGA的全局復(fù)位端口GSR

復(fù)位信號(hào)容易受到毛刺的影響且容易存在亞穩(wěn)態(tài)問題

建議使用同步復(fù)位的方式,若一定要使用異步復(fù)位的話,則建議使用異步復(fù)位、同步釋放的方法。

高or低?

選擇高還是低,需要根據(jù)具體的電平標(biāo)準(zhǔn)、器件結(jié)構(gòu)來選擇,并不是一概而論低電平有效的好或者高電平有效的好。簡(jiǎn)單經(jīng)驗(yàn):Altera的用低電平復(fù)位,Xilinx的用高電平復(fù)位。

總結(jié)

復(fù)位信號(hào)能不用就不要用,需要特定初值的可以在定義寄存器時(shí)賦值

如果一定需要?jiǎng)t使用異步復(fù)位、同步釋放的方法,并將復(fù)位信號(hào)局部化,避免高扇出。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21952瀏覽量

613787 -

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124284 -

復(fù)位

+關(guān)注

關(guān)注

0文章

179瀏覽量

24551

發(fā)布評(píng)論請(qǐng)先 登錄

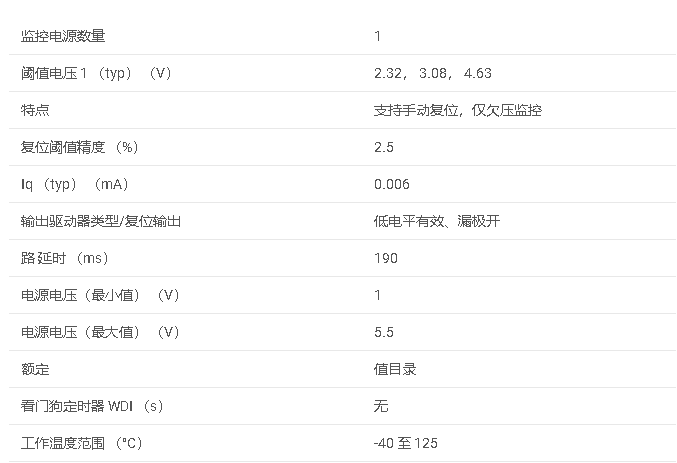

LM3724系列 低功率電壓監(jiān)控和復(fù)位IC,帶手動(dòng)復(fù)位功能數(shù)據(jù)手冊(cè)

復(fù)位電路的作用、控制方式和類型

做APPSFPGA的vhdl源碼,fpga如何修改pgen送數(shù)據(jù)到數(shù)據(jù)總線然后復(fù)位?

FPGA復(fù)位的8種技巧

復(fù)位電路的設(shè)計(jì)問題

復(fù)位電路的三種方式 復(fù)位電路的原理和作用

復(fù)位電路的電容多大的 復(fù)位電路設(shè)計(jì)類型有哪幾種

復(fù)位電路靜電整改案例分享(一)——交換機(jī)復(fù)位電路

淺談FPGA的復(fù)位設(shè)計(jì)問題

淺談FPGA的復(fù)位設(shè)計(jì)問題

評(píng)論