以太網PHY是什么?

從硬件上來說,一般PHY芯片為模數混合電路,負責接收電、光這類模擬信號,經過解調和A/D轉換后通過MII接口將信號交給MAC芯片進行處理。一般MAC芯片為純數字電路。

物理層定義了數據傳送與接收所需要的電與光信號、線路狀態、時鐘基準、數據編碼和電路等,并向數據鏈路層設備提供標準接口。物理層的芯片稱之為PHY。

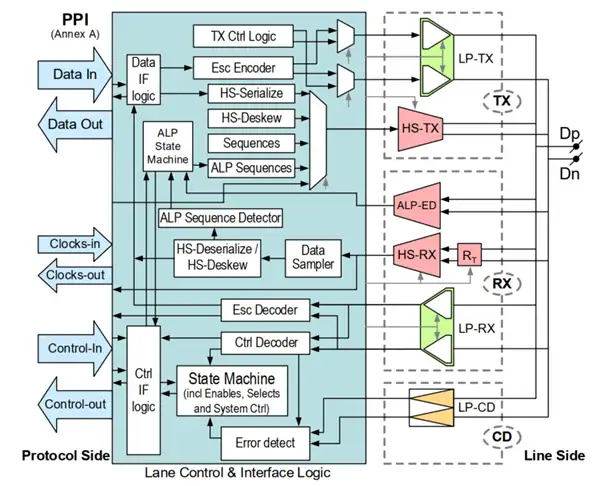

PHY是物理接口收發器,它實現物理層.IEEE-802.3標準定義了以太網PHY.包括MII/GMII(介質獨立接口)子層,PCS(物理編碼子層),PMA(物理介質附加)子層,PMD(物理介質相關)子層,MDI子層。它符合IEEE-802.3k中用于10BaseT(第14條)和100BaseTX(第24條和第25條)的規范。

PHY在發送數據的時候,收到MAC過來的數據(對PHY來說,沒有幀的概念,對它來說,都是數據而不管什么地址,數據還是CRC.對于100BaseTX因為使用4B/5B編碼,每4bit就增加1bit的檢錯碼),然后把并行數據轉化為串行流數據,再按照物理層的編碼規則把數據編碼,再變為模擬信號把數據送出去。

收數據時的流程反之.PHY還有個重要的功能就是實現CSMA/CD的部分功能。它可以檢測到網絡上是否有數據在傳送,如果有數據在傳送中就等待,一旦檢測到網絡空閑,再等待一個隨機時間后將送數據出去。

如果兩個碰巧同時送出了數據,那樣必將造成沖突,這時候,沖突檢測機構可以檢測到沖突,然后各等待一個隨機的時間重新發送數據。

這個隨機時間很有講究的,并不是一個常數,在不同的時刻計算出來的隨機時間都是不同的,而且有多重算法來應付出現概率很低的同兩臺主機之間的第二次沖突。

關于phy芯片 以RTL8211E(G)為例

PHY是IEEE802.3中定義的一個標準模塊,STA(station management entity,管理實體,一般為MAC或CPU)

通過SMI(Serial Manage Interface)對PHY的行為、狀態進行管理和控制,而具體管理和控制動作是通過讀寫PHY內部的寄存器實現的。

PHY寄存器的地址空間為5位,從0到31最多可以定義32個寄存器

所討論的RTL8211EG地址位是由001 - 111,由硬件配置,不同phy芯片配置有所不同,詳細需要閱讀芯片手冊

CSDN,博客園,凡有等待就有啟程綜合整理

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52091瀏覽量

435418 -

收發器

+關注

關注

10文章

3594瀏覽量

107293 -

PHY

+關注

關注

2文章

313瀏覽量

52455

發布評論請先 登錄

PHY芯片與網絡變壓器接線設計指南——不同速率與接口的硬件設計原則

AMD助力打造MIPI C-PHY/D-PHY測試方案

T2081 VSC8572 phy:Ping不起作用的原因?

Valens聯合七家MIPI A-PHY芯片廠商完成互操作性測試,加速中國及全球MIPI A-PHY生態發展

軟件在芯片設計中有什么作用

芯片的作用

使用FPGA的LVDS_serdes模式驅動DP83867E,可以不使用PHY芯片上自帶的SGMII_SCO(625MHz)的時鐘嗎?

是德科技承辦MIPI A-PHY芯片互聯互通測試周

D3 Embedded推出基于Valens VA7000 MIPI A-PHY芯片組的攝像頭模組

X1G004481000300低功耗晶振以太網PHY芯片的關鍵核心

聚焦MIPI 系列之四:一文盤點D-PHY/C-PHY/M-PHY之架構與測試解決方案

解讀MIPI A-PHY與車載Serdes芯片技術與測試

phy芯片的作用

phy芯片的作用

評論