FPGA方案

隨著一款產(chǎn)品在研發(fā)階段的日漸成熟,實現(xiàn)的功能也日趨復雜化和多樣化,對產(chǎn)品功能實現(xiàn)重定義的應用需求也在日益加大。產(chǎn)品功能重定義就是在不改動設備硬件設計的前提下,通過更改FPGA的程序文件,達到產(chǎn)品功能重定義的方法。

一般的產(chǎn)品在設計時,研發(fā)會按照產(chǎn)品的定義完成功能代碼的開發(fā),然后用JTAG接口進行燒錄、調(diào)試,但是等產(chǎn)品上線時,所有的固件就會被固化,并且因為JTAG接口過于笨重,我們一般是不保留該接口;所以也無法在產(chǎn)品完成固化后進行重新燒錄進行重定義的操作。

目前也有一些應用方案會使用BLE/WIFI SOC+存儲芯片的架構(gòu),BLE/WIFI SOC負責存儲芯片的讀寫,存儲芯片作為FPGA的程序代碼存儲器,工作時,BLE/WIFI SOC將存儲芯片中的數(shù)據(jù)讀出,并按照特定時序(FPGA加載時序)發(fā)送到FPGA,此過程即為FPGA的數(shù)據(jù)加載流程,如果需要升級功能,通過無線進行遠程OTA升級。而本方案是無需其它芯片參與的情況下通過邏輯設計和UART口進行產(chǎn)品功能的重定義。

邏輯設計

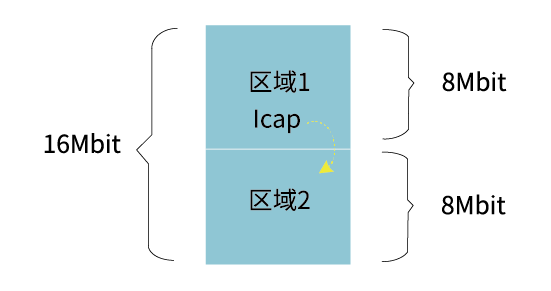

本方案的核心就是雙啟動,其中區(qū)域1為固化區(qū)域,此區(qū)域非功能區(qū)域,而是負責區(qū)域2的管理,其中區(qū)域2為功能區(qū)域,每次的功能重定義就是對區(qū)域2的刷新。區(qū)域2的刷新通過PC和串口調(diào)試助手模擬上位機,傳輸工程的 Bin文件到 fpga啟動配置的 Flash中,實現(xiàn)兩個存儲到 flash程序的跳轉(zhuǎn)完成固件升級操作。

設置兩個區(qū)域,第一個區(qū)域執(zhí)行程序1,完成對區(qū)域2的管理和升級工作。第二個區(qū)域的程序2是我們用戶設計的功能程序或者說產(chǎn)品程序。在 FPGA啟動中,如果我們不升級區(qū)域 2的程序,那么自動通過 ICap接口跳轉(zhuǎn)到區(qū)域2的程序中。區(qū)域1起始地址 0x0,區(qū)域2起始地址 0x0100000。

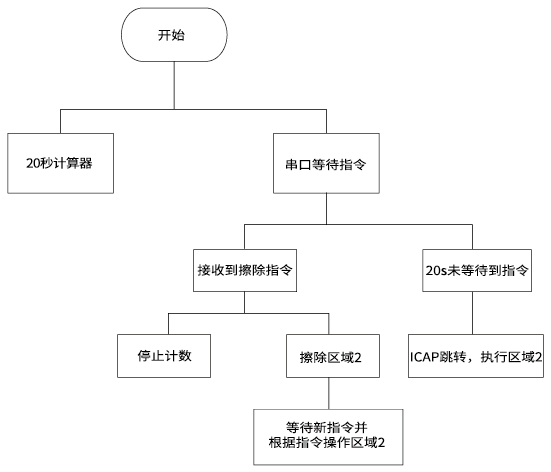

在本方案中,設計區(qū)域1的程序?qū)崿F(xiàn)的功能為:上電后自動加載此程序,此時開始計時如果 20秒內(nèi)沒有檢測到串口發(fā)送的擦除指令,那么我們啟動 icap跳轉(zhuǎn),跳轉(zhuǎn)到區(qū)域 2程序中。

如果希望再次升級的話必須重新給板卡上電使得程序回到區(qū)域1中。

流程圖如下:

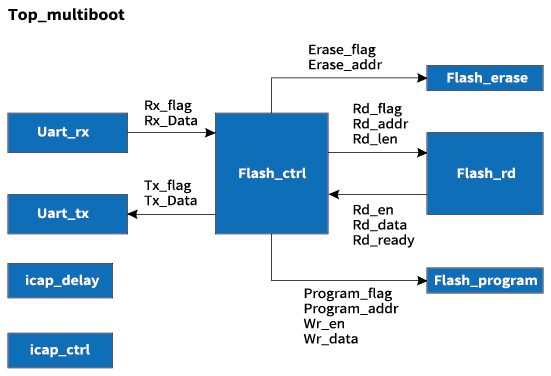

頂層結(jié)構(gòu)圖如下:

FPGA uart接收模塊,接收上位機發(fā)送的數(shù)據(jù),并實現(xiàn)波特率為115200的uart協(xié)議的串行數(shù)據(jù)到并行數(shù)據(jù)的轉(zhuǎn)換,將數(shù)據(jù)發(fā)送至flash_ctrl模塊,F(xiàn)lash_ctrl模塊是flash的控制模塊,該模塊自定義了一個簡單的協(xié)議,根據(jù)uart指令來控制flash的擦除、讀、寫,協(xié)議包括三種數(shù)據(jù)包來對應相應的指令,再將數(shù)據(jù)發(fā)送至對應的模塊;而由flash擦除、讀、寫三個模塊處理的數(shù)據(jù)返回后經(jīng)過uart_tx模塊返回上位機,本文中即返回PC機串口模塊。

編輯:YYX

-

芯片

+關注

關注

459文章

52181瀏覽量

436173 -

上位機

+關注

關注

27文章

960瀏覽量

55587

發(fā)布評論請先 登錄

百靈鳥電路的設計方案

FPGA設計大賽設計方案提交規(guī)則和截止時間須知

多種EDA工具的FPGA設計方案

基于CPLD/FPGA的多串口擴展設計方案

基于FPGA的百變設計方案分享

基于FPGA的百變設計方案分享

評論