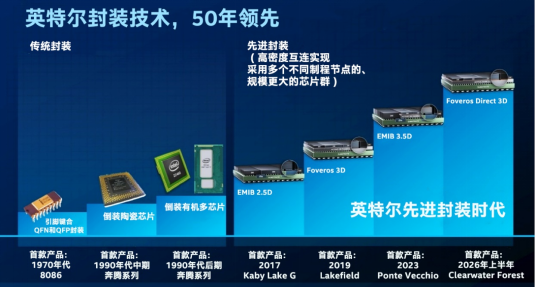

近日,英特爾對外分享了英特爾封裝技術路線圖。英特爾院士、封裝研究與系統(tǒng)解決方案總監(jiān)Johanna Swan分享道,從標準封裝到嵌入式橋接時,凸點間距從 100 微米變?yōu)?55-36 微米。到Foveros封裝時,英特爾將芯片堆疊在一起,實現(xiàn)橫向和縱向的互連,凸點間距大概是50微米。未來,英特爾將通過采用Hybrid Bonding(有兩種翻譯:混合鍵合、混合結(jié)合)技術,計劃實現(xiàn)小于 10 微米的凸點間距。

將凸點間距縮小到小于10微米, Hybrid Bonding技術究竟是如何實現(xiàn)的?

Hybrid Bonding技術顛覆焊接技術

英特爾今年曾在ECTC 上發(fā)表關于混合鍵合技術的論文。Johanna Swan介紹,混合鍵合技術是一種在相互堆疊的芯片之間獲得更密集互連的方法,并幫助實現(xiàn)更小的外形尺寸。

當縮減到大約 10 微米的凸點間距,將能夠達到每平方毫米 10,000 個凸點。 這樣,兩個芯片之間能夠?qū)崿F(xiàn)更多的互連,進而可以提供更小、更簡單的電路,因為它們可以相互疊加,也不必做扇入(fan-in)和扇出(fan-out)。

“有了這個更簡單的電路,我們可以使用更低的電容, 然后開始降低該通道的功率,這有助于朝著提供最好產(chǎn)品方向發(fā)展。” Johanna Swan表示。

Hybrid Bonding與Foveros 技術所實現(xiàn)的焊接有諸多區(qū)別。

混合鍵合技術使電介質(zhì)的芯片非常光滑,而不是有一個突出的凸點。實際上,還會有一個略微的凹陷。 當采用混合鍵合技術將兩個組件放在一起時,可以在室溫下進行,將它們放置好后,再升高溫度對其進行退火,銅在這時會膨脹,從而形成電氣連接。

Johanna Swan認為:“這非常有用,因為可獲得更高的載流能力,并且可以將間距縮小到 10 微米以下。這樣使我們目前在這些接口之間獲得了比底部填充和緊密的銅密度更好的熱性能。當使用混合鍵合技術時,將需要一種新的制造、清潔和測試方法。”

轉(zhuǎn)向更小的間距可能會更有吸引力。 英特爾正在轉(zhuǎn)向多個晶片,將其分解成 GPU、CPU、IO或區(qū)塊,之后或許可以使用更小的區(qū)塊去擁有單獨的 IP, 這使得擁有更多區(qū)塊,進而可以重復使用。Johanna Swan指出,這項技術可以根據(jù)特定客戶的獨特需求定制產(chǎn)品。 這種技術可改變晶片到晶片的互連,從焊接轉(zhuǎn)向混合鍵合。

如果必須保持制造流程以相同的速度進行,當又有更多的晶片需要放置時,需要如何應對?為此,英特爾正在考慮的解決方案是批量組裝,簡稱“自組裝”。

當前,英特爾正在與 CEA-LETI(法國原子能委員會電子與信息技術實驗室) 合作,研究一次能夠放置多個晶片,并且進行自組裝。

封裝將繼續(xù)小型化和縮小尺寸

在可擴展性軸上,包括CO-EMIB技術和ODI 全方位互連技術。

CO-EMIB技術嘗試通過使用 EMIB 和 Foveros 的組合來融合 2D 和 3D 的技術, 這種架構(gòu)基于與配套晶片和堆疊芯片復合體的高密度連接,實現(xiàn)了比基礎尺寸更大的尺寸。

ODI 全方位互連技術,是英特爾正在使用的封裝的一個新維度。

對于2.5D 和 3D的組合,Johanna Swan指出,這種趨勢肯定會繼續(xù)下去,因為擁有的發(fā)展機會是在每毫米立方體上提供盡可能多的區(qū)塊并獲得每毫米立方體盡可能多的功能。封裝將繼續(xù)小型化和縮小尺寸,以便可以獲得毫米立方體的最大功能。

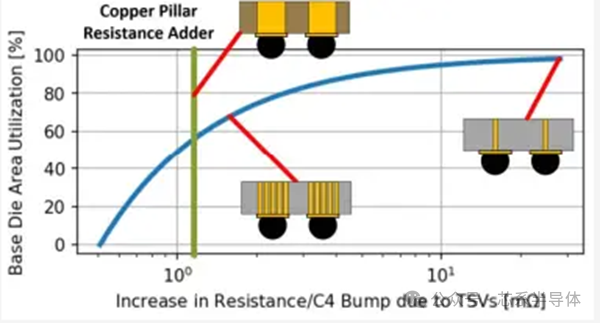

英特爾的 Foveros技術,通過該技術堆疊芯片,使用硅通孔Through -Silicon-Via(TSV) 技術在封裝和晶片之間通信,一直到頂部晶片。

然而,ODI 封裝技術是另一種優(yōu)化,通過添加 ODI 封裝技術為客戶進行定制。在右側(cè)添加了支柱,允許最右側(cè)的頂部管芯直接連接到封裝,這使得可以將較小的 TSV 芯片面積用于硅通孔 (TSV),進而減少數(shù)量。這些支柱提供了直接向頂部晶片封裝供電的能力。頂部的兩個晶對下部的晶片有更高的帶寬、更小的凸點、更小的通道。

對于如何推動封裝的不斷演進,Johanna Swan認為:“封裝是一個差異化優(yōu)勢的區(qū)分因素,關鍵是客戶。我們努力服務并提供獨特的解決方案給客戶,這也推動了我們關注技術。因此,封裝的機會在于,隨著繼續(xù)為客戶提供服務,客戶的產(chǎn)品需求在不斷進化,這才是真正推動封裝技術需要轉(zhuǎn)變的原因。客戶的這種差異化需求也會推動相應的封裝技術的出現(xiàn)。

為了滿足客戶的需求,晶圓制造企業(yè)開始致力于先進封裝技術,這也將晶圓制造與封裝兩個環(huán)節(jié)的界線開始模糊。對于兩者今后的發(fā)展趨勢,Johanna Swan也表達了自己的理解:“在 10 微米間距的混合鍵合時,這兩個世界已經(jīng)開始融合,我開始研究我們正在使用的金屬層的特征低于 10 微米,像 4 微米。晶圓制造和封裝正在融合,這已經(jīng)成為一個非常重要、有趣的創(chuàng)新場所,因為它們的尺寸相同,所以這種放置是非常令人興奮的,使用具有封裝測試技術的傳統(tǒng)晶圓廠工具并創(chuàng)造出我們在封裝方面進行創(chuàng)新的全新領域。

(校對/清泉)

發(fā)布評論請先 登錄

英特爾先進封裝,新突破

英特爾持續(xù)推進核心制程和先進封裝技術創(chuàng)新,分享最新進展

英特爾代工:明確重點廣合作,服務客戶鑄信任

英特爾先進封裝:助力AI芯片高效集成的技術力量

英特爾與Stellantis Motorsports攜手推進自適應控制技術

英特爾推出全新英特爾銳炫B系列顯卡

英特爾獲78.6億美元美國芯片補貼

英特爾宣布擴容成都封裝測試基地

英特爾擴容在成都的封裝測試基地

英特爾至強品牌新戰(zhàn)略發(fā)布

淺談英特爾在先進封裝領域的探索

英特爾推出Hybrid Bonding技術 推進高端封裝演進

英特爾推出Hybrid Bonding技術 推進高端封裝演進

評論