Vivado 的XDC設置輸出延時,用于輸出伴隨時鐘和數據的,數據是由系統時鐘125M驅動,伴隨時鐘是由125M經過Pll相位移動-90度。

設置輸出時鐘時,參考時鐘選擇相移的那個,發現不起作用,沒有路徑。

如果選擇系統時鐘,分析后是系統時鐘的最大最小延時,沒有相位移動后的信息,這是什么問題?

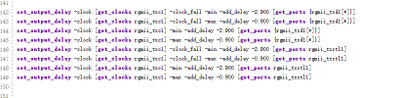

伴隨時鐘創建的Create_generated_clock中的Set_output_delay如下:

Txc1 是鎖相環移動相位后直接送到輸出管腳,Rxc1是驅動數據的。

數據輸出路徑以及對應的Clock的連接Schematic截圖

Txc是Rx經過鎖相環再經過oddr生成的

數據輸出是Rxc驅動Oddr打出來的

軟件認為這個時鐘沒有路徑,這個問題在ISE上也遇到過,軟件時鐘始終不認伴隨時鐘

A1

ISE約束和Vivado的約束用法不同,Create_generated_clock的source指定的net是哪一段,改為用get_pins指定的ODDR的C pin試試。Report_clocks結果查一下你的clock約束都生效了嗎?

Q2

指定Obuf的O管腳和Edit Constraints重新編輯后,約束成功了,請問原因是什么?create_generated_clock在set_output_delay約束的簽名,有時候把鎖相環輸出的bufg改成no buffer但是生成的網表里仍然有,關閉再打開就沒了,但時序分析路徑卻有這個bug。

A2

是不是synthesized design沒有reload?如果synthesized design 已經是打開的情況下,修改設計重新synthesize,已經打開的synthesized design會提示需要reload,否則是修改之前的結果

如果發生約束沒有約束上的問題,可以查一下messages窗口里的critical warning或warning,看是否有提到關于這條約束的問題。

也可以在synthesized design或者implemented design的tcl console里,report_timing用-from -to指定路徑起始點來report下相應path看是如何分析的,可以從分析結果看下是path不存在還是約束有問題。

如果用edit constraints重新編輯并保存就好了,很可能是原來手寫的約束哪里有問題

原文標題:本周一問 | Vivado 的XDC設置輸出延時

文章出處:【微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Xilinx

+關注

關注

73文章

2185瀏覽量

125282 -

Vivado

+關注

關注

19文章

835瀏覽量

68734

原文標題:本周一問 | Vivado 的XDC設置輸出延時

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Vivado無法選中開發板的常見原因及解決方法

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

STM32F030內部晶振怎么設置,內部晶振是延時函數怎么設置?

一文詳解Vivado時序約束

使用STM32F030時沒使用內部晶振怎么設置,使用內部晶振時延時函數怎么寫?

Vivado Design Suite用戶指南:邏輯仿真

VIVADO的調試窗口IAL監測到AFE5816輸出電壓大了一倍,怎么解決?

U50的AMD Vivado Design Tool flow設置

每次Vivado編譯的結果都一樣嗎

Vivado使用小技巧

Vivado的XDC設置輸出延時問題

Vivado的XDC設置輸出延時問題

評論