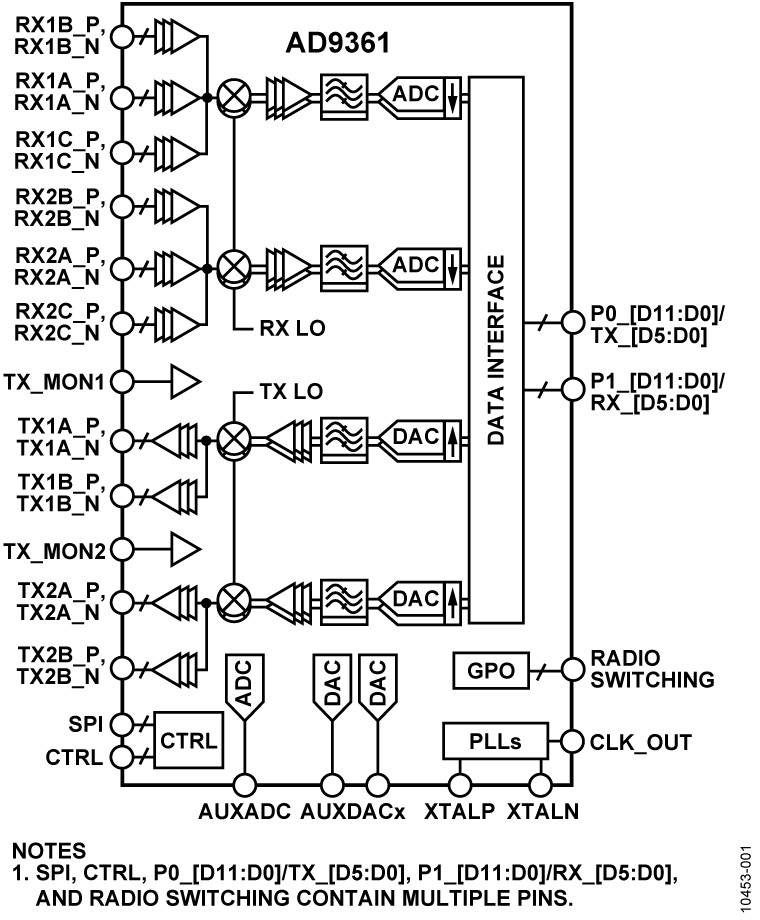

ADI是業界卓越的半導體公司,在模擬信號、混合信號和數字信號處理的設計與制造領域都發揮著十分重要的作用。到目前為止,推出了多款芯片,涉及的領域十分廣闊。針對推出的芯片,都有配套的開發板與其芯片子模塊進行配套使用,所以配套資源包含該芯片的FPGA邏輯代碼,都上傳到github上,所有的代碼都是免費公開的。

2 工程建立

2.1 自我環境檢查

首先檢查自己的Vivado或者Quartus的版本號,選擇對應的ADI官方提供的免費HDL與no-OS庫。HDL庫存放的是對應芯片的FPGA驅動程序,no-OS存放的是芯片SDK下的C程序。

2.2 克隆對應代碼

利用git軟件克隆hdl與no-OS庫,以便后續使用。

git clone https://github.com/analogdevicesinc/no-OS.git

git clone https://github.com/analogdevicesinc/hdl.git

2.3 安裝編譯工具

在Windows電腦上安裝Cygwin軟件,詳細的安裝教程網上很多,不在贅述。也可以用Vivado或者Quartus自帶的編譯器進行編譯,用戶可自己嘗試。

Cygwin是一個在windows平臺上運行的類UNIX模擬環境,是cygnus solutions公司開發的自由軟件(該公司開發的著名工具還有eCos,不過現已被Redhat收購)。它對于學習UNIX/Linux操作環境,或者從UNIX到Windows的應用程序移植,或者進行某些特殊的開發工作,尤其是使用GNU工具集在Windows上進行嵌入式系統開發,非常有用。隨著嵌入式系統開發在國內日漸流行,越來越多的開發者對Cygwin產生了興趣。

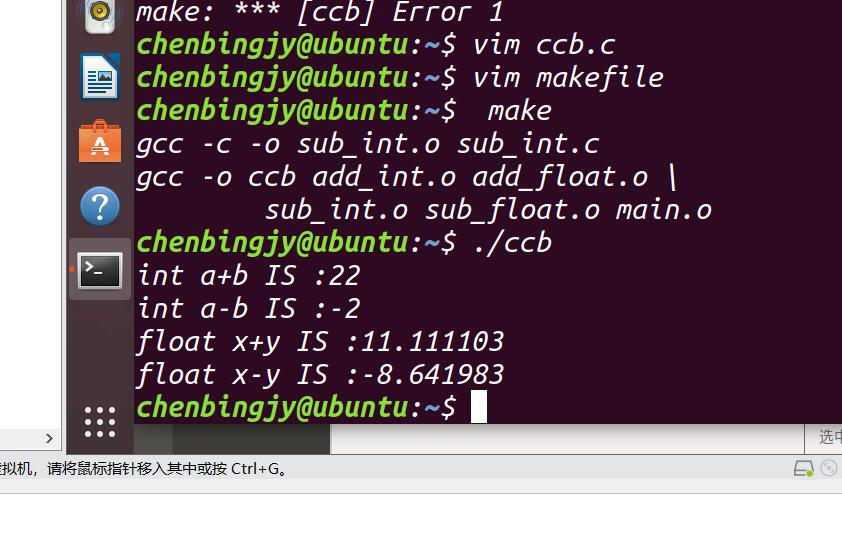

2.4 編譯tcl工程

首先找到自己Vivado或者Quartus安裝的具體目錄,打開Cygwin,輸入下面的指令并執行(根據自己的目錄輸入)。

export PATH=$PATH:/cygdrive/C/Xilinx/Vivado/2018.2/bin

找到上述下載的hdl庫目錄,先對library進行編譯,如果不確定接下來工程需要哪些庫,對全部庫文件編譯即可。

make -C C:/gitadi/analogdevicesinc/hdl/hdl-hdl_2018_r2/library all

接下來對想要編譯的工程進行編譯,由于fmcomms5包含兩片AD9361,正式我所需要的參考工程,在選擇對應的開發板zc706即可(不要對所有的工程進行編譯,工程量太大)。

make -C C:/gitadi/analogdevicesinc/hdl/hdl-hdl_2018_r2/projects/fmcomms5/zc706

編譯完成后,打開對應的工程,可以看到詳細的工程設計,用戶可以根據自己的需求進行修改。

2.5 詳細的參考文章

上述講解只針對Windows環境下Vivado相關工程的編譯,如果用戶有Linux系統或者使用Quartus軟件需求等等,更為詳細的編譯說明參考鏈接如下:https://wiki.analog.com/resources/fpga/docs/build

3 no-OS庫的編譯

上述工程編譯完成后,導出bit文件到SDK,并將no-OS庫下對應工程的c文件拷貝到SDK工程之下,重新編譯即可得到整個完整工程(HDL工程與ARM工程)。接下來用戶就可以對整個工程進行測試修改,轉化為自己的程序。

如果對SDK下c文件工程的建立與編譯仍然不清楚,可以參考以下官方鏈接:https://wiki.analog.com/resources/eval/user-guides/ad-fmcomms2-ebz/software/baremetal

需要注意的一點就是,官方給的工程量比較大,需要將堆棧設置到合理的值,否則編譯會出現錯誤。

原文標題:AD9361官方FPGA工程編譯

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1643文章

21971瀏覽量

614315 -

ADI

+關注

關注

148文章

46025瀏覽量

258884

原文標題:AD9361官方FPGA工程編譯

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA Verilog HDL語法之編譯預處理

DLPNIRNANOEVM按照官方文檔編譯文件時報錯gmake: *** [NIRscanNano.out] Error -1073741819怎么解決?

AD9361 RF捷變收發器,評估套件和開發資源

【米爾-紫光PG2L100H國產FPGA開發板試用】官方LED例程測試體驗

多平臺FPGA工程快速移植與構建

FIFO Generator的Xilinx官方手冊

每次Vivado編譯的結果都一樣嗎

AD936x RF收發器應用相關問答

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

淺談Vivado編譯時間

AD9361官方FPGA工程編譯過程

AD9361官方FPGA工程編譯過程

評論