數(shù)據(jù)時(shí)代對(duì)計(jì)算提出新需求

在過(guò)去的一年半中,全球經(jīng)歷了新冠疫情的肆虐。雖然已經(jīng)有多種疫苗開始實(shí)施接種,但是新冠疫情在未來(lái)相當(dāng)長(zhǎng)的一段時(shí)間里對(duì)我們的生活依舊持續(xù)帶來(lái)影響。我們很多人已經(jīng)習(xí)慣了通過(guò)電子設(shè)備在家辦公、上網(wǎng)課、開會(huì)甚至舉辦線上大型會(huì)議。2020年,全球市值最大的10家公司中前8家公司都是基于互聯(lián)網(wǎng)和大數(shù)據(jù)開展業(yè)務(wù),另外值得關(guān)注的是半導(dǎo)體制造商臺(tái)積電(TSMC)位列第9位。21世紀(jì)將會(huì)是數(shù)據(jù)的世紀(jì),數(shù)據(jù)已經(jīng)成為類似石油的新型資源。大數(shù)據(jù)、圖像分析、機(jī)器學(xué)習(xí)已經(jīng)非常普遍,從數(shù)據(jù)中心、移動(dòng)設(shè)備到物聯(lián)網(wǎng)設(shè)備都會(huì)成為數(shù)據(jù)處理的主要節(jié)點(diǎn)。高性能計(jì)算機(jī)前所未有地成為我們生活中的必需品,并且極大推動(dòng)了對(duì)高算力計(jì)算芯片的龐大需求。

傳統(tǒng)集成技術(shù)下的摩爾定律已經(jīng)不再有效

在1965年Gordon Moore提出摩爾定律到今天的近56年中,摩爾定律的效率已經(jīng)逐步衰退到接近失效。Alphabet的董事長(zhǎng)John Hennessy于2018年在美國(guó)國(guó)防高級(jí)研究計(jì)劃局電子復(fù)興計(jì)劃會(huì)議(DARPA ERI)上的演講中展示了一張圖片,是過(guò)去40年來(lái)計(jì)算機(jī)性能的增長(zhǎng)趨勢(shì)。可以看到,在1978年到1986年,計(jì)算機(jī)性能的平均每年長(zhǎng)率是25%,隨后的1986年到2003年的17年中,年平均增長(zhǎng)率增加到52%。接下來(lái)的10年,計(jì)算機(jī)性能的年平均增長(zhǎng)率開始下降到23%,隨后的幾年,進(jìn)一步下降到12%,直到近5年,已經(jīng)下降到了3.5%。

近40年來(lái),計(jì)算機(jī)性能增長(zhǎng)的趨勢(shì)

John Shalf在2019國(guó)際超級(jí)計(jì)算機(jī)會(huì)議上的演講中展示了一張圖片,在過(guò)去近50年中,計(jì)算機(jī)系統(tǒng)在晶體管數(shù)量、單線程性能、時(shí)鐘頻率、功耗以及內(nèi)核數(shù)量這5個(gè)指標(biāo)上的發(fā)展趨勢(shì)。可以看到,在2021年,這些指標(biāo)都有可能趨于飽和。今天,我們正在面臨摩爾定律的終結(jié),需要尋找一種新的路徑繼續(xù)提高電子產(chǎn)品的性能。

計(jì)算機(jī)技術(shù)發(fā)展趨勢(shì)在2021年趨于飽和

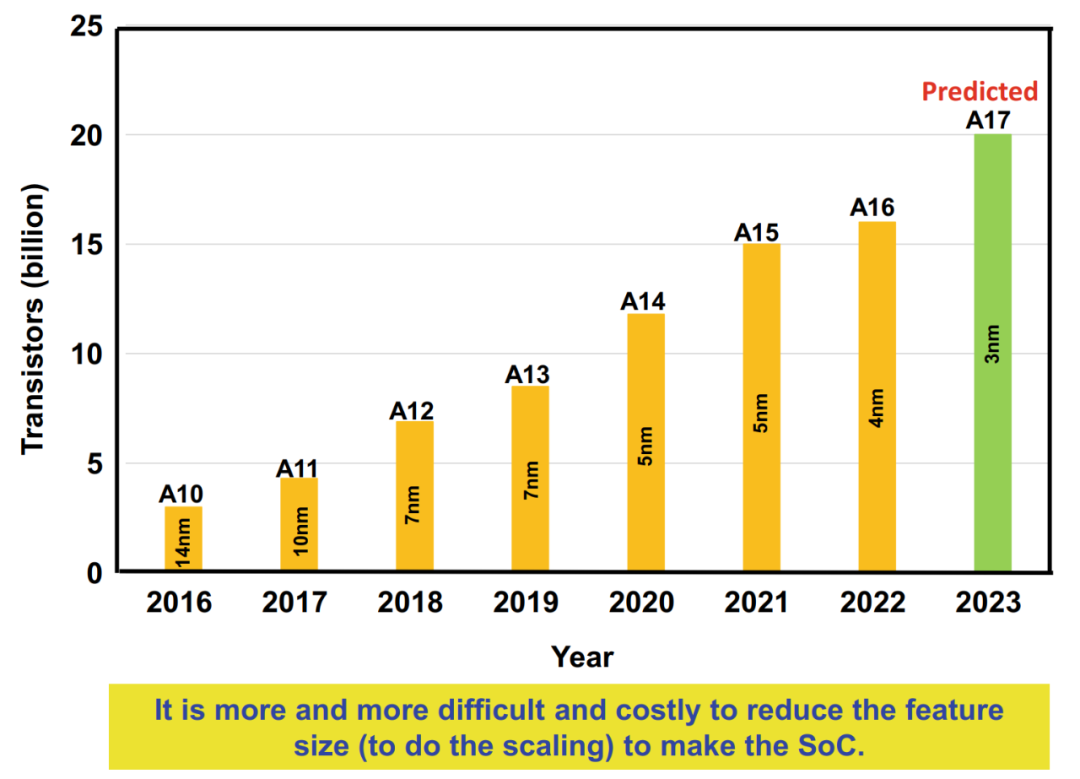

國(guó)際半導(dǎo)體技術(shù)藍(lán)圖(ITRS)自從1991年誕生到2016年7月發(fā)布了最后的版本,指出半導(dǎo)體體積到2021年將不再縮小。報(bào)告認(rèn)為,半導(dǎo)體廠商將面積縮小、放下更多晶體管的做法在經(jīng)濟(jì)上已經(jīng)不劃算。此后,半導(dǎo)體廠商將更多關(guān)注3D芯片等其他技術(shù)增強(qiáng)計(jì)算性能。AMD的CEO Lisa Su在2019年的DARPA ERI會(huì)議上也展示了隨著工藝節(jié)點(diǎn)從45nm逐步過(guò)渡到5nm,單位芯片面積的成本增加到了最初的5倍。

摩爾定律的經(jīng)濟(jì)效應(yīng)遇到瓶頸

異構(gòu)集成將推動(dòng)摩爾定律趨勢(shì)繼續(xù)有效

2015年,ITRS的異構(gòu)集成(Heterogeneous Integration)研究團(tuán)隊(duì)與電氣電子工程師學(xué)會(huì)(IEEE)的元器件、封裝、制造技術(shù)學(xué)會(huì)(CPMT)簽署了一份諒解備忘錄,宣告異構(gòu)集成藍(lán)圖(HIR)成立并開始完全代替ITRS。HIR 由IEEE的3個(gè)學(xué)會(huì)(電子封裝學(xué)會(huì)EPS、電子器件學(xué)會(huì)EDS、光電學(xué)會(huì)PS)和半導(dǎo)體設(shè)備和材料國(guó)際組織(SEMI) 與美國(guó)機(jī)械工程師學(xué)會(huì)的電子與光子封裝事業(yè)部 (ASME EPPD)共同組成。目的是為了維護(hù)把不同工藝制造的元器件集成在一起的先進(jìn)封裝技術(shù)的進(jìn)步步伐,以便使當(dāng)今和未來(lái)的電子系統(tǒng)得到更增強(qiáng)的功能和操作體驗(yàn)。

異構(gòu)集成通過(guò)工藝技術(shù)的多樣性、功能多樣性和材料的多樣性進(jìn)行系統(tǒng)級(jí)的集成或3D封裝,將進(jìn)一步推動(dòng)半導(dǎo)體工業(yè)第四波技術(shù)浪潮以便維持摩爾定律趨勢(shì)繼續(xù)有效。技術(shù)多樣性需要將不同工藝節(jié)點(diǎn)的芯片集成在一起,不同于傳統(tǒng)SoC技術(shù)手段去統(tǒng)一追求更先進(jìn)的工藝節(jié)點(diǎn),對(duì)于某些性能優(yōu)異的工作穩(wěn)定的IP或稱為小芯片(Chiplet)可以更長(zhǎng)時(shí)間停留在較早的工藝節(jié)點(diǎn)上。對(duì)于功能多樣性體現(xiàn)在把數(shù)字、模擬、模數(shù)混合、光電子、微機(jī)械等等不同類別的芯片做集成,這在傳統(tǒng)SoC技術(shù)路徑上是很難做到的。材料多樣性是異構(gòu)集成最重要的特性,不局限于傳統(tǒng)CMOS工藝,采用多種工藝結(jié)合的方式,比如采用光學(xué)系統(tǒng)的I/O。

異構(gòu)集成是延長(zhǎng)摩爾定律的第4波浪潮

Intel的 Agilex系列FPGA是非常典型的異構(gòu)集成成功案例,它既包含了傳統(tǒng)FPGA靈活的可編程性,又結(jié)合了現(xiàn)代FPGA基于異構(gòu)架構(gòu)的敏捷性。通過(guò)Intel定義的EMIB總線將不同工藝節(jié)點(diǎn)的小芯片連接起來(lái)。

AMD的EPYC處理器是另一個(gè)異構(gòu)集成的案例。在第一代EPYC中,處理器由4個(gè)14nm工藝的小芯片組合而成。而到第二代EPYC時(shí),處理器由4組共八個(gè)7nm小芯片和一個(gè)14nm的I/O芯片組合而成。

以下是幾款主流手機(jī)處理器芯片的切面圖,可以看到,Apple A12采用了WLP Fan-out工藝封裝集成,而三星 EXYNOS9810和華為Kirin980都是采用了先進(jìn)PoP工藝封裝集成。

異構(gòu)集成不僅僅是封裝加工

異構(gòu)集成對(duì)傳統(tǒng)的封裝測(cè)試廠商(OSAT)提出了更高要求,無(wú)論是從系統(tǒng)設(shè)計(jì)還是EMI/PI/SI協(xié)同優(yōu)化仿真,熱性能優(yōu)化和結(jié)構(gòu)優(yōu)化仿真都與傳統(tǒng)封裝廠的工藝技術(shù)有較大區(qū)別。未來(lái),承擔(dān)異構(gòu)集成設(shè)計(jì)的廠商絕不能僅僅是一家封裝代工廠,而是需要能夠提供完整的先進(jìn)封裝設(shè)計(jì)與制造解決方案的廠商。在眾多廠商中,ASE、Amkor具備了優(yōu)秀和完整的整體解決方案。國(guó)內(nèi)廠商中,通富AMD和長(zhǎng)電收購(gòu)的星科金朋也有比較強(qiáng)的整體方案能力。

銳杰微科技在異構(gòu)集成方面擁有多年積累

銳杰微在芯片封裝設(shè)計(jì),電性能仿真、分析、優(yōu)化,熱性能分析優(yōu)化,機(jī)械應(yīng)力分析優(yōu)化方面經(jīng)過(guò)大量的高端系統(tǒng)化芯片產(chǎn)品的項(xiàng)目經(jīng)驗(yàn),構(gòu)建了一套獨(dú)特的方案設(shè)計(jì)、仿真、優(yōu)化思路,幫助國(guó)內(nèi)百余家中高端科研、商業(yè)客戶完成大量業(yè)內(nèi)首創(chuàng)產(chǎn)品,涵蓋國(guó)產(chǎn)CPU、GPU、FPGA、DSP以及ADC、手機(jī)處理器、AI、車載控制芯片領(lǐng)域,下面是銳杰微的經(jīng)典案例中比較突出產(chǎn)品:

CPU+FPGA SiP(網(wǎng)絡(luò)處理芯片)

多芯片球陣列網(wǎng)絡(luò)處理器芯片,包含DDR3(1600Mbps),PCIE2.0(5Gbps)、XAUI(6.25Gbps)等高速信號(hào),該項(xiàng)在有限的空間內(nèi)部封裝有大量的高速信號(hào)互聯(lián),并且實(shí)現(xiàn)互相干擾達(dá)標(biāo)。61mm x61mm的大尺寸封裝同時(shí)也對(duì)設(shè)計(jì)和加工帶來(lái)極大挑戰(zhàn)

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:61mm x 61mm

Ball數(shù)量:3576

基板:10 層有機(jī)基板

CPU+FPGA+Flash SiP

該產(chǎn)品同樣屬于大尺寸封裝,50mm x 50mm,高速率、多信號(hào),含 PCIE x 16 3.0,DDR3 x 72,USB 2.0 等高速接口,內(nèi)部集成多芯片,并且結(jié)合Solder Ball 和 Copper Pillar 兩種倒裝工藝形式,基板的設(shè)計(jì)和表面處理工藝滿足兩種 Bump 加工工藝的設(shè)計(jì)與加工參數(shù)

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:50mm x 50mm

Ball數(shù)量:2089

基板:10 層有機(jī)基板

DSPSiP(處理芯片)

大規(guī)模的HFCBGA 封裝芯片,集高性能、高密度一體化數(shù)字處理模塊,高速串并行信號(hào)(PCIE 3.0;Serdes 10.125 Gbps;TDP 60W;內(nèi)部集成 8 顆 4Gb DDR3 4 x 72bit 1600Mbps )和一顆 Flash 外加一顆 DSP 芯片。DDR 芯片原始設(shè)計(jì)為 WB 工藝,銳杰微對(duì)該芯片進(jìn)行了 RDL 二次設(shè)計(jì),使 DDR 芯片改為倒裝工藝,在基板的設(shè)計(jì)過(guò)程中對(duì) DDR 拓樸的排布,封裝一次加工就達(dá)到了項(xiàng)目要求。9 顆大功耗的芯片集成在一個(gè)封裝內(nèi),特別是主芯片電流達(dá)到 30A,在如此小的封裝內(nèi)部很好的滿足了大電流低電壓的電源完整性和散熱問(wèn)題

封裝形式:HFCBGA(Flip Chip Ball Grid Array with Heat Spread)

封裝尺寸:35mm x 35mm

Ball數(shù)量:1024

基板:10 層有機(jī)基板

銳杰微同時(shí)在先進(jìn)封裝領(lǐng)域也積累了2.5D高密度和復(fù)雜TSV 的設(shè)計(jì)及應(yīng)用項(xiàng)目經(jīng)驗(yàn),具備完整的設(shè)計(jì)、仿真、產(chǎn)品評(píng)估能力,下面是一款從設(shè)計(jì)到仿真(信號(hào)完整性、電源完整性、結(jié)構(gòu)應(yīng)力)、加工工藝、組裝工藝、表面處理工藝到產(chǎn)品的陶封TSV正反雙腔體、FC和WB混合工藝的SiP封裝產(chǎn)品:

CPGA(陶封)SiP

陶瓷正反雙腔體、TSV 2.5D 封裝結(jié)構(gòu)、21 顆裸芯,正面 WB,反面 FC 混合工藝,包含 DDR3 、FPGA 、DSP 、AD 、Flash 及部分高速差分和模擬信號(hào),大型陶瓷封裝,應(yīng)用在高可靠性領(lǐng)域,封裝采用了先進(jìn)的 2.5D 工藝,封裝內(nèi)部集成了紅外光感芯片,DSPFPGA5片DDRAD芯片,集成度高,功能復(fù)雜。DDR 難度較大,在有限的空間內(nèi)及針對(duì)陶瓷基板很好的匹配有限的工藝能力同時(shí)實(shí)現(xiàn)大功耗,高頻率的信號(hào)連接

封裝形式:CPGA (Ceramic Pin Grid Array)

封裝尺寸:40mm x 40mm

Ball數(shù)量:316

基板:23層陶瓷基板

銳杰微科技是一家高度重視知識(shí)產(chǎn)權(quán)的科技企業(yè),建有一套完整的知識(shí)產(chǎn)權(quán)管理體系,不斷激勵(lì)創(chuàng)新。在公司發(fā)展的過(guò)程中,不斷地獲得政府和產(chǎn)業(yè)的高度認(rèn)可。

在美國(guó)對(duì)華科技打壓的大背景下,異構(gòu)集成是實(shí)現(xiàn)彎道追趕的最佳路徑

1947年,美國(guó)貝爾實(shí)驗(yàn)室發(fā)明了世界上第一個(gè)晶體管。直到1956年,中國(guó)才成功制成第一根硅單晶棒。1958年,當(dāng)時(shí)在TI工作的Jack Kilby做出的世界上首個(gè)集成電路。1968年,國(guó)防科工委決定在永川建立一個(gè)專業(yè)從事集成電路及相關(guān)技術(shù)研究的綜合性研究所——“中國(guó)人民解放軍一四二四研究所”,這也是我國(guó)第一個(gè)集成電路專業(yè)研究所。1972年6月成功研制出了我國(guó)第一塊PMOS型大規(guī)模集成電路——120位靜態(tài)移位寄存器(集成了1084個(gè)元件/片)。中國(guó)的集成電路行業(yè),從起步就已經(jīng)落后美國(guó)十幾年。這個(gè)行業(yè)一直是中國(guó)在追趕美國(guó)的步伐。

美國(guó)對(duì)中國(guó)在集成電路方面的打壓并不是近幾年才有的事情,對(duì)于最先進(jìn)的工藝技術(shù),很多年前就已經(jīng)保持著對(duì)華封鎖的態(tài)勢(shì),這也使得中國(guó)在工藝代差上始終落后美國(guó)至少2~3代。這種代差對(duì)于數(shù)字集成電路如CPU的性能影響尤其比較大。在摩爾定律最穩(wěn)定的那段時(shí)間,工藝節(jié)點(diǎn)決定了芯片的性能。不過(guò)隨著摩爾定律的逐漸退化,近幾年來(lái),用以提升處理器性能的方式已經(jīng)不僅僅是采用先進(jìn)工藝制程等,同時(shí)代差的影響已經(jīng)沒(méi)有過(guò)去那么大了。

隨著多核架構(gòu)、高吞吐存儲(chǔ)等方式的運(yùn)用,采用10nm制程的多芯片異構(gòu)集成方式處理器性能未必會(huì)遜色于采用7nm SoC單芯片方式的性能。Intel的Agilex FPGA就是個(gè)成功案例。這也給目前中國(guó)面臨的巨大國(guó)產(chǎn)替代壓力下的集成電路行業(yè)提供了一個(gè)新思路。通過(guò)已有的工藝能力加工出小芯片(chiplet),用異構(gòu)集成的方式進(jìn)行性能和功能的擴(kuò)展集成,同樣可以實(shí)現(xiàn)小型化、高性能的芯片方案。而且隨著工藝節(jié)點(diǎn)的繼續(xù)升級(jí),這種改善比單純依賴提高工藝水平的性價(jià)比高很多。

美國(guó)Intel成立了一個(gè)名為HI3(Heterogeneous Integration Incorporating Intel)的合作標(biāo)準(zhǔn)組織,發(fā)展Chiplet生態(tài)環(huán)境。目前已經(jīng)有包括Intel、TSMC、GF等多個(gè)工藝節(jié)點(diǎn)的數(shù)十個(gè)Chiplet量產(chǎn)。

銳杰微科技也已在幾年前就致力于發(fā)展中國(guó)自有的chiplet標(biāo)準(zhǔn),早在2019年就加入了中國(guó)軟件定義互連技術(shù)與產(chǎn)業(yè)創(chuàng)新聯(lián)盟(SDI),于2020年加入了中國(guó)計(jì)算機(jī)互連技術(shù)聯(lián)盟(CCITA)。在異構(gòu)集成方面,中國(guó)完全不必按照美國(guó)的路徑追趕。通過(guò)建立自己的芯片互聯(lián)標(biāo)準(zhǔn),完全可以在上一波摩爾定律退化失效而第4波浪潮還未起來(lái)的時(shí)候彎道趕上。在中美科技對(duì)抗的大環(huán)境下,這樣做也是必要的。

原文標(biāo)題:展商動(dòng)態(tài) | 異構(gòu)集成重新定義封裝在芯片產(chǎn)業(yè)鏈中的地位——銳杰微科技集團(tuán)總裁 劉海川

文章出處:【微信公眾號(hào):ELEXCON深圳國(guó)際電子展】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52202瀏覽量

436427 -

封裝

+關(guān)注

關(guān)注

128文章

8526瀏覽量

144826 -

異構(gòu)集成

+關(guān)注

關(guān)注

0文章

36瀏覽量

2047

原文標(biāo)題:展商動(dòng)態(tài) | 異構(gòu)集成重新定義封裝在芯片產(chǎn)業(yè)鏈中的地位——銳杰微科技集團(tuán)總裁 劉海川

文章出處:【微信號(hào):ELEXCON深圳國(guó)際電子展,微信公眾號(hào):ELEXCON深圳國(guó)際電子展】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

電力電子中的“摩爾定律”(2)

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

電力電子中的“摩爾定律”(1)

AI時(shí)代,封裝材料如何助力實(shí)現(xiàn)更優(yōu)的異構(gòu)集成?

瑞沃微先進(jìn)封裝:突破摩爾定律枷鎖,助力半導(dǎo)體新飛躍

2.5D集成電路的Chiplet布局設(shè)計(jì)

混合鍵合中的銅連接:或成摩爾定律救星

石墨烯互連技術(shù):延續(xù)摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

后摩爾定律時(shí)代,提升集成芯片系統(tǒng)化能力的有效途徑有哪些?

異構(gòu)集成封裝類型詳解

潤(rùn)欣科技與奇異摩爾簽署CoWoS-S封裝服務(wù)協(xié)議

高算力AI芯片主張“超越摩爾”,Chiplet與先進(jìn)封裝技術(shù)迎百家爭(zhēng)鳴時(shí)代

異構(gòu)集成將推動(dòng)摩爾定律趨勢(shì)繼續(xù)有效

異構(gòu)集成將推動(dòng)摩爾定律趨勢(shì)繼續(xù)有效

評(píng)論