斷言是一種條件語句,通過標記錯誤繼而捕獲錯誤來指示設計的不正確行為。斷言用于驗證處于不同生命周期階段(例如形式驗證、動態(tài)驗證、運行時監(jiān)控和仿真)的硬件設計。基于斷言的驗證為設計和驗證過程提供了顯著的好處。它有助于輕松地檢測功能錯誤,讓用戶能

夠查找更接近實際問題根源的錯誤,以及確保在設計流程的早期找出錯誤。斷言為整個設計和驗證周期帶來了諸多直接好處;因此,工程師在斷言的編碼和測試過程中遇到的任何挑戰(zhàn),都值得加以解決。

UVM 中的回調是一種用于改變驗證組件(例如驅動器或監(jiān)視器)的行為而無需實際更改組件代碼的機制。Uvm_callback 類提供了用于實現(xiàn)回調的基類。從 uvm_callback擴展類并非推薦的編碼實踐,因為這可能導致一些潛在的排序問題。在 Siemens Digital Industries Software 下屬部門 Siemens EDA 所提供的 Questa Verification IP(QVIP) 中,回調是通過擴展基類并為其填充必要的方法來實現(xiàn)的,以達成諸如將某個序列項替換為另一個包含一組新屬性的序列項之類的回調實現(xiàn)。

斷言驗證通常構成整個驗證 IP 開發(fā)周期不可或缺的一部分。第一步是編寫斷言,第二步是通過所謂的 “錯誤注入” 來對這些斷言場景進行驗證。回調對于此激勵生成步驟可能非常有益,因為驗證工程師不必修改源代碼,而只需改變擴展的類便能測試不同的場景。這在 PCIe之類基于數(shù)據(jù)包的協(xié)議中特別有用,因為這類協(xié)議中的字段會被損壞,而通過回調可以提供精細的控制。因此回調可提高整個驗證過程的功效,使其更加穩(wěn)定可靠。

原文標題:免費下載 | 使用UVM回調簡化斷言驗證

文章出處:【微信公眾號:Mentor明導】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

IP

+關注

關注

5文章

1785瀏覽量

151305 -

UVM

+關注

關注

0文章

182瀏覽量

19430

原文標題:免費下載 | 使用UVM回調簡化斷言驗證

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

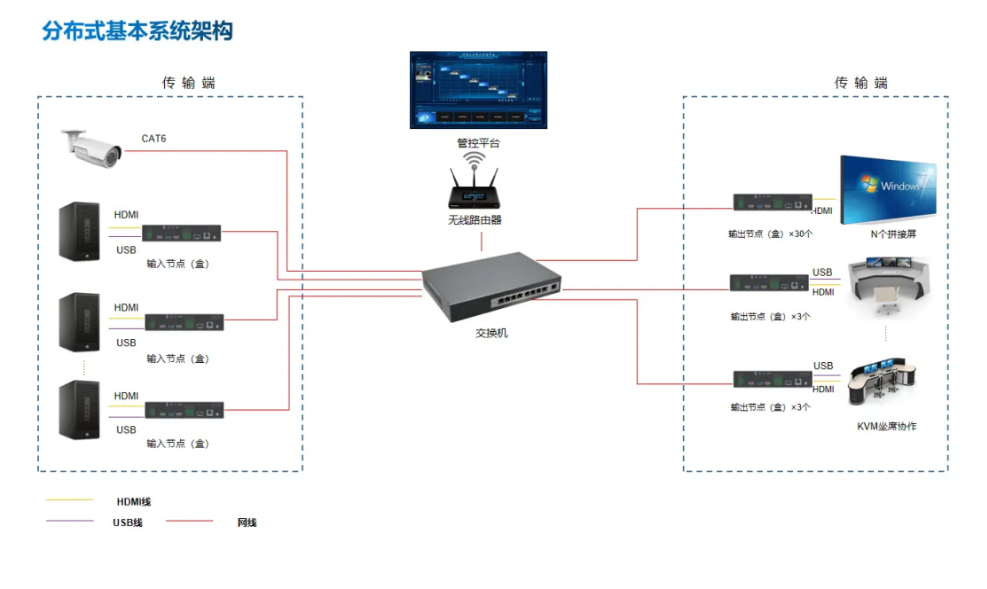

深蕾半導體IP-KVM產品方案解析

為何原理圖比對是電子設計中不可或缺的功能?

使用DLP9000在切換不同的灰度圖時,會出現(xiàn)一部分的延遲以后才可以完整的顯示圖像,為什么?

DLPC3478固件加載只有前面一部分是怎么回事?

DAC348X EVM的I路輸出電路,畫圈的那一部分有什么作用?0L電感L40有什么作用?

BGA芯片封裝:現(xiàn)代電子產業(yè)不可或缺的技術瑰寶

解鎖網(wǎng)絡新體驗:住宅靜態(tài)IP的奇妙之旅

0.5mm層疊封裝應用處理器的PCB設計指南,第一部分

0.4毫米層疊封裝(PoP)的PCB設計指南,第一部分

什么是觸摸芯片:現(xiàn)代電子產品不可或缺的關鍵技術解析

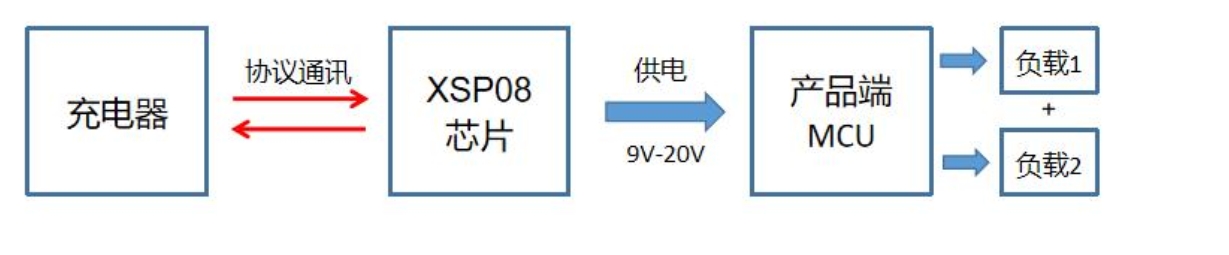

多口適配器-現(xiàn)代生活中的不可或缺的一部分

言驗證通常構成整個驗證IP開發(fā)周期不可或缺的一部分

言驗證通常構成整個驗證IP開發(fā)周期不可或缺的一部分

評論