IBM最近宣布,位于紐約Albany的IBM Research實(shí)驗(yàn)室采用納米片(nanosheet)技術(shù)研制出2nm芯片,據(jù)稱在150mm2的平面上(約指甲蓋大小)嵌入了 500 億個(gè)晶體管,平均每平方毫米3.3 億個(gè)。而臺積電和三星的7納米芯片容納的晶體管數(shù)量大約在每平方毫米9,000萬個(gè);三星的5LPE為1.3億個(gè);臺積電的5納米芯片則是1.7億個(gè)。

IBM 2nm芯片的性能/功耗提升靠什么技術(shù)?

據(jù)IBM Research負(fù)責(zé)人Darío Gil稱,采用2納米工藝制造的處理器相比現(xiàn)在許多筆記本電腦及手機(jī)使用的主流7納米處理器速度提升45%,能效提高75%。也就是說,其2納米架構(gòu)可以在與現(xiàn)有7納米相同的性能下,僅耗用25%的電力。以最新的智能手機(jī)為例,可能四天才需要充一次電。而在筆記本電腦、自動駕駛等對能耗不敏感的使用場景下,則能帶來更高的算力。

這種2nm芯片還可用于數(shù)據(jù)中心、太空探索、人工智能、5G、6G 乃至于量子計(jì)算。但要真正投片量產(chǎn)還要等待幾年時(shí)間,估計(jì)至少要到2024年。大約4年前,IBM宣布與合作伙伴格芯和三星共同開發(fā)出采用納米片晶體管結(jié)構(gòu)的5納米芯片。

據(jù)稱在指甲蓋大小的面積上集成了30億個(gè)晶體管,而其前一代7納米測試芯片(于2015年發(fā)布)的容量為20億個(gè)晶體管。然而,今年下半年才能看到IBM的7納米芯片投入商用。

雖然IBM不再自己生產(chǎn)芯片(將其晶圓廠賣給了格芯),但位于紐約Albany的IBM Research實(shí)驗(yàn)室仍繼續(xù)研發(fā)最前沿的半導(dǎo)體制造技術(shù),7nm、5nm和2nm芯片都是業(yè)界率先研制成功的,而且都是采用這種業(yè)界通常稱為柵極全環(huán)繞型(GAA,Gate-All-Around)的納米片(nanosheet)技術(shù)。

從Planar到FinFET,再到GAA

可以容納數(shù)十億個(gè)晶體管的先進(jìn)微處理器無疑是世界上最復(fù)雜的系統(tǒng)之一,但其本質(zhì)上卻是一個(gè)非常簡單的單元:晶體管。無論晶體管數(shù)量多大,它們幾乎都是相同的,功能上就是一個(gè)簡單的開關(guān)。因此,提高性能并增加這些晶體管的密度是使微處理器及其驅(qū)動的計(jì)算機(jī)高效工作的最直接方法。這就是多年來摩爾定律正常運(yùn)作的前提,但現(xiàn)在幾乎要走到盡頭了。

開發(fā)更小且更好的晶體管在技術(shù)上越來越困難,而且制造成本越來越高。目前,全世界只有英特爾、三星和臺積電(TSMC)三家公司能夠生產(chǎn)7nm及以下工藝的芯片。雖然臺積電和三星仍在不斷往5nm、3nm甚至2nm工藝進(jìn)軍。

但它們已經(jīng)不是傳統(tǒng)意義上晶體管線寬的準(zhǔn)確物理概念了,只是廠商在最先進(jìn)工藝競賽中使用的營銷代號而已。盡管如此,它們?nèi)匀豢梢苑从吵?a target="_blank">集成電路中晶體管的結(jié)構(gòu)特征和小型化程度。

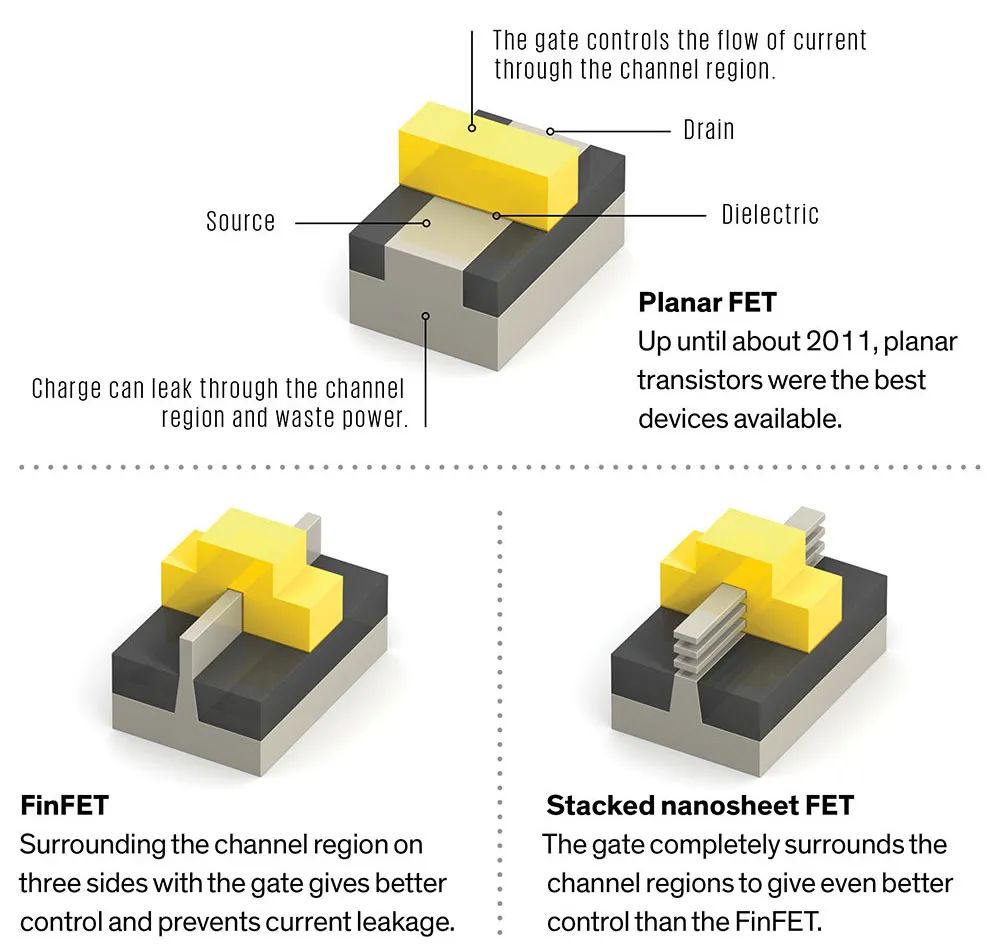

自1959年問世以來,金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)一直采用相同的基本結(jié)構(gòu):柵極疊層、溝道區(qū)、源極和漏極。而且MOSFET的源極和漏極基本放置于硅平面上,柵極疊層位于溝道區(qū)的正上方,這就是沿用多年的平面型FET(Planar FET)。然而,這種結(jié)構(gòu)的一個(gè)缺點(diǎn)是電荷有可能通過溝道區(qū)域泄漏,導(dǎo)致晶體管永遠(yuǎn)不會完全截止,從而浪費(fèi)功率并產(chǎn)生熱量。

為了阻止不必要的電荷流,必須將溝道區(qū)域做得更薄,以限制電荷流動的路徑,而且柵極需要在更多側(cè)面包圍溝道。為解決這一問題,加州大學(xué)伯克利分校的胡正明教授于2000年提出了鰭式場效晶體管(FinFET)方案。

在這種設(shè)計(jì)中,溝道區(qū)域在其側(cè)面向上傾斜,從而在源極和漏極之間形成一個(gè)細(xì)長的硅鰭,為電流提供了更寬的路徑。然后將柵極和電介質(zhì)覆蓋在鰭片的三個(gè)側(cè)面,將硅鰭包圍起來。2011年,英特爾開始利用FinFET結(jié)構(gòu)生產(chǎn)22納米的芯片。這一創(chuàng)新的晶體管結(jié)構(gòu)把摩爾定律的有效期延長了數(shù)十年,如今22納米以下的工藝都是采用FinFET結(jié)構(gòu)。

從Planar FET到FinFET再到疊層納米片F(xiàn)ET的演進(jìn)(來源:IEEE SPECTRUM)

FinFET無疑取得了巨大的成功,自2011年以來它一直是摩爾定律最后階段中先進(jìn)數(shù)字邏輯芯片的主動力。英特爾、三星和臺積電等公司都在繼續(xù)使用FinFET研發(fā)7nm和5nm的芯片。但是,到了3nm節(jié)點(diǎn),F(xiàn)inFET有點(diǎn)力不從心了。

FinFET雖然解決了平面型FET的電荷泄漏問題,但它也引入了新的設(shè)計(jì)限制。要知道,為達(dá)到最佳效果,我們必須在晶體管的速度、功耗、制造復(fù)雜性和成本之間做出取舍。這種折衷與溝道寬度(Weff )有很大關(guān)系,更大的寬度意味著可以驅(qū)動更多的電流并更快地開關(guān)晶體管。但這需要更復(fù)雜、成本更高的制造工藝。

對于平面型FET結(jié)構(gòu),可以簡單地通過調(diào)整溝道的幾何形狀來實(shí)現(xiàn)折衷。但是FinFET的鰭片卻沒有這樣的靈活性,因?yàn)檫B接晶體管以形成電路的金屬互連位于晶體管自身上方的層中。因此,在不干擾互連層的前提下,晶體管鰭片的高度(相當(dāng)于平面型FET的寬度)實(shí)際上不能有很大的變化。如今,芯片設(shè)計(jì)人員通過設(shè)計(jì)具有多個(gè)鰭的晶體管來解決這個(gè)問題。

FinFET的另一個(gè)缺點(diǎn)是,其柵極僅在三個(gè)側(cè)面圍繞矩形硅鰭,而底側(cè)仍與硅主體相連。當(dāng)晶體管關(guān)閉時(shí),仍有一些泄漏電流流過。業(yè)界研究人員認(rèn)為,要獲得對溝道區(qū)域的完全控制,柵極需要將其四面完全包圍。

從1990年開始,研究人員就著手將此想法付諸實(shí)際,并研制出首個(gè)完全圍繞溝道區(qū)域的柵極硅器件。從那以后,更多的研究人員投入研發(fā)所謂的柵極全環(huán)繞型(GAA)器件。到2003年,一直尋求最小化電流泄漏的研究人員將溝道區(qū)域變成了一條狹窄的納米線(nanowire),該納米線連接源極和漏極,其四周都被柵極包圍了。

那么,是否可以基于全包圍的納米線設(shè)計(jì)新的晶體管呢?這時(shí)溝道寬度又成了攔路虎。雖然較細(xì)的導(dǎo)線幾乎完全阻止了電子的逃逸,在晶體管處于關(guān)閉狀態(tài)時(shí)確實(shí)達(dá)到了真正的關(guān)閉。但是,當(dāng)晶體管導(dǎo)通時(shí),它也阻礙了電子的流動,從而限制了電流并減慢了開關(guān)速度。

如果將納米線彼此堆疊起來,就可以獲得更大的Weff,從而獲得更多電流。2004年三星研發(fā)出了這種配置的結(jié)構(gòu),稱為多橋溝道FET。但是它有一些局限性,例如FinFET的鰭堆疊不能太高,否則會干擾互連層。另外,每增加一條納米線就會增加晶體管的電容,從而減慢晶體管的開關(guān)速度。最后,由于制造非常窄的納米線特別復(fù)雜,其邊緣常常變得非常粗糙,這種表面粗糙度又會阻礙電荷載流子的速度。

2006年,法國CEA-Leti的研發(fā)人員想出了一個(gè)更好的主意。他們沒有使用一堆納米線來橋接源極和漏極,而是采用了一堆硅薄片。這個(gè)想法是在較小的晶體管中增加溝道的寬度,同時(shí)保持對泄漏電流的嚴(yán)格控制,從而提供性能更好的低功耗器件。IBM Research在此基礎(chǔ)上更進(jìn)一步,證明由堆疊納米片(stacked nanosheets)構(gòu)成的晶體管在同樣的面積上可以提供比FinFET更寬的Weff。

此外,納米片的設(shè)計(jì)又提供了一個(gè)額外的好處:它恢復(fù)了從Planar FET向FinFET過渡時(shí)喪失的靈活性。既可以讓納米片變寬以增加電流,也可以使其變窄以限制功耗。IBM Research將它們堆疊成三層,大小從8-50 nm不等,并于2017年宣布開發(fā)出基于這種納米片結(jié)構(gòu)的5nm芯片。

GAA能否取代FinFET的主導(dǎo)地位?

在這種新型晶體管結(jié)構(gòu)的開發(fā)過程中,有各種各樣的名稱出現(xiàn),比如柵極全環(huán)繞型(GAA)、多橋溝道、納米束,以及半導(dǎo)體學(xué)術(shù)研究界通常叫的“納米片”。叫什么名字不重要,重要的是這種設(shè)計(jì)不僅僅是邏輯芯片的下一個(gè)晶體管結(jié)構(gòu),它可能是摩爾定律終結(jié)前的最后一個(gè)。

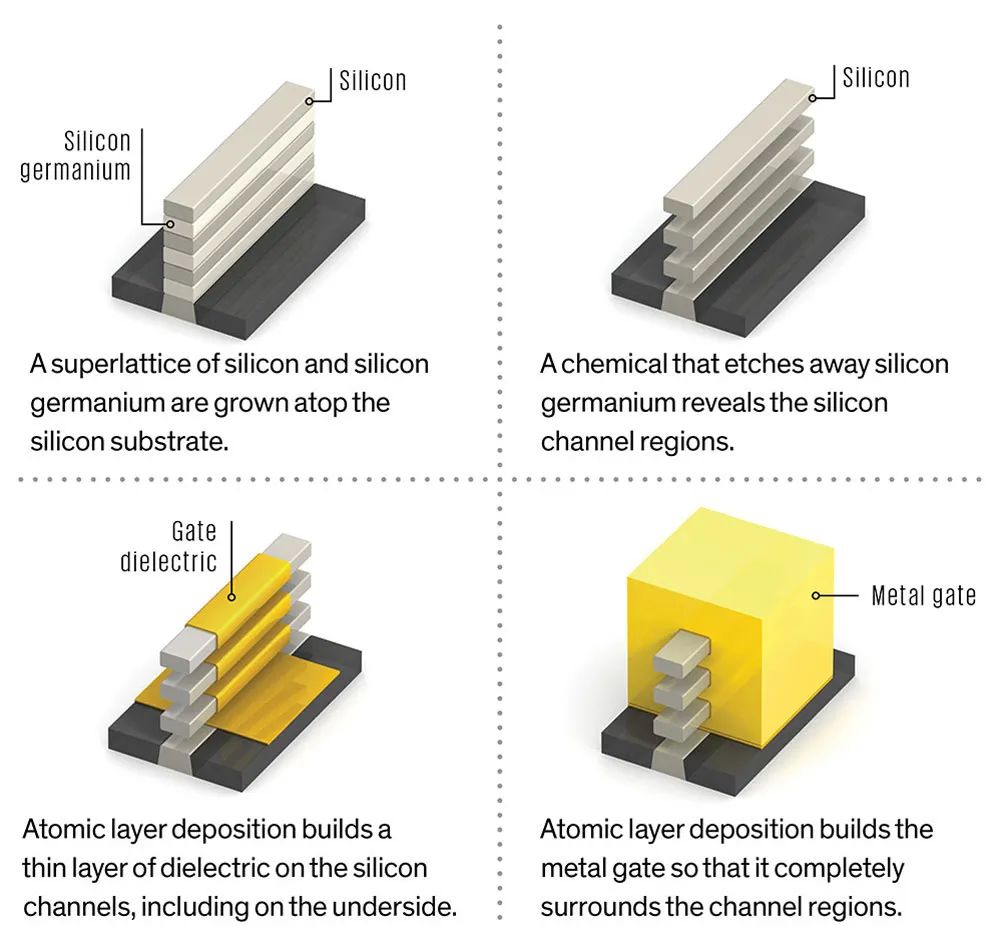

那么,如何制造納米片呢?制造納米片需要補(bǔ)償層、選擇性化學(xué)蝕刻劑,以及先進(jìn)的原子精確沉積技術(shù)。

納米片設(shè)計(jì)結(jié)構(gòu)插圖:Emily Cooper

基于納米片結(jié)構(gòu)的晶體管又如何構(gòu)建呢?考慮到大多數(shù)半導(dǎo)體制造工藝從硅的頂部垂直向下切割或從裸露的表面垂直向上填充,這似乎是一項(xiàng)艱巨的任務(wù)。納米片需要去除其他材料層之間的材料,并用金屬和電介質(zhì)填充間隙。

其中的關(guān)鍵是構(gòu)建所謂的超晶格--一種由兩種材料組成的周期性分層晶體。它可以是硅和硅鍺,研究人員已經(jīng)制作出了19層的超晶格,但是所涉及的機(jī)械應(yīng)力以及電容讓我們認(rèn)識到不應(yīng)該使用這么多的層。在生長了適當(dāng)數(shù)量的層之后,我們使用一種選擇性腐蝕硅鍺但對硅無作用的化學(xué)物質(zhì),僅留下硅納米片作為源極和漏極之間的懸浮橋。

構(gòu)建好硅納米片的溝道區(qū)域后,就需要填充間隙,首先用電介質(zhì),然后用金屬環(huán)繞溝道,以形成柵極疊層。這兩個(gè)步驟都是通過稱為“原子層沉積”的工藝完成的,這種工藝僅在十年前才引入半導(dǎo)體制造領(lǐng)域。

納米片設(shè)計(jì)的驚人之處是,它可能延續(xù)摩爾定律的有效壽命,甚至超過溝道中硅的使用時(shí)間,但是首先要解決散熱問題。每代工藝節(jié)點(diǎn)的晶體管密度仍在不斷增加,但芯片可以合理散熱的功率密度近十年來一直保持在每平方厘米100瓦左右。

芯片制造商已竭盡全力避免超過這一上線。為了降低熱量,時(shí)鐘速率不得超過4 GHz,于是處理器廠商轉(zhuǎn)向多核設(shè)計(jì),期望幾個(gè)較慢的處理器內(nèi)核可以完成與單個(gè)快速處理器內(nèi)核相同的工作,同時(shí)產(chǎn)生的熱量更少。然而,如果想再次提高時(shí)鐘速度,我們就需要比硅本身的能效更高的晶體管。

一種潛在的解決方案是將新材料引入溝道區(qū)域,例如鍺或由元素周期表的第III列和第V列的元素組成的半導(dǎo)體,例如砷化鎵。電子在其中一些半導(dǎo)體中的移動速度可以快10倍以上,從而使得由這些材料制成的晶體管的開關(guān)速度更快。更重要的是,由于電子運(yùn)動更快,器件可以在較低的電壓下工作,從而提高了能效,并減少了熱量的產(chǎn)生。

受早期關(guān)于納米線晶體管和超晶格結(jié)構(gòu)研究的啟發(fā),普渡大學(xué)的Peide Ye教授使用砷化銦鎵(III-V半導(dǎo)體)研制出一種三納米片器件,其結(jié)果好于預(yù)期。這種納米片晶體管對于每微米的溝道寬度允許9,000微安的電流。這是當(dāng)今最好的平面型InGaAs MOSFET的三倍左右。如果制造工藝得到進(jìn)一步改善,這種器件的性能仍然可以提高。通過堆疊更多的納米片,我們有可能將性能提高10倍以上。因此,這一設(shè)計(jì)思路對未來的高速和節(jié)能型集成電路的發(fā)展有著重要的指導(dǎo)意義。

當(dāng)然,InGaAs并不是未來納米片晶體管的唯一選擇。研究人員還在探索其他具有高遷移率載流子的半導(dǎo)體,包括鍺、砷化銦和銻化鎵。例如,新加坡國立大學(xué)的研究人員最近使用由砷化銦制成的N型晶體管和由銻化鎵制成的P型晶體管的組合,構(gòu)建了完整的CMOS IC。然而,一種可能更簡單的解決方案是使用摻雜的鍺,因?yàn)殡娮雍驼姾奢d流子(空穴)通過鍺的速度都非常快。

總而言之,無論采用什么化合物材料,堆疊納米片似乎是構(gòu)造未來晶體管的最佳方法。芯片制造商已經(jīng)對該技術(shù)有足夠的信心,相信在不久的將來會將其納入設(shè)計(jì)規(guī)劃路線圖。隨著高遷移率半導(dǎo)體材料的集成,納米片晶體管將滲透到我們的未來生活,這是任何人現(xiàn)在就可以預(yù)見到的。

GAA之爭已經(jīng)開始

TSMC計(jì)劃在2022年第三季度為蘋果公司提供基于3nm FinFET的芯片,而三星計(jì)劃在2022年第四季度開始量產(chǎn)其第一代基于3nm GAA晶體管的芯片。在臺積電的規(guī)劃路線圖上,這家全球最大的晶圓代工廠商計(jì)劃將FinFET擴(kuò)展到3nm,然后在2023/2024年轉(zhuǎn)移到2nm GAA。相比之下,三星則直接從5nm FinFET轉(zhuǎn)移到3nm GAA。

英特爾還在開發(fā)可能用于其5nm節(jié)點(diǎn)的納米片F(xiàn)ET,但目前尚不清楚英特爾的5nm芯片何時(shí)發(fā)布,但短期內(nèi)難以縮小與臺積電和三星的工藝差距。至少在未來三年內(nèi),三星和臺積電的總支出將超過500億美元,對于任何一家公司來說,要在最先進(jìn)的邏輯處理技術(shù)上趕上這兩家公司都是極其困難的。

但是,美國的英特爾在其新任CEO的領(lǐng)導(dǎo)下,趕上甚至超越還是有可能的。也許,新型的GAA(或者納米片)晶體管是拯救英特爾和摩爾定律的最后一根稻草。

編輯:jq

-

芯片

+關(guān)注

關(guān)注

459文章

52481瀏覽量

440615 -

CMOS

+關(guān)注

關(guān)注

58文章

6021瀏覽量

238831 -

晶體管

+關(guān)注

關(guān)注

77文章

10018瀏覽量

141608 -

納米

+關(guān)注

關(guān)注

2文章

711瀏覽量

38871

原文標(biāo)題:干貨 | IBM 2nm芯片采用的GAA技術(shù)能否替代FinFET而延續(xù)摩爾定律的神話?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

臺積電2nm良率超 90%!蘋果等巨頭搶單

FinFET與GAA結(jié)構(gòu)的差異及其影響

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

電力電子中的“摩爾定律”(1)

瑞沃微先進(jìn)封裝:突破摩爾定律枷鎖,助力半導(dǎo)體新飛躍

手機(jī)芯片進(jìn)入2nm時(shí)代,首發(fā)不是蘋果?

混合鍵合中的銅連接:或成摩爾定律救星

聯(lián)發(fā)科采用AI驅(qū)動Cadence工具加速2nm芯片設(shè)計(jì)

石墨烯互連技術(shù):延續(xù)摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

IBM與Rapidus在多閾值電壓GAA晶體管技術(shù)的新突破

對話郝沁汾:牽頭制定中國與IEEE Chiplet技術(shù)標(biāo)準(zhǔn),終極目標(biāo)“讓天下沒有難設(shè)計(jì)的芯片”

IBM 2nm芯片采用的GAA技術(shù)能否替代FinFET而延續(xù)摩爾定律的神話?

IBM 2nm芯片采用的GAA技術(shù)能否替代FinFET而延續(xù)摩爾定律的神話?

評論