目前,雖然基于C/C++等高層次綜合相較于手寫(xiě)RTL層級(jí)HDL語(yǔ)言已大幅提升了開(kāi)發(fā)效率,但隨著相關(guān)技術(shù)的不斷進(jìn)步,以及算法迭代的日益頻繁,人們似乎并不滿足于此。

不少剛剛接觸到Pynq的用戶第一個(gè)問(wèn)號(hào)

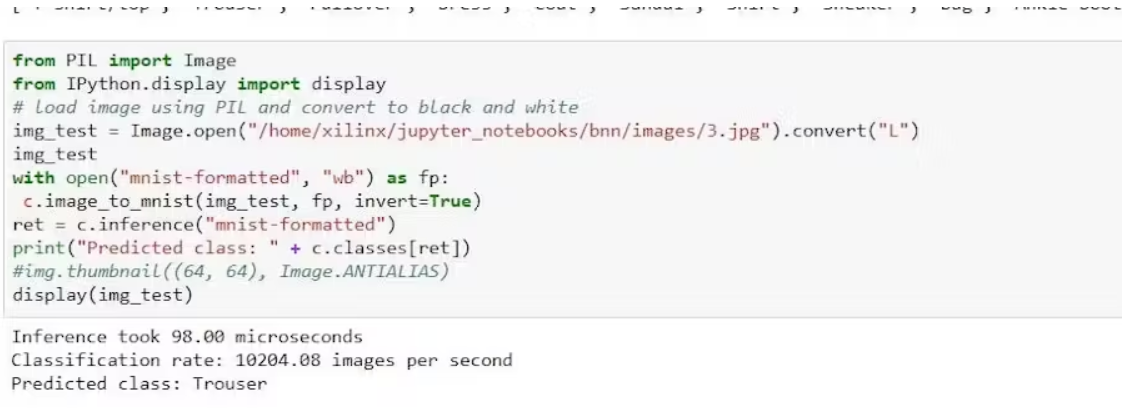

在Pynq的FAQ中,我們強(qiáng)調(diào)的第一個(gè)重點(diǎn)就是PYNQ是一個(gè)開(kāi)源框架而不是一個(gè)直接用Python編程FPGA的工具。但是,在不遠(yuǎn)的將來(lái),我們也許就要修改這條FAQ了。

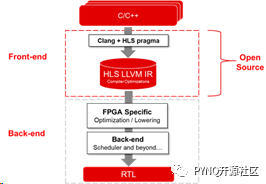

因?yàn)樵?月28日,Vitis HLS工具前端開(kāi)源了!!!

這是Xilinx的開(kāi)源戰(zhàn)略和承諾的一部分,通過(guò)Vitis HLS工具鏈前端開(kāi)源可以

Add support for new high-level languages beyond C/C++ and OpenCL

Add new domain-specific optimization pragmas or compiler directives

Customize the transformations to the LLVMIR (new LLVM passes)

這意味著,軟硬件開(kāi)發(fā)人員可以靈活地使用標(biāo)準(zhǔn)的 Clang / LLVM 基礎(chǔ)架構(gòu),支持自由擴(kuò)展,也可以定制高層次綜合 (HLS) 編譯過(guò)程的前端。

例如,自定義語(yǔ)言支持和全新特定于應(yīng)用的編譯器指令,以及更多的可能性。

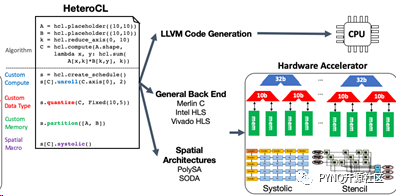

研究人員早就在開(kāi)始探索增加Python高層次綜合。例如2019年,Themefisher和康奈爾大學(xué)聯(lián)合推出了HeteroCL。

HeteroCL是一種編程基礎(chǔ)結(jié)構(gòu),由基于Python的域特定語(yǔ)言(DSL)和編譯流程組成,其編譯器在CPU上生成LLVM代碼。

因此可通過(guò)結(jié)合最新的HLS優(yōu)化(例如用于脈動(dòng)陣列的PolySA和用于模板的SODA與數(shù)據(jù)流體系結(jié)構(gòu)),產(chǎn)生高效的空間體系結(jié)構(gòu)。

將來(lái)要發(fā)生的事情,大家應(yīng)該都有自己的想象空間了

編輯:lyn

-

FPGA

+關(guān)注

關(guān)注

1643文章

21974瀏覽量

614381 -

python

+關(guān)注

關(guān)注

56文章

4825瀏覽量

86237 -

PYNQ

+關(guān)注

關(guān)注

4文章

62瀏覽量

3053

原文標(biāo)題:PYNQ框架下用Python編程FPGA不是夢(mèng)-Vitis HLS前端開(kāi)源

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Vivado HLS設(shè)計(jì)流程

數(shù)字電路設(shè)計(jì)中:前端與后端的差異解析

熱門(mén)前端框架:引領(lǐng)現(xiàn)代 Web 開(kāi)發(fā)的潮流

使用ADS1274 ADC進(jìn)行前端信號(hào)采集,前端信號(hào)調(diào)理過(guò)程中是否還需要設(shè)計(jì)AA Filter?

使用AMD Vitis進(jìn)行嵌入式設(shè)計(jì)開(kāi)發(fā)用戶指南

前端的作用

全新AMD Vitis統(tǒng)一軟件平臺(tái)2024.2版本發(fā)布

AMD Vitis Unified Software Platform 2024.2發(fā)布

基于PYNQ和機(jī)器學(xué)習(xí)探索MPSOC筆記

前端總線頻率怎么看的

前端總線頻率的類型是什么?

前端總線是屬于什么總線

優(yōu)化 FPGA HLS 設(shè)計(jì)

使用PYNQ訓(xùn)練和實(shí)現(xiàn)BNN

一種在HLS中插入HDL代碼的方式

淺談PYNQ中的Vitis HLS前端開(kāi)源

淺談PYNQ中的Vitis HLS前端開(kāi)源

評(píng)論