DPU600是DapuStor(大普微)在業(yè)內(nèi)首創(chuàng)的智能存儲SoC,基于最新的12nm FinFET工藝,可作為SSD主控提供業(yè)界領(lǐng)先的性能,還集成了可計算存儲平臺,用于ASIC加速的機(jī)器學(xué)習(xí)架構(gòu)等。

上期講到得益于DPU600內(nèi)置的應(yīng)用處理器平臺,可以將DPU600作為存算一體化固態(tài)硬盤(PIS-SSD),并討論了相關(guān)架構(gòu)和實現(xiàn)技術(shù)。本期小編將進(jìn)一步討論計算存儲的功能,這是小編又付出N個雞腿后,從研發(fā)小伙伴們手里“炸”出來的干貨。

同樣地,小編需要先重復(fù)一下背景:

在大數(shù)據(jù)應(yīng)用的背景下,海量的數(shù)據(jù)傳輸占用了各類總線、網(wǎng)絡(luò)帶寬,與此同時,固態(tài)硬盤(SSD)本身含有的CPU的算力也越來越強(qiáng)。為了減少大數(shù)據(jù)量的傳輸,從而衍生出各類對存儲計算一體化(PIS-Processing In Storage)的需求,即在數(shù)據(jù)端固態(tài)硬盤內(nèi)進(jìn)行計算處理,也經(jīng)常稱之為“近存儲計算”,僅傳輸結(jié)果和部分?jǐn)?shù)據(jù),從而減少海量數(shù)據(jù)傳輸,減輕總線和網(wǎng)絡(luò)負(fù)載(Offloading)。

讀者或許想說:這些上次說過了?

小編……,打Patch:雖然DPU600內(nèi)置了PIS模塊,但是需求永遠(yuǎn)是在變化和前進(jìn)的(研發(fā)小伙伴最頭痛的需求的快速變化),那么DPU600 如何應(yīng)對?特別是特定計算要求的情況下,如何快速而靈活地滿足需求?

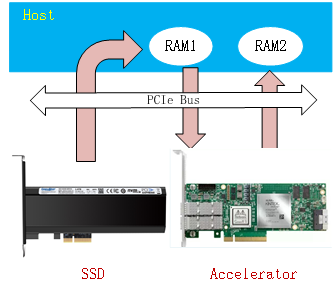

首先說說現(xiàn)有的技術(shù),如圖1,是一種計算靠近存儲的最通用方法:專用加速卡(計算模塊)和存儲都放置在PCIe總線,Host控制數(shù)據(jù)流在PCIe總線流動。顯然,此種方式對IO(PCIe,RAM)的占用是非常的高。

圖1

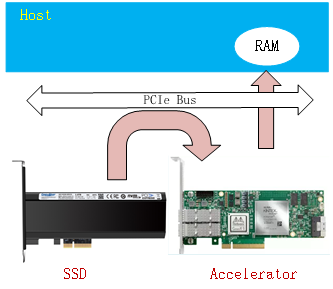

有瓶頸就有新的方案產(chǎn)生,業(yè)界有團(tuán)隊開始研發(fā)新的方案,如圖2,即P2P Connection方案(此P2P不是坑各位錢的網(wǎng)絡(luò)金融,類似各位下載用過的P2P,Peer2Peer),通過PCIe Bus,加速卡和存儲器之間直接傳輸數(shù)據(jù),以此Off Loading CPU和RAM的負(fù)載。

圖2

說到這里,大家想到了DPU600肯定有什么東東,可以在此類應(yīng)用需求上發(fā)揮作用?沒錯,DapuStor正在探索在DPU600上實現(xiàn)一種存儲計算一體的固態(tài)硬盤(SSD)。

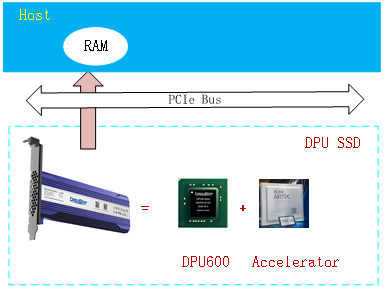

圖3

先看一下,我們的設(shè)計基于如圖3,相對于圖1,2,其思路是:將所有運(yùn)算放置在固態(tài)硬盤(SSD),其中為了彌補(bǔ)控制器本身計算能力擴(kuò)展性有限的弱點(diǎn),引入了加速器設(shè)計,并集成到一個PCB內(nèi)。這樣,可以進(jìn)一步減輕負(fù)載(Offloading)到存儲器(固態(tài)硬盤)內(nèi),相對于P2P方案,將計算加速器放置在SSD內(nèi)(主機(jī)視角),從而不走主機(jī)上PCIe Bus。

為何如此設(shè)計?

1. 由于DPU600具有雙PCIe模塊,可以同時滿足和主機(jī)通信(PCIe/NVMe),以及和加速器通信(PCIe/DPU-LINK),即滿足數(shù)據(jù)的存儲和計算兩種通路需求,一個接口用于數(shù)據(jù)存儲,另一個接口用于數(shù)據(jù)計算。其中運(yùn)用DPU600中專門設(shè)計的DPU-LINK技術(shù),減低傳輸延時,提升性能。

2. 由于DapuStor在存儲計算深耕多年,形成了諸多存儲計算的IP,可以應(yīng)用到加速器(FPGA)里面。根據(jù)各自不同特性系統(tǒng)的需求,可以配置不同算法模塊。

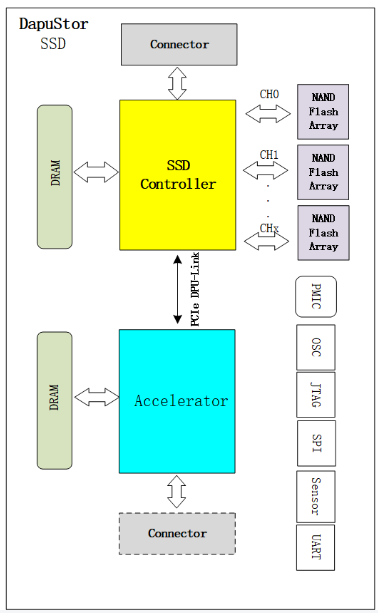

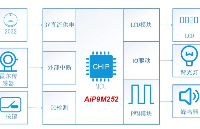

如圖4,是我們設(shè)計的框架圖:上半部分和普通的固態(tài)硬盤基本一致,下半部分是加速器的部分,目前是以FPGA為主體,其中由于計算的需求,可單獨(dú)設(shè)置DRAM。但對主機(jī)而言保持一個接口,當(dāng)然為了兼容性考慮,也備份了加速器的PCIe接口,便于擴(kuò)展主機(jī)和加速器之間的通信。

圖4

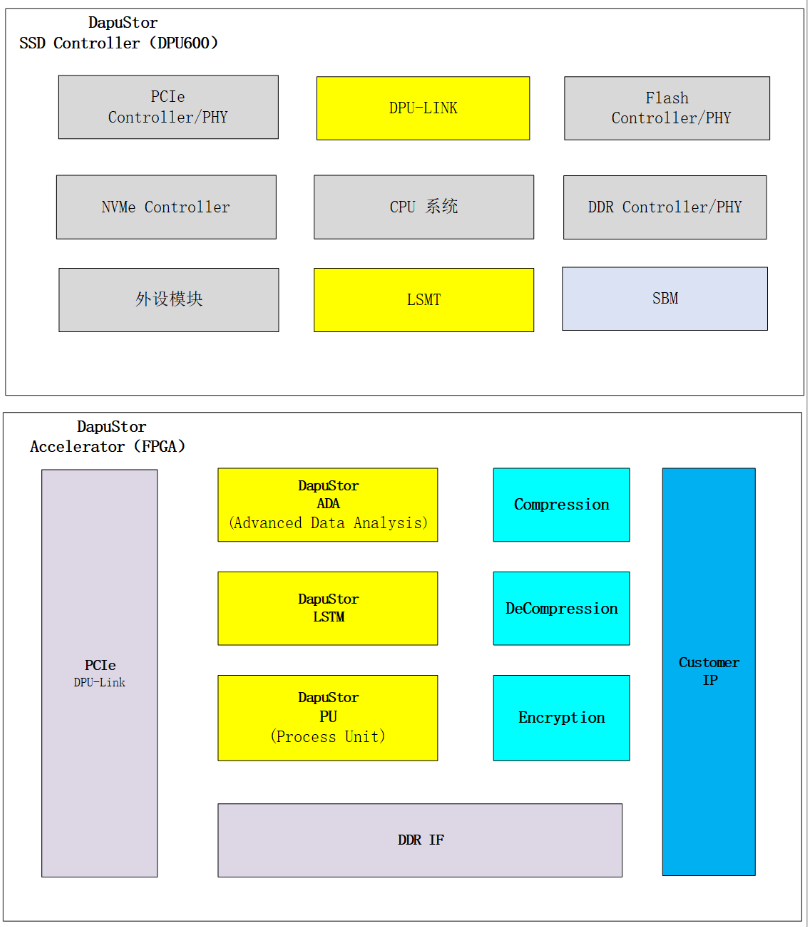

大家可能比較興趣的技術(shù)點(diǎn): DPU600和FPGA的內(nèi)部設(shè)計。受限于小編手里雞腿有限,只能“炸”到基本模塊框架圖,如圖5。上圖是DPU600內(nèi)部相關(guān)模塊構(gòu)成,下圖是FPGA相關(guān)模塊構(gòu)成。

圖5

小編根據(jù)模塊框圖,這里把關(guān)鍵模塊進(jìn)行探討一下:

1. DPU600存儲系統(tǒng),包括

PCIe Controller/PHY和NVMe Controller,應(yīng)用于前端模塊(FE)和主機(jī)通信協(xié)議棧,命令數(shù)據(jù)收發(fā)的硬件處理。

NAND Flash Controller/PHY,應(yīng)用于后端模塊(BE)閃存數(shù)據(jù)讀寫和相關(guān)閃存命令的硬件處理;

DDR Controller/PHY外連DRAM設(shè)備,應(yīng)用于數(shù)據(jù)緩存。

CPU系統(tǒng),包含MMU,CCI等典型應(yīng)用處理器的功能模塊,用于運(yùn)行固件和Linux 操作系統(tǒng);

其中和計算相關(guān)模塊:

LSTM,是基于神經(jīng)網(wǎng)絡(luò)算法的計算模塊,可以用于預(yù)測IO趨勢,優(yōu)化SSD性能。

DPU-LINK,是基于PCIe特性的硬件Buffer傳輸管理模塊,用于優(yōu)化PCIe數(shù)據(jù)傳輸管理,減少數(shù)據(jù)傳輸延時。

2.FPGA加速器計算系統(tǒng),包括:

ADA(數(shù)據(jù)分析處理),用硬件實現(xiàn)數(shù)據(jù)的預(yù)分析和處理,包括但不限于:

ASCII數(shù)據(jù)轉(zhuǎn)換(dconv)功能

正則匹配字符串查找(grep)功能

預(yù)排序處理(sort)功能

LSTM,是基于神經(jīng)網(wǎng)絡(luò)算法的計算模塊,是DPU600內(nèi)LSTM的強(qiáng)化版本。

PU, 是數(shù)據(jù)計算處理專用單元,優(yōu)化數(shù)據(jù)處理進(jìn)程。

其他通用計算模塊,包括但不限于:

壓縮(Compresssion)和解壓(Decompression),

另外引入客戶IP接口,相關(guān)處理包括但不限于數(shù)據(jù)搜索(Search),數(shù)據(jù)比較(Compare),數(shù)據(jù)標(biāo)簽(Tag),數(shù)據(jù)索引(Index)。

小編在這里Copy過來:一種計算應(yīng)用場景,在DPU600+Accelerator的加持下,下面所述的計算需求更容易Offloading到計算存儲系統(tǒng)內(nèi)。

SQL Query一種典型的數(shù)據(jù)庫應(yīng)用,傳統(tǒng)的所有步驟步驟均是在主機(jī)計算完成。在引入存算一體化存儲器之后,可以把大部分查詢計算移入到存取器內(nèi)(加速器內(nèi)),如圖6,可以大大減少IO傳輸,是一種典型的 “近存儲計算”應(yīng)用。

原文標(biāo)題:SSD主控芯片, 除了做SSD還能干點(diǎn)啥?- III

文章出處:【微信公眾號:大普微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52174瀏覽量

436132 -

SSD

+關(guān)注

關(guān)注

21文章

2950瀏覽量

119107

發(fā)布評論請先 登錄

SSD主控芯片格局已定?一家國內(nèi)企業(yè)躋身全球第二,主控江湖劍指PCIe5.0

QLC SSD在數(shù)據(jù)中心的用途

慧榮科技車用級SSD主控芯片獲得ASPICE CL3國際認(rèn)證

慧榮科技企業(yè)級主控芯片SM8366為企業(yè)級SSD存儲芯片注入新動力

慧榮正在開發(fā)4nm PCIe 6.0 SSD主控芯片

芯盛智能與中芯國際發(fā)布SATA企業(yè)級SSD主控芯片XT6160

固態(tài)硬盤控制芯片壞了,數(shù)據(jù)能恢復(fù)嗎

顯示器主控芯片和電視主控芯片的區(qū)別

機(jī)器人主控器的主控芯片在功能上與什么相似

SSD主控芯片還有哪些用途?

SSD主控芯片還有哪些用途?

評論