隨著芯片技術(shù)的不斷發(fā)展,特別是芯片工藝水平的提升,芯片規(guī)模越來越大,這也為芯片邏輯功能驗證帶來了很大的挑戰(zhàn)。如何保證產(chǎn)品上市時間(TimetoMarket),快速完成功能驗證和達成較高的覆蓋率,已成為驗證進程管理的棘手問題。本文主要跟小伙伴們聊一聊智能跟蹤SoC驗證進度的方法。

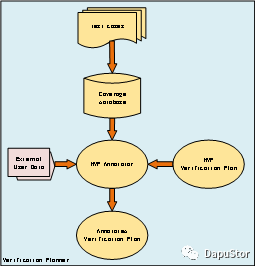

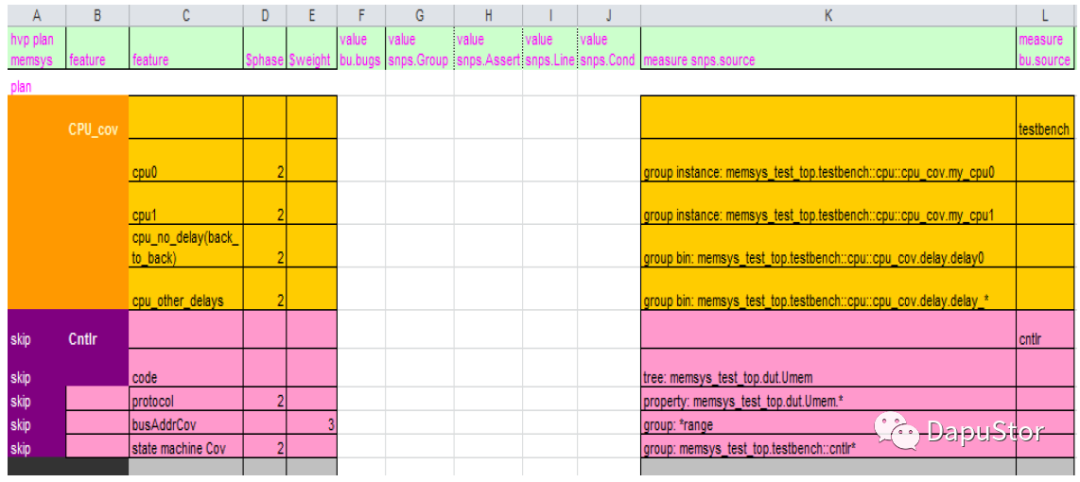

EDA工具兩大巨頭Synopsys和Cadence都有自己的驗證計劃工具,分別是Synopsys公司的VerificationPlanner和Cadence的vmanager,兩者各有千秋。今天我們主要針對的是Synopsys的層次化驗證計劃工具。該工具采用自定義的描述語言HVP(Hierarchical Verification Plan),層次化地描述驗證計劃,并在驗證計劃的實施過程中,通過測試數(shù)據(jù)結(jié)果,反標回驗證計劃,根據(jù)產(chǎn)生相應的狀態(tài)報告,可以有效地追蹤驗證的整個進程。其基本流程如圖1所示。

圖1:HVP基本流程

該流程需要驗證人員首先編寫驗證計劃,驗證計劃通常需要Synopsys提供的另一種工具Verdi或DVE編輯HVP文件,或者直接采用office工具Excel編輯XML格式文件。在項目驗證計劃中會包含測試計劃、功能覆蓋率計劃、斷言覆蓋計劃、代碼覆蓋率計劃等等。下面將介紹HVP是如何編寫來映射我們上述提到的各種計劃的。

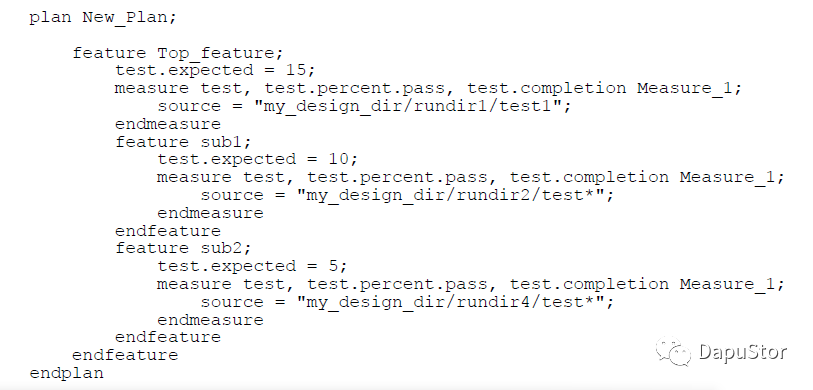

驗證計劃有自己的.hvp格式,如圖2 HVP描述示例。該文件可以比較容易的通過Verdi生成模板。

圖2:HVP描述示例

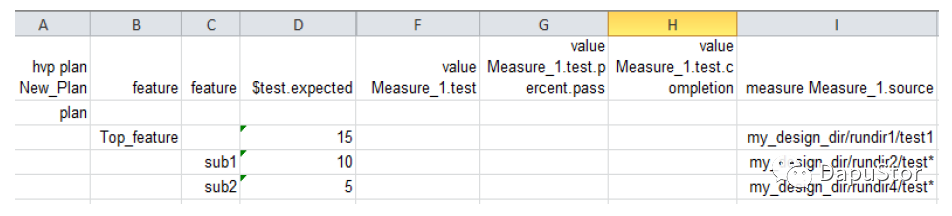

當然,如果你比較鐘愛Excel,那么可以用命令將hvp計劃文件轉(zhuǎn)換成XML格式:

hvpgenxls–planmy_plan.hvp –lca

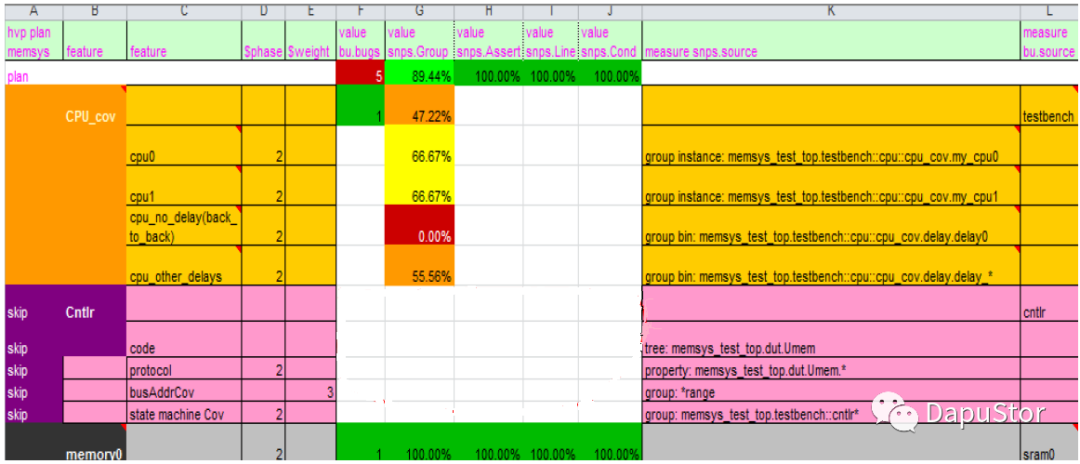

這樣就可以用Excel打開生成的如my_plan.hvp.xml文件了,如圖3所示。

圖3:ExcelXML格式驗證計劃

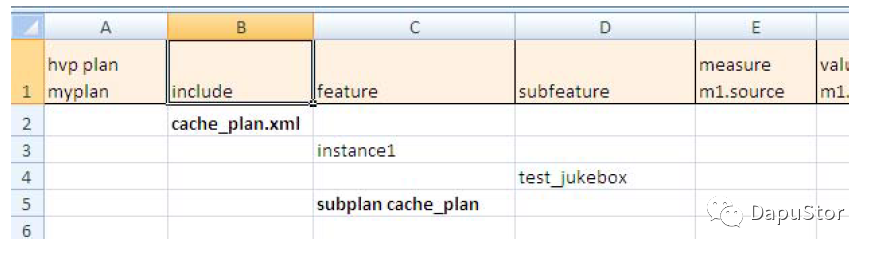

從圖3中可以看出,測試項填在feature列,分層計劃一方面就體現(xiàn)在feature是分級的,C列feature為B列的子feature。另一方面體現(xiàn)在plan可以include子plan,如圖4中include列即為myplan包含了cache_plan。帶有value關(guān)鍵字列表示測試項完成度情況,而帶有measure關(guān)鍵字列則表示對應測試項如何衡量,也即我們所提的如代碼覆蓋率,功能覆蓋率,斷言覆蓋率了。如圖5中“measure snps.source”列中,group關(guān)鍵字表征功能覆蓋率,property關(guān)鍵字表征斷言覆蓋率,tree關(guān)鍵字則表征代碼覆蓋率。

圖4:包含子plan示例

圖5:包含代碼代碼覆蓋率、功能覆蓋率和斷言覆蓋率的plan示例

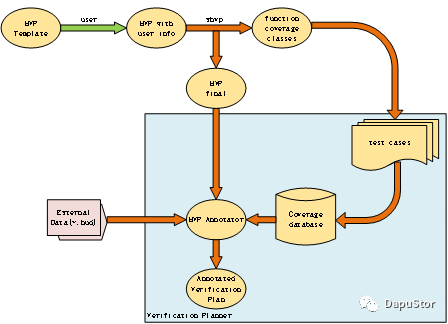

好了,我們的驗證計劃完成了,下一步就要開發(fā)測試用例并作回歸測試。所有測試用例運行完成后,仿真工具VCS會收集這些覆蓋率并輸出數(shù)據(jù)庫。此外,當然我們也希望會收集測試用例是pass還是fail的信息,作為反標信息的用戶自定義輸入信息。有了這些數(shù)據(jù),通過反標工具就可以看到驗證報告了,運行如下命令:

hvpannotate –plan my_plan.hvp.xml –dir *.vdb –userdata *.hud

可以得到my_plan.hvp.ann.xml文件,類似如圖6所有的形式。

圖6:反標后的hvp計劃示例

寫到這里,我們的驗證工程師們確實被這種可視化的、自動化的驗證計劃管理驚艷到了。整個驗證跟蹤過程被自動化,既保證了跟蹤的準確性,也避免了工程繁瑣的管理和手工勞動。重要的一點是,老大再問起驗得咋樣了,我們就可以以數(shù)據(jù)說話:“老大,就一個功能覆蓋點沒覆蓋到了,你看。”領(lǐng)導滿意的點點頭:“嗯,小伙子不錯,年輕有為!”

但是,我們的工程師們也注意到了,填寫功能覆蓋率計劃的時候,要從我們測試平臺中找出covergroup或coverpoint的層次路徑,如圖5中的group instance和group bin。這個可麻煩了,有沒有好的方法不去寫層次路徑,只寫coveragegroup和coverpoint名呢?這個難不倒我們的技術(shù)牛們,他們創(chuàng)造了一個新的HVP流程,如圖7所示。一個新的HVP模板如圖8所示,讓驗證人員只需要填寫class.covergroup[.coverpoint[.bin]]這樣格式的命名來表征當前feature或子feature由哪個covergroup和coverpoint覆蓋測試,然后運行我們開發(fā)的工具xhvp,可以輸出最終的hvp文件和用Systemverilog語言描述的function coverage類聲明文件了。通過上述的步驟,我們的技術(shù)牛把function coverage的代碼都生成好了,對驗證人員真是無比的體貼,大大減輕驗證人員的負擔。當然也大大提高驗證評審的效率,從而加快項目驗證進度。

圖7:新的HVP流程

圖8:HVP模板計劃頁示例

至此,這套大殺器介紹完了,它在我們的DPU600芯片驗證中已經(jīng)被完美地使用。作為DapuStor業(yè)內(nèi)首創(chuàng)的智能存儲SoC芯片,基于最新的12nm FinFET工藝,即有業(yè)內(nèi)領(lǐng)先性能的SSD主控功能,還集成了可計算存儲,機器學習等高大上的特性,同時還擁有強大的功耗管理,晶體管數(shù)接近億級,這么多強大的功能,其驗證復雜度可想而知,得益于我們的HVP流程, DPU600芯片的邏輯驗證順利完成,而且一次流片量產(chǎn)成功,基于DPU600產(chǎn)品也即將面世,敬請期待哦!

原文標題:芯片驗證管理,也能自動跟蹤!

文章出處:【微信公眾號:大普微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435886 -

eda

+關(guān)注

關(guān)注

71文章

2881瀏覽量

176406

原文標題:芯片驗證管理,也能自動跟蹤!

文章出處:【微信號:dputech,微信公眾號:DapuStor】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

西門子利用AI來縮小行業(yè)的IC驗證生產(chǎn)率差距

西門子推出Questa One智能驗證解決方案

概倫電子芯片封裝連接性驗證工具PadInspector介紹

激光焊縫跟蹤器與傳統(tǒng)焊縫檢測方法的對比

soc技術(shù)在智能設(shè)備中的應用

SOC芯片在人工智能中的應用

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗證之路

避免智能手機應用 SOC 跳變的 TI 監(jiān)測計方法應用說明

光學跟蹤器接口連接方法有哪些

機器學習中的交叉驗證方法

Silicon Labs藍牙SoC BG27榮獲2024年資產(chǎn)跟蹤產(chǎn)品獎

大規(guī)模 SoC 原型驗證面臨哪些技術(shù)挑戰(zhàn)?

智能跟蹤SoC驗證進度的方法

智能跟蹤SoC驗證進度的方法

評論