數(shù)據(jù)傳輸是數(shù)字信號(hào)處理過程中的重要一環(huán),其效率影響整個(gè)數(shù)據(jù)處理系統(tǒng)的性能。數(shù)據(jù)傳輸往往采用行業(yè)中標(biāo)準(zhǔn)化的總線技術(shù),使數(shù)字系統(tǒng)的設(shè)計(jì)可靠、方便、易于升級(jí)。PCI作為一種成熟的總線標(biāo)準(zhǔn),應(yīng)用于許多系統(tǒng)的數(shù)據(jù)傳輸過程。針對工業(yè)環(huán)境建立的CompactPCI標(biāo)準(zhǔn)結(jié)合了PCI的電氣特性與優(yōu)良的機(jī)械特性,在工業(yè)領(lǐng)域的應(yīng)用更為廣泛。在設(shè)計(jì)基于PCI或CompactPCI總線的數(shù)字設(shè)備時(shí),采用各公司提供的通用PCI I/O芯片或IP核,可簡化復(fù)雜的PCI接口設(shè)計(jì),加快產(chǎn)品的研發(fā)和升級(jí)。PCI 9656是PLX公司為高速PCI(CompactPCI)總線應(yīng)用而設(shè)計(jì)的通用I/O芯片,適用于66MHz、64bit的PCI(CompactPCI)總線,提供了528MB/s(PCI總線)和264MB/s(局部總線)的突發(fā)傳輸速度,能夠滿足大多高速數(shù)字系統(tǒng)的性能要求。

1 PCI 9656功能簡述

PCI 9656支持66Mhz、64bit的PCI R2.2規(guī)范,提供了兼容PICMG 2.1 R2.0規(guī)范的CompactPCI Hot Swap接口,其局部總線達(dá)到66MHz、32bit(支持0“66MHz、8/16bit),可為PCI(CompactPCI)適配器及嵌入式系統(tǒng)設(shè)計(jì)提供高性能的總線接口。PCI 9656的配置寄存器與PCI 9054、PCI9056兼容,也方便了原有設(shè)計(jì)的移植。

PCI 9656具有6條獨(dú)立的數(shù)據(jù)通道,用于Direct Master、Direct Slave以及DMA功能模式下的數(shù)據(jù)傳輸,其深FIFO設(shè)計(jì)有效提升了總線的突發(fā)傳輸性能。

1 Direct Master模式。用于局部總線到PCI(CompactPCI)的數(shù)據(jù)傳輸,16 QWords(128byte)和32 QWords(256byte)的FIFO各應(yīng)用于數(shù)據(jù)的讀、寫通道。

2 Direct Slave模式。用于PCI(CompactPCI)到局部總線的數(shù)據(jù)傳輸,16 QWords(128byte)和32 QWords(256byte)的FIFO各應(yīng)用于數(shù)據(jù)的讀、寫通道。

3 DMA模式。PCI 9656提供了兩條DMA通道(Channel 0、Channel 1),使用了兩獨(dú)立的32 QWords(256byte)雙向FIFO。兩條DMA通道可同時(shí)傳輸數(shù)據(jù),通過PCI 9656的MARBR寄存器可配置其優(yōu)先級(jí)關(guān)系。PCI 9656的DMA方式有常規(guī)的塊模式(Block mode)和集散模式(Scatter/Gather mode),而且支持以DREQ#、DASK#信號(hào)請求、應(yīng)答的命令模式(Demand mode),可應(yīng)用于通信領(lǐng)域中的實(shí)時(shí)數(shù)據(jù)傳輸。

在局部總線端,PCI 9656簡化了數(shù)據(jù)的傳輸控制邏輯,與ISA總線類似,方便了傳輸控制的設(shè)計(jì)實(shí)現(xiàn)。PCI 9656的局部總線有三種應(yīng)用模式,可以適用不同的嵌入式處理器。

1 M模式。支持Motorola 32bit的處理器,提供了可與MPC850、MPC860 PowerQCICC 直接相連的接口。

2 C模式。適合大多數(shù)處理器的通用模式,在設(shè)計(jì)中多采用此模式。

3 J模式。與C模式類似,但其地址線與數(shù)據(jù)線復(fù)用。

2 數(shù)據(jù)接收卡設(shè)計(jì)

PCI 9656片內(nèi)資源豐富,功能多樣,采用PCI 9656為接口芯片,可方便地進(jìn)行PCI(Compact)適配器的設(shè)計(jì)。而在PCI 9656的局部總線端,往往不需要實(shí)現(xiàn)其全部邏輯功能,可依據(jù)需要選取配置,更進(jìn)一步簡化設(shè)計(jì)。

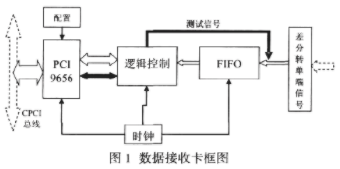

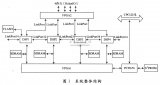

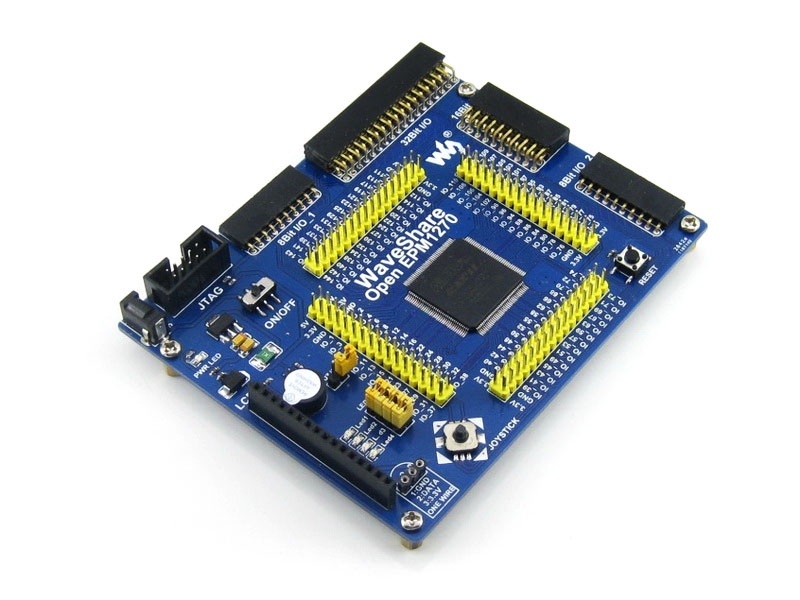

圖1是應(yīng)用PCI 9656的CompactPCI數(shù)據(jù)記錄卡的設(shè)計(jì)框圖,此數(shù)據(jù)接收卡應(yīng)用于一款合成孔徑雷達(dá)的數(shù)據(jù)記錄器中,數(shù)據(jù)源為34bit的差分信號(hào),32bit數(shù)據(jù),1bit采樣時(shí)鐘,1bit數(shù)據(jù)有效標(biāo)志位。圖1中:時(shí)鐘驅(qū)動(dòng)ICS553向PCI 9656、邏輯控制模塊和FIFO提供同步時(shí)鐘信號(hào);初始化配置芯片采用Microchip 93LC56B,PCI 9000系列提供3線的E2PROM串行接口,可在系統(tǒng)上電時(shí)初始化內(nèi)部配置寄存器;差分到單端信號(hào)的轉(zhuǎn)換經(jīng)由Ti公司的LVDT386和390完成;FIFO采用了IDT公司所設(shè)計(jì)的高速、低功耗的72T36135M,數(shù)據(jù)容量為512K×36bit,使用易于級(jí)聯(lián)的First Word Follow Through工作模式;邏輯控制部分采用Altera的MAXII EPM1270,實(shí)現(xiàn)FIFO到PCI 9656局部總線間的數(shù)據(jù)傳輸控制。

2.1 PCI9656的設(shè)計(jì)應(yīng)用

在CompactPCI端,PCI 9656提供了66MHz、64bit總線應(yīng)用所需信號(hào),可依據(jù)CompactPCI規(guī)范連接,通過簡單的外部電路,可實(shí)現(xiàn)Hot Swa p功能。

在局部總線端,采用了PCI 9656的C模式。在C模式下,PCI 9656的局部總線可配置實(shí)現(xiàn)三種數(shù)據(jù)傳輸邏輯。(1)Single cycle mode。每次傳輸1個(gè)數(shù)據(jù)(8/16/32bit),默認(rèn)的傳輸模式。(2)Burst-4 mode。每次4個(gè)數(shù)據(jù),應(yīng)用Intel i960與IBM PPC401處理器時(shí)的推薦模式。(3)Continuous burst mode。多數(shù)據(jù)的連續(xù)突發(fā)傳輸模式,提供了最大的數(shù)據(jù)吞吐量。在傳輸過程中,從設(shè)備(Slave)可通過Bterm#信號(hào)停止傳輸過程。模式2與模式3只選其一,模式1始終可用。在數(shù)據(jù)接收卡中,采用了連續(xù)突發(fā)(Continuous burst)模式,可以有效的利用局部總線帶寬。

分析接收卡的設(shè)計(jì):局部總線端無處理器,PCI 9656在此端為主設(shè)備(Master),始終占用總線,負(fù)責(zé)邏輯控制的CPLD為從設(shè)備(Slave),始終響應(yīng)PCI 9656。數(shù)據(jù)傳輸過程只利用了PCI 9656的Direct Slave和DMA模式,,而且不需DMA的命令模式,運(yùn)行過程中數(shù)據(jù)通過FIFO單向傳輸,不需解碼地址信號(hào),對CPLD的控制可通過向其寫命令碼完成。因此,可以對PCI 9656的許多信號(hào)簡化處理,只需實(shí)現(xiàn)如下信號(hào)的時(shí)序要求:

LD[31:0],32bits數(shù)據(jù)信號(hào)。

ADS#,總線操作的開始標(biāo)志。

Blast#,突發(fā)傳輸?shù)慕Y(jié)束標(biāo)志。

LW/R#,寫/讀信號(hào)。

Wait#,主設(shè)備暫停傳輸信號(hào),信號(hào)無效標(biāo)志主設(shè)備正常。

Ready#,從設(shè)備操作完成信號(hào),信號(hào)有效標(biāo)志從設(shè)備正常。

EOT#,數(shù)據(jù)傳輸異常中止信號(hào),用于FIFO溢出或空時(shí)中斷數(shù)據(jù)傳輸。

Lint#,中斷信號(hào)輸入,用于引起CompactPCI總線端的中斷。

LRST#,局部總線端重置。

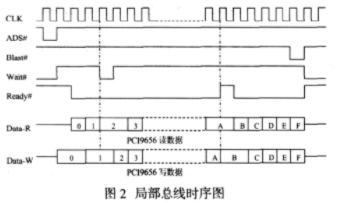

信號(hào)經(jīng)簡化后,在正常的讀寫操作中,只需要處理ADS#、Blast#、LW/R#、Wait#、Ready#與數(shù)據(jù)的邏輯關(guān)系,Single cycle可認(rèn)為是Continuous burst的特例,從而將兩種模式下的邏輯時(shí)序統(tǒng)一處理。正常操作中,ADS#、Blast#、Wait#、Ready#需滿足的邏輯關(guān)系如圖2所示:

圖2中,ADS#、Blast#、Wait#信號(hào)由PCI 9656驅(qū)動(dòng),LW/R#(圖2中未標(biāo)出)也由PCI 9656驅(qū)動(dòng),在整個(gè)過程中處于低或高,標(biāo)志PCI 9656對總線的讀或?qū)懖僮鳌eady#由CPLD驅(qū)動(dòng),Data為雙向信號(hào)。CPLD空閑狀態(tài)時(shí)監(jiān)測ADS#信號(hào),一旦ADS#有效,則根據(jù)LW/R#轉(zhuǎn)入讀或?qū)懖僮鳌Wx操作中,CPLD將FIFO數(shù)據(jù)讀出,同時(shí)將Ready#置為有效狀態(tài),需監(jiān)測Wait#,Wait#無效時(shí),才可繼續(xù)讀取下一數(shù)據(jù);寫操作中,CPLD需將Ready#置為有效狀態(tài),監(jiān)測Wait#,Wait#無效時(shí),CPLD才可完成總線上數(shù)據(jù)的寫入;當(dāng)CPLD檢測到Blast#、Wait# 、Ready#均為有效狀態(tài)時(shí),便完成最后一個(gè)數(shù)據(jù)的傳輸操作,轉(zhuǎn)至空閑狀態(tài)。

實(shí)現(xiàn)上述的數(shù)據(jù)傳輸邏輯,再加上適當(dāng)?shù)漠惓G闆r和測試轉(zhuǎn)換控制,便可設(shè)計(jì)CPLD的邏輯控制模塊。

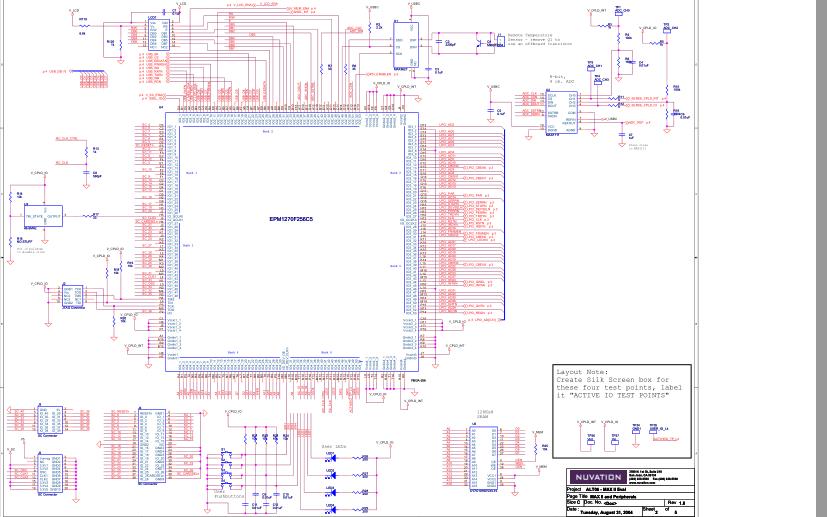

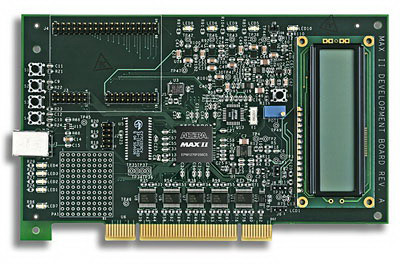

2.2 MAXII EPM1270應(yīng)用

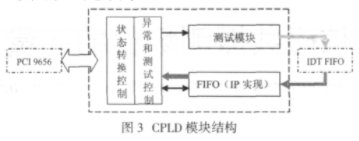

MAXII系列是Altera公司的新型架構(gòu)CPLD,與傳統(tǒng)架構(gòu)的CPLD相比,MAXII的功耗和成本大幅降低,資源密度和性能卻顯著提升,非常適用于接口間的控制協(xié)議轉(zhuǎn)換。設(shè)計(jì)中采用了MAXII的EPM1270型號(hào)CPLD,其設(shè)計(jì)結(jié)構(gòu)如圖3所示。MAXII EPM1270內(nèi)部主要分為邏輯控制、測試、FIFO三個(gè)模塊:

1 FIFO采用Altera提供的IP核實(shí)現(xiàn),容量可根據(jù)資源利用情況調(diào)節(jié),使用FWFT(First Word Follow Through)模式,為CPLD提供與外部FIFO簡便的接口。

2 測試模塊產(chǎn)生測試數(shù)據(jù),控制數(shù)據(jù)通道在真實(shí)數(shù)據(jù)源與測試數(shù)據(jù)源間切換,在測試接收卡時(shí)使用。

3 邏輯控制模塊內(nèi)有異常和測試控制、狀態(tài)轉(zhuǎn)換控制兩部分,通過一個(gè)8bit寄存器進(jìn)行通信。(1)寄存器控制CPLD的測試模塊、狀態(tài)選擇,同時(shí)記錄FIFO的狀態(tài)變化。(2)異常和測試控制部分依據(jù)狀態(tài)寄存器內(nèi)容控制測試模塊,監(jiān)測FIFO的溢出、半滿、空等狀態(tài),產(chǎn)生Lint#信號(hào)或通過控制寄存器傳遞到狀態(tài)轉(zhuǎn)換控制部分,使之有效EOT#,中斷數(shù)據(jù)傳輸。(3)狀態(tài)轉(zhuǎn)換控制部分執(zhí)行局部總線的數(shù)據(jù)讀寫邏輯,建立了四個(gè)狀態(tài):S0,空閑狀態(tài);S1,數(shù)據(jù)讀狀態(tài);S2,寄存器讀狀態(tài);S3,命令寫狀態(tài)。S0狀態(tài)下根據(jù)LW/R#信號(hào)和寄存器內(nèi)容確定向S1、S2、S3狀態(tài)的轉(zhuǎn)換。S1狀態(tài)下讀取FIFO數(shù)據(jù),根據(jù)FIFO狀態(tài)產(chǎn)生異常中止信號(hào)EOT#。S2狀態(tài)下 讀取8bit寄存器內(nèi)容。S3狀態(tài)下向8bit寄存器寫入命令碼來改寫和重置其相關(guān)比特位,從而控制CPLD的測試模塊,切換S1、S2狀態(tài),清空FIFO。

通過上述設(shè)計(jì)模塊,MAXII CPLD便可在PCI 9656與IDT 72T36135M之間建立一個(gè)簡捷的數(shù)據(jù)傳輸通道。

3 結(jié)束語

PCI 9656采用了PLX公司業(yè)界領(lǐng)先的數(shù)據(jù)通道架構(gòu)技術(shù),其豐富的功能為高速的PCI(CompactPCI)總線應(yīng)用提供了簡捷的I/O設(shè)計(jì)途徑。文章介紹了采用PCI 9656作為PCI I/O設(shè)計(jì)的一款應(yīng)用于66Mhz、64bit CompactPCI總線系統(tǒng)的數(shù)據(jù)接收卡。本文作者創(chuàng)新點(diǎn): 1 將PCI 9656應(yīng)用于66Mhz、64bit CompactPCI總線系統(tǒng),滿足高速數(shù)據(jù)傳輸?shù)囊蟆? 采用CPLD內(nèi)建FIFO的IP核實(shí)現(xiàn)FIFO與PCI 9656的接口連接,優(yōu)化了CPLD的轉(zhuǎn)換邏輯。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19804瀏覽量

233527 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

170996 -

適配器

+關(guān)注

關(guān)注

9文章

2025瀏覽量

69299

發(fā)布評(píng)論請先 登錄

PCI9656介紹及其應(yīng)用實(shí)例

USB -CPLD開發(fā)板使用攻略

MPC8260和PLX9656組成的嵌入式系統(tǒng)的PCI接口設(shè)計(jì)方案

PCI9656 pdf datasheet

應(yīng)用PCI 9656的數(shù)據(jù)接收卡設(shè)計(jì)

基于PCI IP核的碼流接收卡的設(shè)計(jì)

PCI9656實(shí)現(xiàn)與CPCI總線通信的雷達(dá)信號(hào)處理板

EDA-E-EPM1270產(chǎn)品說明書

EPM1270 CPLD開發(fā)板的電路原理圖合集免費(fèi)下載

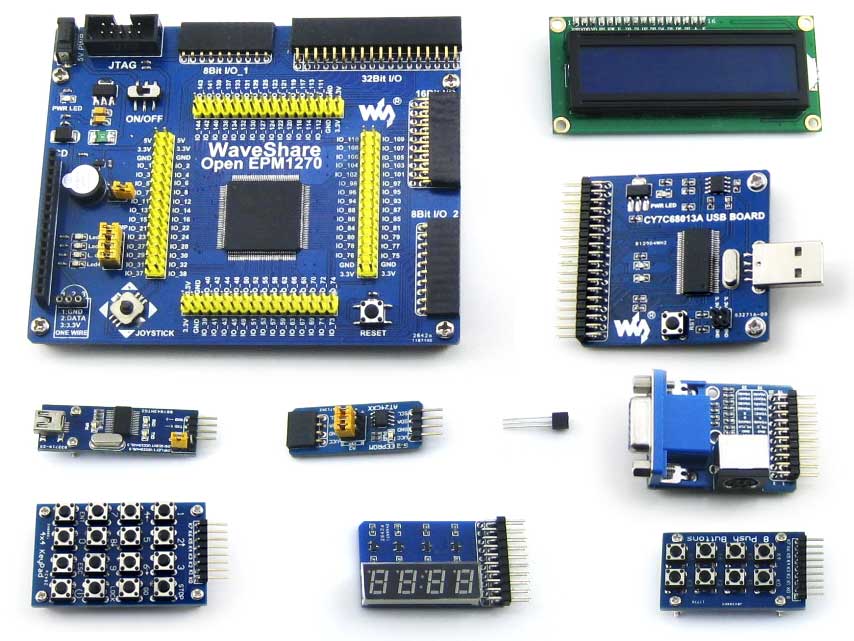

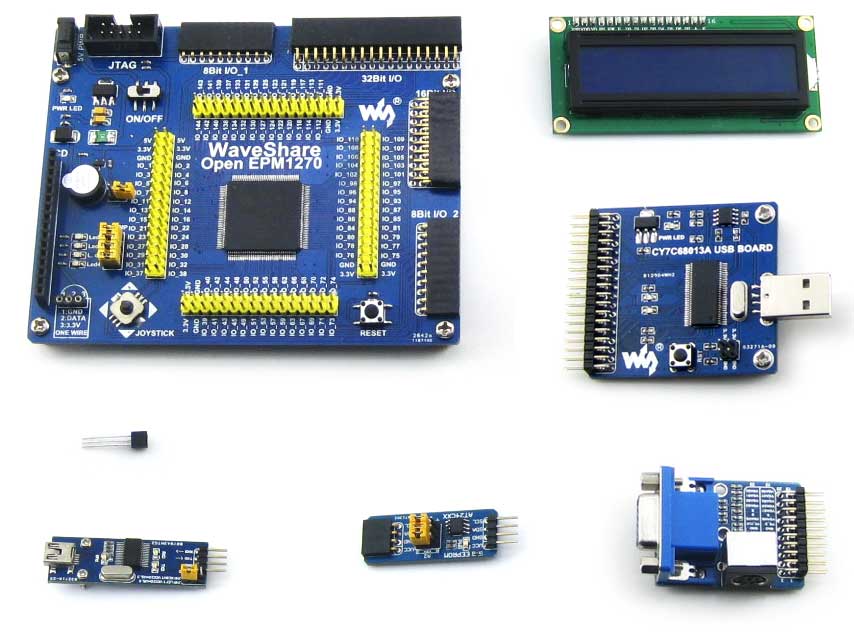

微雪電子OpenEPM1270 CPLD開發(fā)板簡介

微雪電子OpenEPM1270 CPLD 開發(fā)板簡介

微雪電子OpenEPM1270 CPLD開發(fā)板簡介

基于DK-MAXII-1270NESField-Programmable Gate Array的參考設(shè)計(jì)

基于PCI9656和MAXII EPM1270實(shí)現(xiàn)數(shù)據(jù)接收卡的應(yīng)用方案

基于PCI9656和MAXII EPM1270實(shí)現(xiàn)數(shù)據(jù)接收卡的應(yīng)用方案

評(píng)論