作者:焦敬恩,爾桂花,戴瓊海

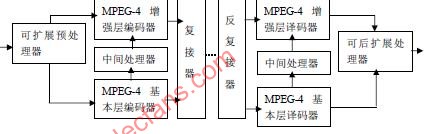

MPEG-4是一種開放性標準,其中許多部分都沒有規(guī)定,可以加入一些新的算法,因此采用通用DSP能夠隨時更新算法、優(yōu)化算法、使得編碼效率更高。由于MPEG-4編碼算法復(fù)雜,需要存儲的數(shù)據(jù)量大,無論是存儲空間分配、數(shù)據(jù)傳輸還是運算速度對DSP來說都是挑戰(zhàn)。本文介紹了基于C6000系列DSP的MPEG-4視頻編碼卡的軟硬件實現(xiàn)。利用DSP的VLIW和流水線結(jié)構(gòu)設(shè)計程序可以使MPEG-4編碼效率大大提高。

1 DSP特性介紹

由于算法的復(fù)雜性及數(shù)據(jù)量的日益增大,單靠串行結(jié)構(gòu)的處理器完成數(shù)據(jù)處理工作已經(jīng)越來越不可行,因此出現(xiàn)了并行結(jié)構(gòu)的CPU以完成這一新的任務(wù)。現(xiàn)今最著名的兩種并行體系結(jié)構(gòu)是超長指令字VLIW(Very Long Instruction Word)結(jié)構(gòu)和超標量體系結(jié)構(gòu)。由于超標量體系結(jié)構(gòu)CPU硬件極其復(fù)雜,指令動態(tài)調(diào)度將導(dǎo)致時間的不確定性,所以DSP很少使用這種結(jié)構(gòu)。而一般使用超長指令字(VLIW)結(jié)構(gòu),這種長指令通常包括多個彼此獨立的同步操作。

C6000系列DSP是TI公司生產(chǎn)的高檔DSP。這一系列DSP都是基于VelociTITM構(gòu)架的VLIW DSP,它在每個周期可以執(zhí)行八條32bit的指令,具有高達200MHz的CPU,從而使得其運算能力達到1600MIPS(200MHz×8條指令=1600MIPS)。這些性能都確立了它在高端多媒體應(yīng)用中的地位。

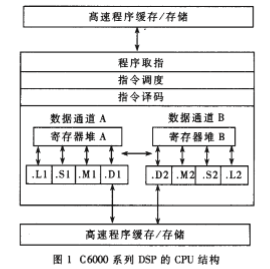

DSP的CPU結(jié)構(gòu)如圖1所示,它具有兩個通道,每個通道具有4個功能單元(1個乘法器和3個算術(shù)邏輯單元),16個32位通用寄存器,每個通道的功能單元可以隨意訪問本通道的寄存器。CPU還有兩個交叉單元,通過它們,一個通道的功能單元可以訪問另一個通道的寄存器。另外CPU還具有256bit寬的數(shù)據(jù)和程序通道,可以使程序存儲器在每個時鐘周期提供8條并行執(zhí)行指令。這種CPU結(jié)構(gòu)是DSP具有VLIW結(jié)構(gòu)的最基本條件。此系列DSP的存儲空間映射為內(nèi)部存儲器、內(nèi)部外設(shè)及擴展存儲器。其中內(nèi)部存儲器由64KB內(nèi)部程序存儲器和數(shù)據(jù)存儲器構(gòu)成,內(nèi)部程序存儲器可以映射到CPU地址空間或者作為Cache操作。內(nèi)部和外部數(shù)據(jù)存儲器均可通過CPU、DMA或HPI(HostPort Interface)方式訪問,HPI接口使上位機可以訪問DSP的存儲空間。

2 MPEG-4編碼卡的硬件設(shè)計

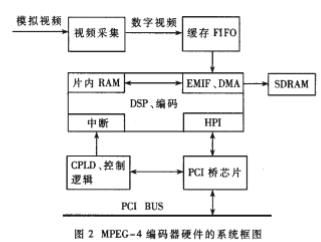

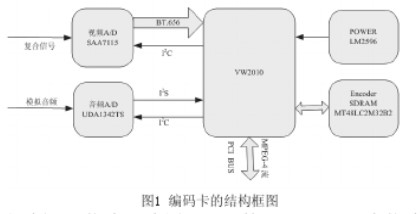

MPEG-4編碼卡包括幾部分:視頻采集、視頻的MPEG-4編碼、整個系統(tǒng)的CPLD控制、PC機與DSP的通信等模塊,其結(jié)構(gòu)框圖如圖2所示。

2.1 視頻采集

視頻采集部分主要完成模擬視頻到數(shù)字視頻的轉(zhuǎn)換,包括一片視頻采集芯片和一片小的CPLD。CPLD的作用是控制視頻采集芯片,將采得的數(shù)據(jù)從8位或16位轉(zhuǎn)化為32位,并且使數(shù)據(jù)按照Y、U、V分開的方式排列。這樣相當于對采集到的數(shù)據(jù)進行了一次預(yù)處理,以便于視頻編碼使用。另外,CPLD將32位寬的數(shù)據(jù)輸出給32位的FIFO。用32位的FIFO以及將視頻數(shù)據(jù)轉(zhuǎn)換為32位,可以使DSP讀取視頻數(shù)據(jù)時32位的數(shù)據(jù)總線沒有空閑,從而提高DSP讀取視頻數(shù)據(jù)的效率;這里使用FIFO是為了減少DSP讀取數(shù)據(jù)的時間、降低高速設(shè)備和低速設(shè)備的不匹配。每次FIFO半滿時,CPLD會給DSP發(fā)送中斷信號,并且在中斷處理程序中使用DMA方式讀取視頻數(shù)據(jù);如果不使用FIFO,DSP會頻繁中斷,從而花費大量時間在入棧、出棧以及寄存器的設(shè)置上。

2.2 視頻編碼

DSP讀入視頻數(shù)據(jù)后進行先期處理,如將YUV格式轉(zhuǎn)為RGB格式等;然后進行MPEG-4視頻編碼。在這一過程中,數(shù)據(jù)訪問通常要占用50%的時間,算術(shù)運算要占用30%的時間,控制要占用20%的時間。因為需要進行運動估計和運動補償,在數(shù)據(jù)存儲器中通常保存一幀I(原始幀)幀圖像和至少一幀P(預(yù)測幀)幀圖像,這些圖像占用的空間都比較大,因此一般都放在外部存儲器SDRAM里。在編碼過程中還要存儲DCT系數(shù)、運動向量、量化矩陣、可變長編碼表、Z形編碼表等,由于占用較小的存儲空間而且會反復(fù)用到,因此把它們放在片內(nèi)存儲器中。

2.3 PC與編碼卡通信

PC與編碼卡通信可以通過并口、串口、USB口、PCI接口等方式實現(xiàn)。其中PCI接口方式易于PC與編碼器高速傳輸數(shù)據(jù),因此本文采用PCI接口。編碼后的數(shù)據(jù)通過DSP的HPI、PCI橋芯片、PCI總線到達PC。PC通過DSP的HPI直接對DSP的存儲空間進行訪問。HPI有兩種工作方式:一種是單數(shù)據(jù)讀寫,這種方式每次只能讀寫一個數(shù)據(jù),一般主機對編碼參數(shù)進行設(shè)置,例如設(shè)置圖像大小、幀率等;另一種是burst方式的數(shù)據(jù)讀寫,在這種方式下只需要指定初始訪問地址,然后以地址自加的方式訪問DSP的存儲空間,這種訪問方式不需要DSP的CPU參與。圖2中CPLD完成PCI橋芯片與DSP之間的訪問控制,DSP、PCI的中斷控制等功能。

3 MPEG-4編碼卡的軟件設(shè)計

C6000系列DSP提供的編譯環(huán)境支持C++、C以及匯編語言,用C++設(shè)計的程序執(zhí)行效率較低,一般不用;大多數(shù)都采用C語言和匯編語言相結(jié)合的方式來完成DSP程序設(shè)計。DSP程序設(shè)計流程如下:先寫出C代碼并對其優(yōu)化,如果不能達到預(yù)期的運行效率,則編寫匯編代碼來提高效率。對于MPEG-4這樣復(fù)雜的算法,只運用C語言是遠遠不夠的,在本設(shè)計里大部分代碼都由匯編語言完成。

設(shè)計高效的代碼,必須充分利用該DSP的VLIW和流水線結(jié)構(gòu)。利用VLIW結(jié)構(gòu)可以在一個時鐘周期并行執(zhí)行八條32位指令;在流水線結(jié)構(gòu)下,一條指令的執(zhí)行不用等待上一條指令執(zhí)行結(jié)束,例如DSP從內(nèi)存中讀取一個數(shù)據(jù)需要5個時鐘周期,在讀取這個數(shù)據(jù)的同時,DSP可以去執(zhí)行別的指令,不必等待這條指令執(zhí)行結(jié)束。具有這兩種結(jié)構(gòu)的DSP在性能提高的同時,程序設(shè)計也變得比較復(fù)雜。對于具有VLIW和流水線結(jié)構(gòu)的DSP在設(shè)計程序時必須注意以下幾個問題:

·每一個指令包可以包括多條操作指令,在C6000系列DSP中每一條指令包括八條32位操作指令;

·可以將兩個16位數(shù)據(jù)或者四個8位數(shù)據(jù)合并成一個32位數(shù)據(jù),以提高存取效率;

·必須靜態(tài)地知道每條操作指令執(zhí)行需要的時鐘周期,這樣才能取得該操作的正確結(jié)果;

·這種結(jié)構(gòu)的處理器不能處理動態(tài)事件,例如Cache突然消失;

·對于多周期才能完成的指令,在正確計算的基礎(chǔ)上,一定要提前執(zhí)行,以免出現(xiàn)一條指令必須等上一條指令執(zhí)行結(jié)束才能執(zhí)行的情況。

下面結(jié)合C6000系列DSP的指令及其具體資源情況,以MPEG-4中的算法為例說明如何利用這兩種結(jié)構(gòu)設(shè)計出高效的代碼。

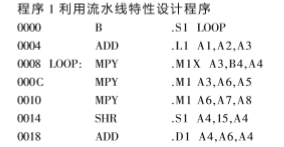

3.1 利用流水線結(jié)構(gòu)設(shè)計程序

流水線是指指令的處理可分為幾個子操作,每個子操作由不同的單元完成。對每個單元來說,每隔一個時鐘周期可進入一條新指令,在同一時間內(nèi)不同單元可以同時處理多條指令。在C6000中B(.unit)lable是一條跳轉(zhuǎn)指令,它的執(zhí)行周期為7個時鐘周期,也就是說,在安排這條指令之后6個時鐘周期才能使程序轉(zhuǎn)移到lable處執(zhí)行,以程序1為例說明如何利用流水線結(jié)構(gòu)設(shè)計程序。該程序的執(zhí)行順序如下:0000→0004→0008→000C-0010→0014→0008→000C.。.從程序執(zhí)行順序知道,要想在執(zhí)行完0014處的指令后跳轉(zhuǎn)到LOOP處,就應(yīng)該在0014的前6個時鐘周期處安排這條指令;如果不提前安排好這條指令,而是在0014后放置這條指令,就需要使CPU等待6個時鐘周期才能跳到LOOP處,從而使程序運行效率降低。從這個程序的執(zhí)行順序可以看出,必須提前知道每一條指令的運行周期數(shù),并提前安排該指令,才能達到減少等待周期、提高程序效率的效果。C6000系列DSP指令集包括許多多時鐘周期的指令,如跳轉(zhuǎn)指令、數(shù)據(jù)訪問指令等。MPEG-4編碼算法需要頻繁地訪問大量數(shù)據(jù),并且有很多循環(huán),無論是數(shù)據(jù)訪問還是循環(huán)都要用到多時鐘周期指令。以MEPG-4的DCT算法為例,每一個8×8的塊變換需要用16次的跳轉(zhuǎn)指令和256次數(shù)據(jù)訪問指令,由此可見流水線在MPEG-4程序優(yōu)化中所起的作用。

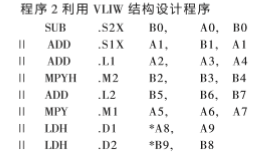

3.2 利用VLIW結(jié)構(gòu)設(shè)計程序

利用VLIW結(jié)構(gòu)設(shè)計程序可以充分利用DSP多個功能單元并行工作的特性。DSP的每一個通道都有四個功能單元(L、S、M、D),每個功能單元負責完成一定的邏輯或者算術(shù)運算,另外A、B兩個通道的互訪可以通過交叉單元1x、2x完成。程序2中,在一個時鐘周期內(nèi)并行執(zhí)行八條指令,使用了所有的功能單元S2、S1、L1、M2、L2、M1、D1、D2,同時使用了所有的交叉單元1x、2x,已經(jīng)達到極限。但是這種并行指令的使用也有一定的限制,其最根本的要求就是不能引起資源沖突,例如:

·不能用同一個功能單元;

·不能對同一通道的寄存器進行兩次long型寫操作;

·不能對同一通道的寄存器同時進行l(wèi)ong型讀操作和存儲操作;

·讀同一寄存器不能超過4次;

·在同一個時鐘周期不能有兩個指令寫入同一寄存器,這不是說向同一寄存器寫的兩條指令不能放在同一個并行指令包內(nèi),而是說兩個指令不能在寫寄存器的那個時鐘周期并存。

仍然以MPEG-4中的DCT算法為例說明VLIW結(jié)構(gòu)在程序優(yōu)化中的作用。進行DCT變換的原始數(shù)據(jù)是short型的,因此可以將兩個數(shù)據(jù)合成一個32位的數(shù)據(jù)來訪問;為了使兩個通道并行訪問數(shù)據(jù)和運算,應(yīng)盡量把要訪問的數(shù)據(jù)平均地分配給不同的通道寄存器;并且通過交叉單元使兩個通道相互訪問,從而達到很高的并行性,大大提高了編碼效率。

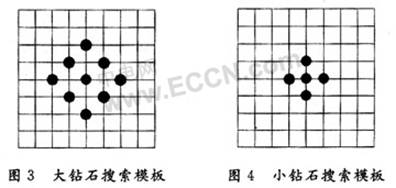

MPEG-4編碼的其它算法,例如逆DCT、運動估計、運動補償?shù)人惴ǘ及罅康难h(huán)運算和數(shù)據(jù)訪問。因此利用DSP的VLIW結(jié)構(gòu)和流水線結(jié)構(gòu)優(yōu)化MPEG-4編碼算法就成為一種非常合適的方法。

當然,編寫程序時不是將DSP的VLIW結(jié)構(gòu)和流水線結(jié)構(gòu)分開考慮,而是將兩者結(jié)合起來,在編寫每一條指令時都要清楚這條指令的執(zhí)行周期以及使用的功能單元,這樣才能編寫出高效的程序。

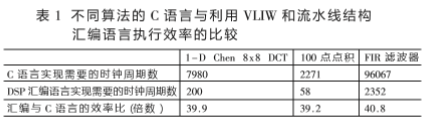

表1對1-D Chen 8×8 DCT、100點點積和FIR濾波器算法的C語言實現(xiàn)與利用VLIW及流水線結(jié)構(gòu)的匯編代碼實現(xiàn)進行比較。從統(tǒng)計數(shù)據(jù)可以看出,利用DSP結(jié)構(gòu)編寫的匯編代碼執(zhí)行效率要比C語言編寫的代碼執(zhí)行效率高40倍左右。因此充分利用DSP的VLIW結(jié)構(gòu)和流水線結(jié)構(gòu)設(shè)計匯編程序能夠使效率大幅度提高。

本文對MPEG-4編碼卡進行了設(shè)計,主要難點是MPEG-4編碼算法的優(yōu)化,MPEG-4的編碼復(fù)雜、代碼量大。利用C6000系列DSP的VLIW結(jié)構(gòu)和流水線結(jié)構(gòu)設(shè)計出了MPEG-4編碼算法。實驗證明,算法效率得到了大幅度提高。

責任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19804瀏覽量

233529 -

dsp

+關(guān)注

關(guān)注

555文章

8142瀏覽量

355211 -

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123322

發(fā)布評論請先 登錄

基于MPEG-4技術(shù)的醫(yī)療系統(tǒng)

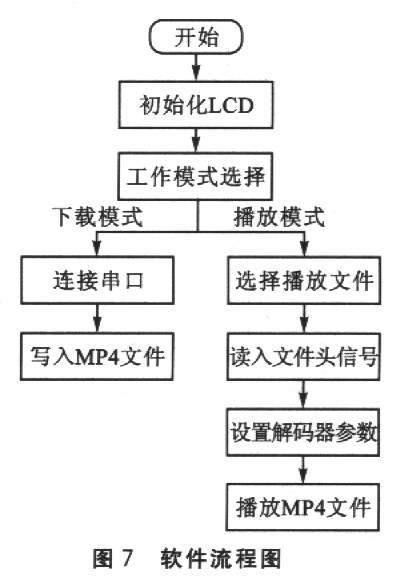

基于FPGA NiosII的MPEG-4視頻播放器該怎么設(shè)計?

基于FPGA NiosII的MPEG-4視頻播放器該怎么設(shè)計?

怎么實現(xiàn)基于C6000系列DSP的MPEG-4視頻編碼卡的軟硬件設(shè)計?

怎么實現(xiàn)MPEG-4 ASP視頻編碼器的軟件優(yōu)化設(shè)計?

TMS320C6201 在MPEG-4 視頻解碼器中的應(yīng)用

基于FPGA NiosII的MPEG-4視頻播放器

MPEG-4在視頻監(jiān)控應(yīng)用中的軟件實現(xiàn)

PC機的MPEG-4編碼原理及實現(xiàn)

基于MPEG-4的視頻DCT編碼器的實現(xiàn)

定制DSP設(shè)計MPEG-4無線視頻產(chǎn)品

MPEG-4視頻編解碼實現(xiàn)方案解析

基于DSP設(shè)計MPEG-4無線視頻產(chǎn)品的案例分析

基于DSP設(shè)計的MPEG-4無線視頻產(chǎn)品解析

應(yīng)用于廣播視頻監(jiān)控系統(tǒng)中MPEG-4解碼卡的設(shè)計

采用數(shù)字信號處理器實現(xiàn)MPEG-4視頻編碼卡的設(shè)計

采用數(shù)字信號處理器實現(xiàn)MPEG-4視頻編碼卡的設(shè)計

評論