日本關西學院大學和豐田通商于3月1日宣布,他們已開發出“動態AGE-ing”技術,這是一種表面納米控制工藝技術,可以消除使SiC襯底上的半導體性能變差的缺陷。

盡管期望將SiC用作下一代功率半導體,但是已知在晶圓的加工階段和晶體生長階段會發生晶體畸變。其中,已知基底平面錯位(Basal Plane Dislocation,BPD)會降低器件的性能,并且制造抑制這種現象發生的高質量晶圓的成本高昂,難以降低器件的價格。

動態AGE-ing是一種通過結合熱退火,晶體生長和熱蝕刻技術將BPD缺陷轉換為不影響器件性能的其他缺陷的技術。同一大學的科學與工程學院的Tadaaki Kaneko教授說:“盡管還有其他技術可以對高質量SiC晶圓中的缺陷進行“解毒”,但是Dynamic AGE-ing可以應用于具有許多缺陷和質量較差的晶圓。”,說明了該技術的優勢。

具體而言,通過使用一個唯一的裝置適當地選擇并執行三個加工過程,可以自動布置晶圓表面上的原子排列,去除加工應變層,并通過刀片(TED)傳送BPD。可以消除對設備的影響。

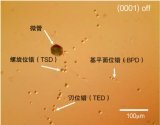

圖:使用動態AGE-ing進行BPD排毒的驗證示例。通過將該技術應用于市售的SiC晶圓,可以確認基板上的BPD數量為1個或更少(來源:關西學院大學的介紹材料)

在這項聯合研究中,從單個零件的尺寸到150毫米(6英寸)晶圓,這是兩年研究與開發中SiC的主流,無論基板的尺寸如何,在某些情況下,晶圓制造商無論,據說BPD可以免費使用。

豐田通商計劃將其商業化,但目前正處于廣泛招募對這項技術感興趣的公司作為業務合作伙伴的階段。另外,作為研究,預計在未來幾年中將實際使用200 mm SiC晶圓,因此我們計劃繼續進行開發以將其應用于該技術。

責任編輯:YYX

-

晶圓

+關注

關注

53文章

5161瀏覽量

129773 -

SiC

+關注

關注

31文章

3223瀏覽量

65219

發布評論請先 登錄

一文搞懂波峰焊工藝及缺陷預防

有效抑制SiC外延片掉落物缺陷生成的方法

碳化硅襯底的生產過程

室溫下制造半導體材料的新工藝問世

不同的碳化硅襯底的吸附方案,對測量碳化硅襯底 BOW/WARP 的影響

碳化硅襯底的環吸方案相比其他吸附方案,對于測量碳化硅襯底 BOW/WARP 的影響

碳化硅SiC制造工藝詳解 碳化硅SiC與傳統半導體對比

SiC單晶襯底加工技術的工藝流程

中國臺灣與遼寧新增SiC襯底工廠,年產能合計達7.2萬片

8英寸襯底+全SiC模塊,羅姆助力SiC普及浪潮

創新工藝可以消除SiC襯底中的缺陷

創新工藝可以消除SiC襯底中的缺陷

評論