作者:falwat

版權聲明:本文為博主原創文章,遵循 CC 4.0 BY-SA 版權協議,轉載請附上原文出處鏈接和本聲明。

本文鏈接:https://blog.csdn.net/falwat/article/details/85918300

本文介紹如何在 vivado 開發教程(一) 創建新工程 的基礎上, 使用IP集成器, 創建塊設計。

創建基本的MicroBlaze系統

點擊Vivado 左側流程導航器中的"IP INTERGRATOR" 下的 "Create Block Design".

點擊"Diagram"中心的"+", 或者使用快捷鍵"Ctrl+I", 或者右鍵選擇菜單"Add IP", 選擇"MicroBlaze" ,雙擊加入到塊設計中.

點擊"Diagram"窗口中的"Run Block Automation", 運行塊自動化. 在彈出的對話框中,根據需要修改選項, 這里先不做任何修改, 點擊"OK"完成.

繼續點擊"Diagram"窗口中的"Run Block Automation", 運行塊自動化, 設置時鐘和復位信號.

在"Diagram"窗口中,右鍵選擇菜單"Regenerate Laout", 重新生成布局, 如下圖所示:

添加外設

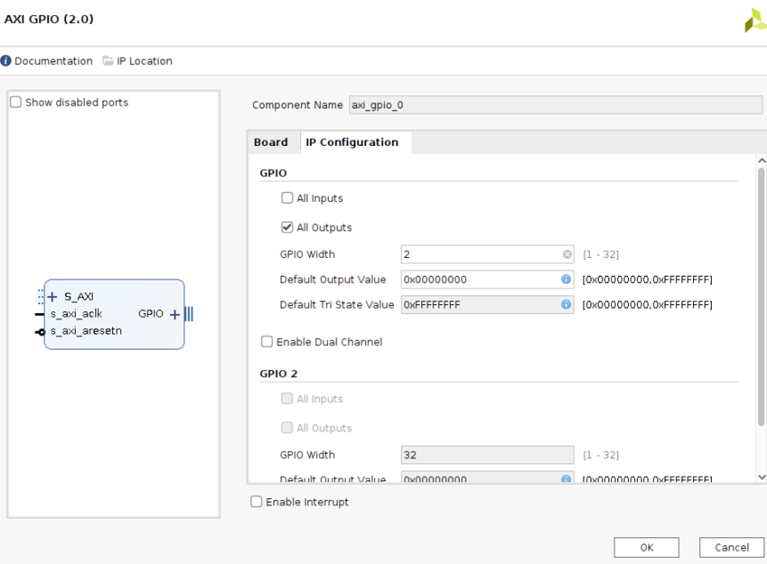

在"Diagram" 窗口中添加"AXI GPIO" IP核, 點擊"Diagram"窗口頂部的"Run Connection Automation", 運行連接自動化. 按下圖進行配置, 配置完成后, 點擊"OK".

在"Diagram"窗口中,右鍵選擇菜單"Regenerate Laout", 重新生成布局, 如下圖所示:

按照上面的步驟,繼續添加串口IP("AXI Uartlite").

在"Diagram"窗口中,右鍵選擇菜單"Validate Design" 或使用快捷鍵"F6", 驗證設計. 驗證通過后, 關閉"Block Design" 窗口.

生成輸出產品(Generate Output Products)

切回工程管理("PROJECT MANAGER" )視圖, 在 "system(system.bd)"上右鍵選擇菜單"Generate Output Products", 生成輸出產品.

在彈出的對話框中,設置并行運行數量(Number of jobs), 點擊"Generate" 按鈕, 等待生成完成.生成過程中, 內存占用和CPU占用會急劇飆升.

創建HDL包裝(HDL Wrapper)

在 "system(system.bd)"上右鍵選擇菜單"Create HDL Wrapper". 在彈出的對話框中,點擊"OK"即可, 生成的"system_wrapper"會自動被設置為頂層.

審核編輯:何安

-

Vivado

+關注

關注

19文章

828瀏覽量

68186 -

IP集成器

+關注

關注

0文章

4瀏覽量

5846

發布評論請先 登錄

Vivado FIR IP核實現

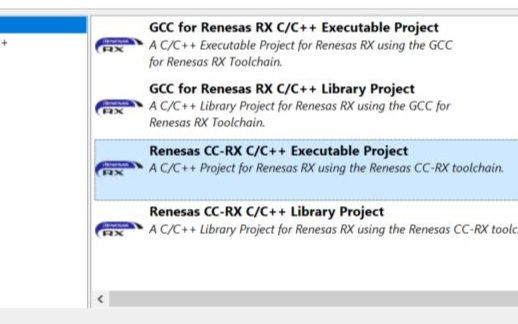

eIQ Time Series Studio工具使用攻略(三)-工程創建

EE-192:使用C語言在Blackfin處理器上創建中斷驅動系統

如何在Linux系統上設置站群服務器IP地址

Altium Designer 18~24創建、打開工程閃退

如何在TMS320C6727 DSP上創建基于延遲的音頻效果

Multi-Scaler IP的Linux示例以及Debug(上)

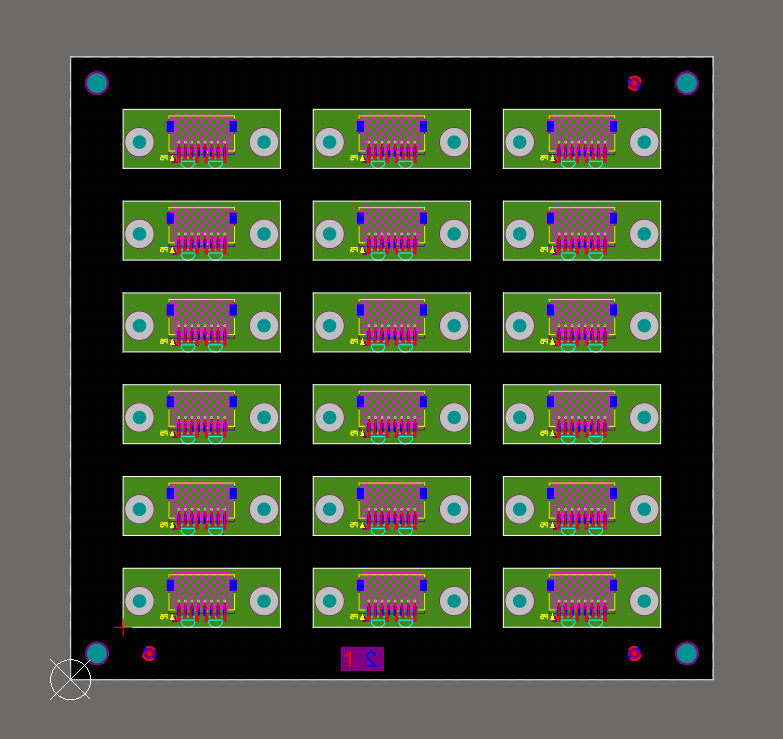

如何在Draftsman中創建PCB制造圖紙

如何在vivado創建新工程上使用IP集成器創建塊設計

如何在vivado創建新工程上使用IP集成器創建塊設計

評論