作者: ALINX

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

對于ZYNQ來說PL(FPGA)開發(fā)是至關重要的,這也是ZYNQ比其他ARM的有優(yōu)勢的地方,可以定制化很多ARM端的外設,在定制ARM端的外設之前先讓我們通過一個LED例程來熟悉PL(FPGA)的開發(fā)流程,熟悉Vivado軟件的基本操作,這個開發(fā)流程和不帶ARM的FPGA芯片完全一致。

在本例程中,我們要做的是LED燈控制實驗,每秒鐘控制開發(fā)板上的LED燈翻轉一次,實現(xiàn)亮、滅、亮、滅的控制。會控制LED燈,其它外設也慢慢就會了。

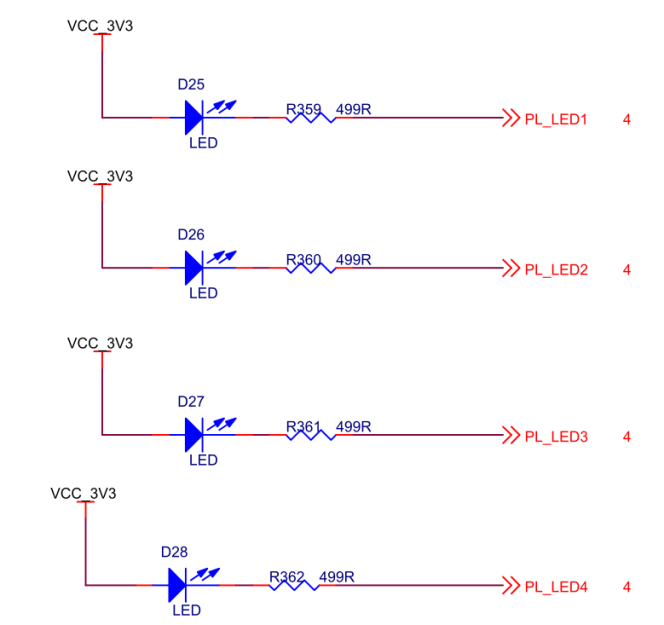

1. LED硬件介紹

1.1 開發(fā)板的PL部分連接了4個紅色的用戶LED燈。這1個燈完全由PL控制。如果PL_LED1為高電平,燈則會滅,否則會亮。

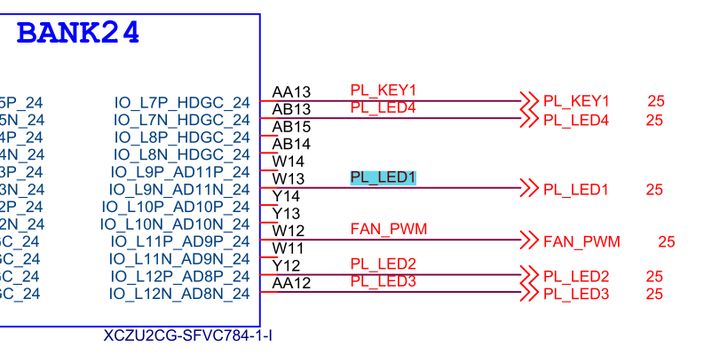

1.2 我們可以根據(jù)原理圖的連線關系確定LED和PL管腳的綁定關系。

1.3 原理圖中以PS_MIO開頭的IO都是PS端IO,不需要綁定,也不能用于PL端的引腳綁定

2. 創(chuàng)建Vivado工程

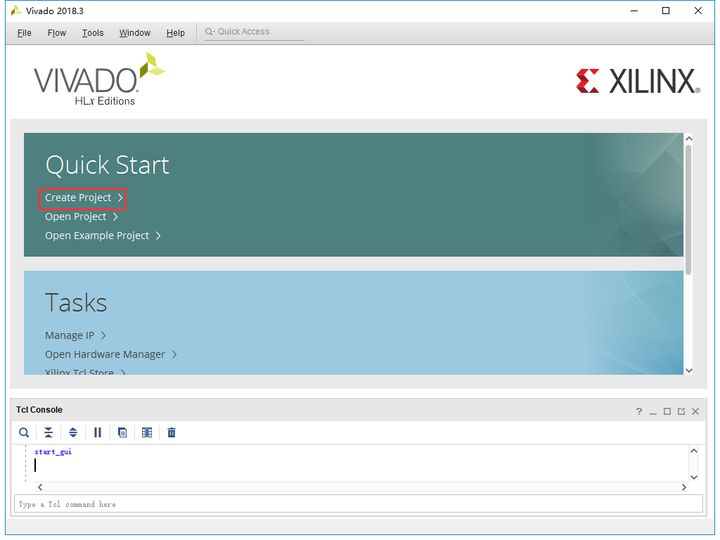

2.1 啟動Vivado,在Windows中可以通過雙擊Vivado快捷方式啟動

2.2 在Vivado開發(fā)環(huán)境里點擊“Create New Project”,創(chuàng)建一個新的工程。

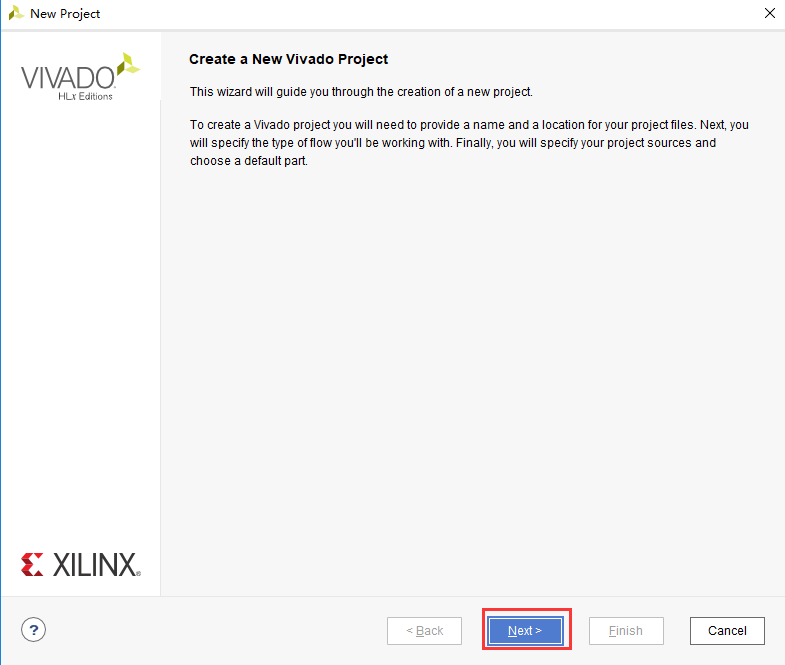

2.3 彈出一個建立新工程的向導,點擊“Next”

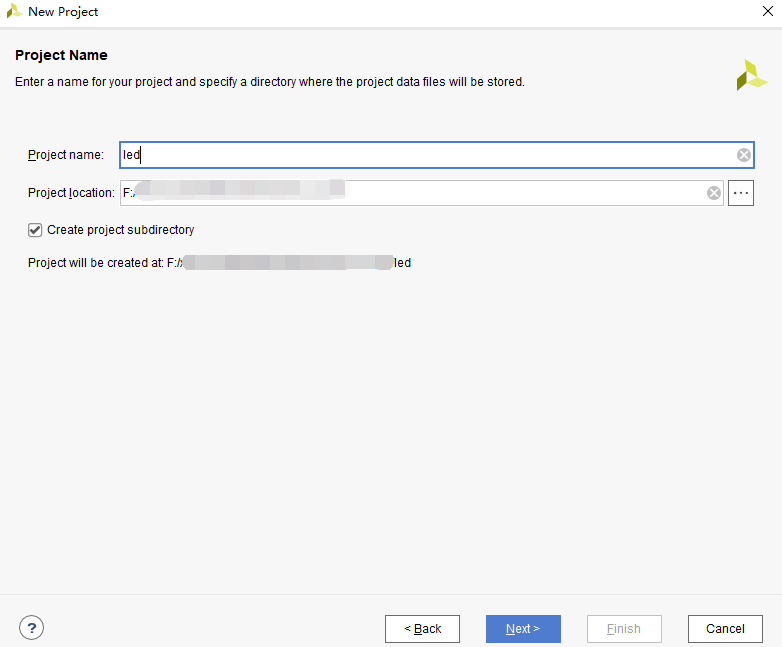

2.4 在彈出的對話框中輸入工程名和工程存放的目錄,我們這里取一個led的工程名。需要注意工程路徑“Project location”不能有中文空格,路徑名稱也不能太長。

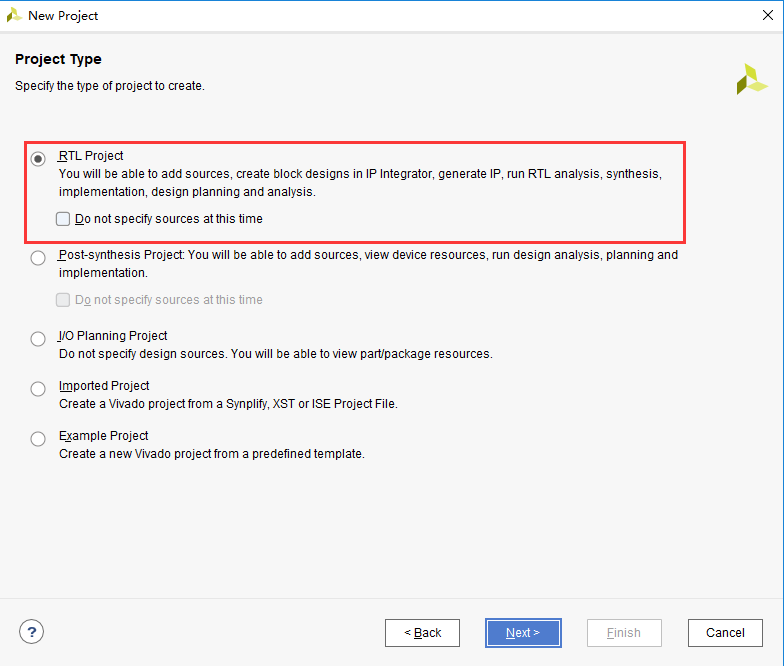

2.5 在工程類型中選擇“RTL Project”

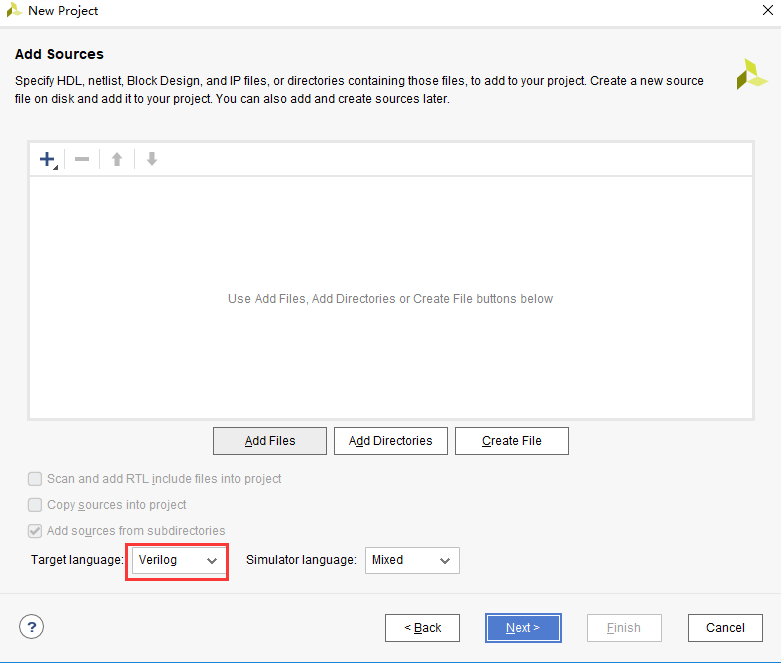

2.6 目標語言“Target language”選擇“Verilog”,雖然選擇Verilog,但VHDL也可以使用,支持多語言混合編程。

2.7 點擊“Next”,不添加任何文件

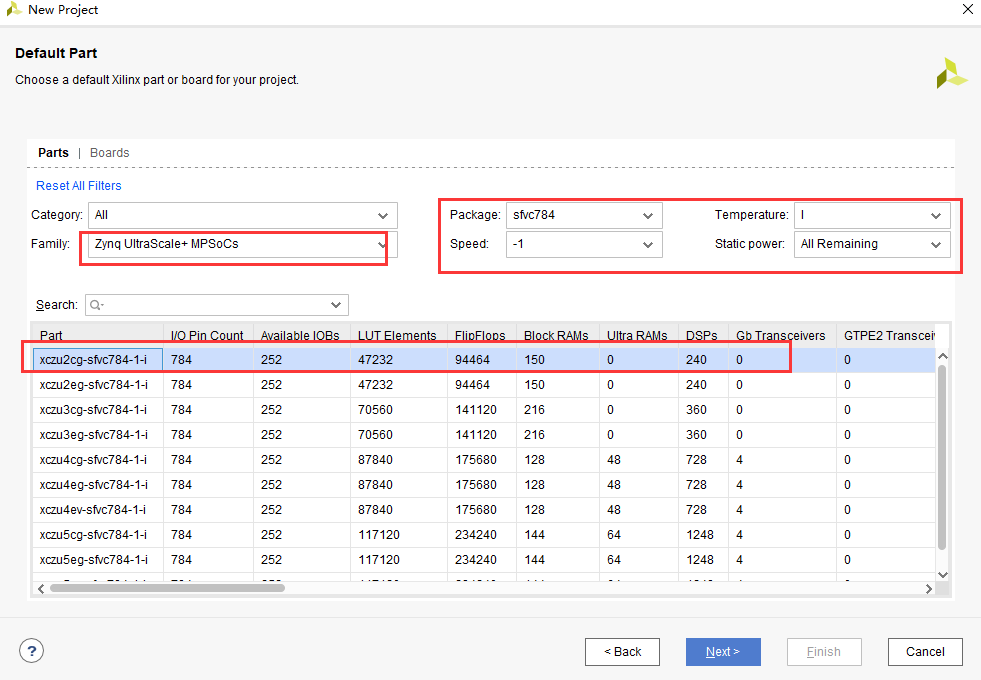

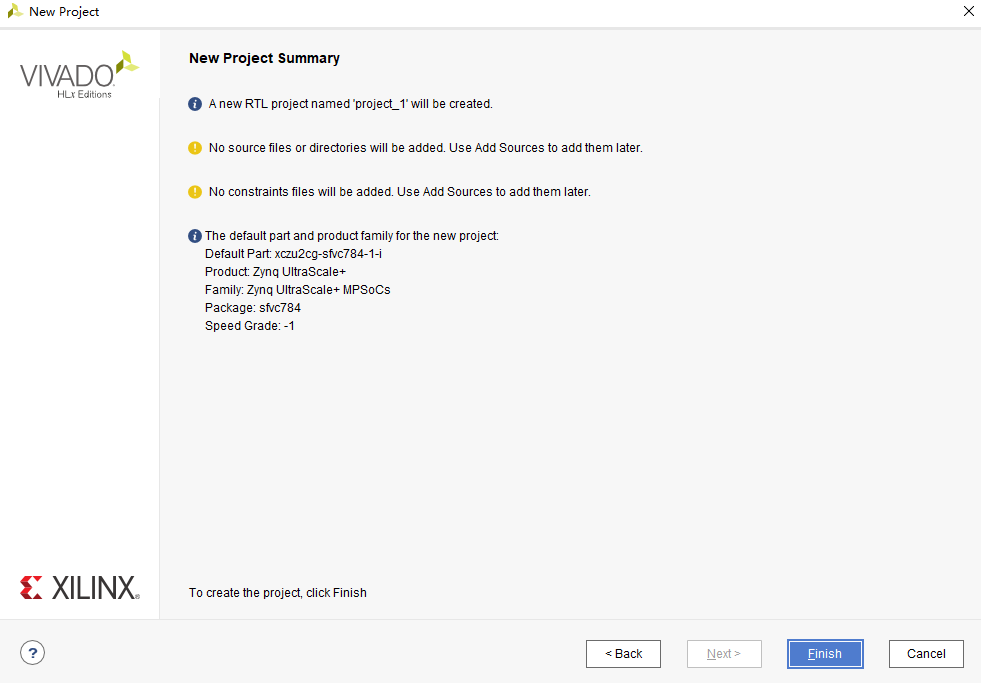

2.8 在“Part”選項中,器件家族“Family”選擇“Zynq UltraScale+ MPSoCs”,封裝類型“Package”選擇“sfvc784”,Speed選擇”-1”,Temperature選擇“I”減少選擇范圍。在下拉列表中選擇“xczu2cg-sfvc784-1-i”,“-1”表示速率等級,數(shù)字越大,性能越好,速率高的芯片向下兼容速率低的芯片。

2.9 點擊“Finish”就可以完成以后名為“l(fā)ed”工程的創(chuàng)建。

2.10 Vivado軟件界面

3. 創(chuàng)建Verilog HDL文件點亮LED

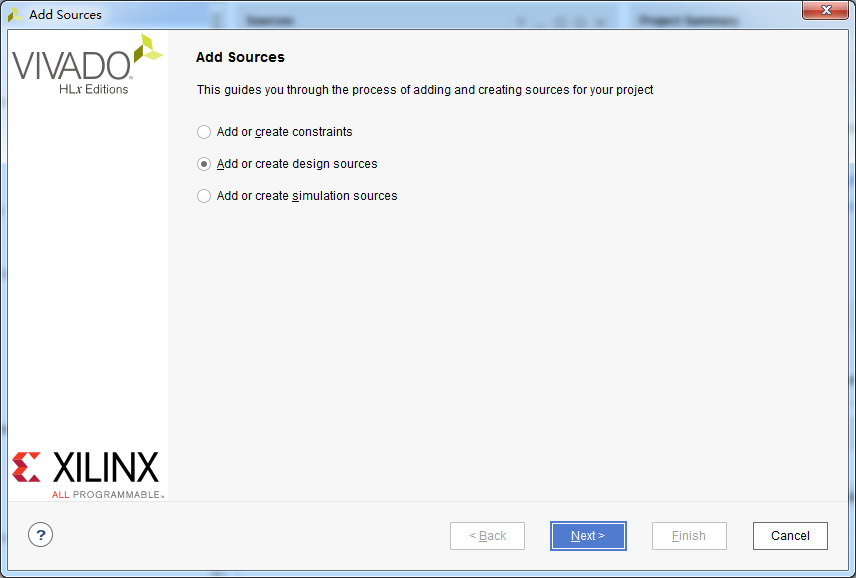

3.1 點擊Project Manager下的Add Sources圖標(或者使用快捷鍵Alt+A)

3.2 選擇添加或創(chuàng)建設計源文件“Add or create design sources”,點擊“Next”

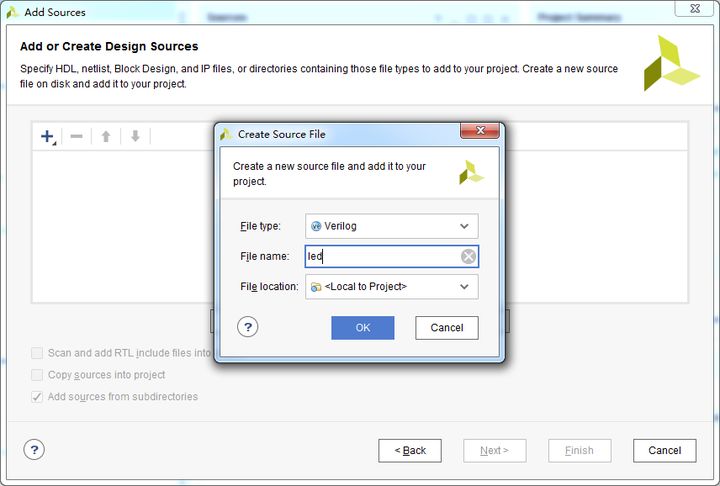

3.3 選擇創(chuàng)建文件“Create File”

3.4 文件名“File name”設置為“l(fā)ed”,點擊“OK”

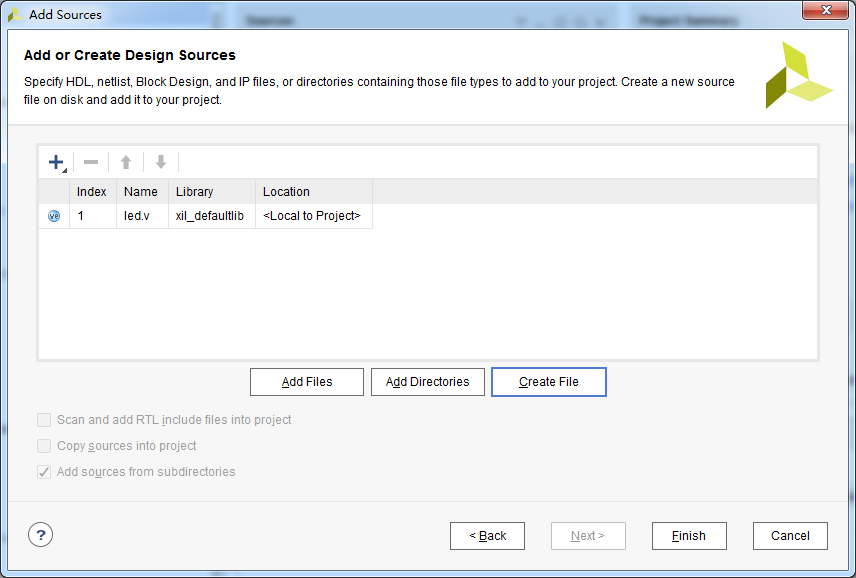

3.5 點擊“Finish”,完成“l(fā)ed.v”文件添加

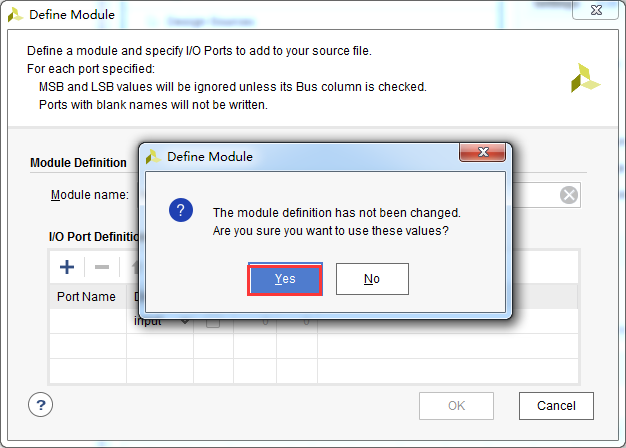

3.6 在彈出的模塊定義“Define Module”,中可以指定“l(fā)ed.v”文件的模塊名稱“Module name”,這里默認不變?yōu)椤發(fā)ed”,還可以指定一些端口,這里暫時不指定,點擊“OK”。

3.7 在彈出的對話框中選擇“Yes”

3.8 雙擊“l(fā)ed.v”可以打開文件,然后編輯

3.9 編寫“l(fā)ed.v”,這里定義了一個32位的寄存器timer, 用于循環(huán)計數(shù)0~24999999(1秒鐘), 計數(shù)到24999999(1秒)的時候, 寄存器timer變?yōu)?,并翻轉四個LED。這樣原來LED是滅的話,就會點亮,如果原來LED為亮的話,就會熄滅。編寫好后的代碼如下:

module led( input sys_clk, input rst_n, outputreg[3:0] led ); reg[31:0] timer_cnt; always@(posedge sys_clk ornegedge rst_n) begin if(!rst_n) begin led <=4'd0; timer_cnt <=32'd0; end elseif(timer_cnt >=32'd24_999_999) begin led <=~led; timer_cnt <=32'd0; end else begin led <= led; timer_cnt <= timer_cnt +32'd1; end end endmodule

3.10 編寫好代碼后保存

4. 添加管腳約束

Vivado使用的約束文件格式為xdc文件。xdc文件里主要是完成管腳的約束,時鐘的約束, 以及組的約束。這里我們需要對led.v程序中的輸入輸出端口分配到FPGA的真實管腳上。

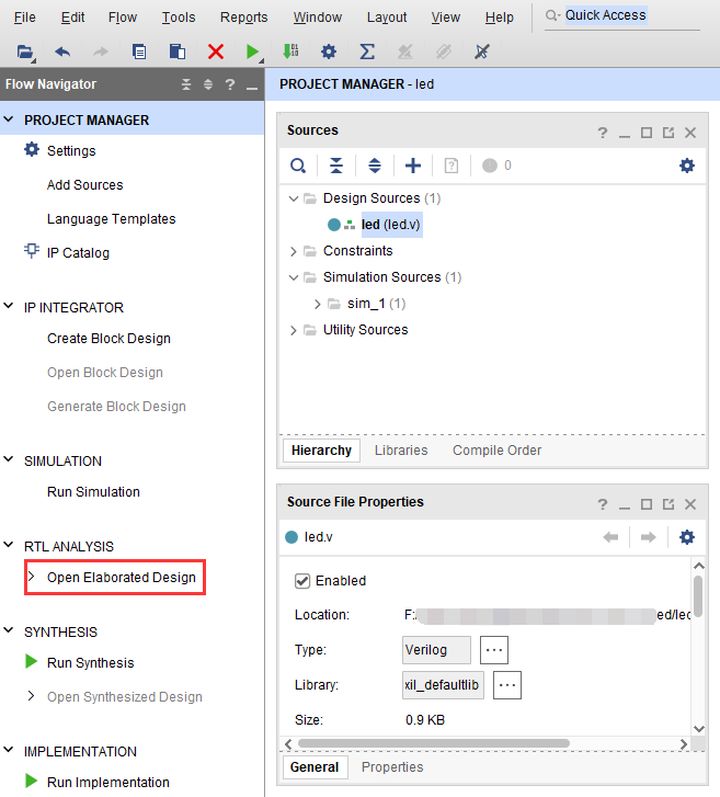

4.1 點擊“Open Elaborated Design”

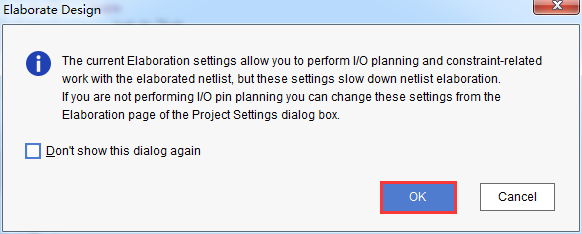

4.2 在彈出的窗口中點擊“OK”按鈕

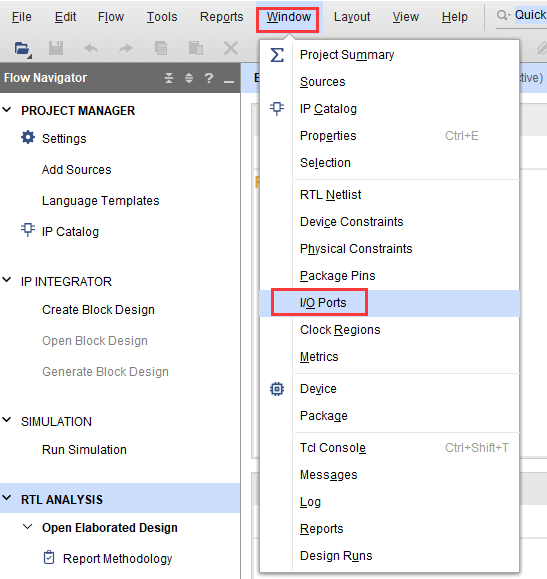

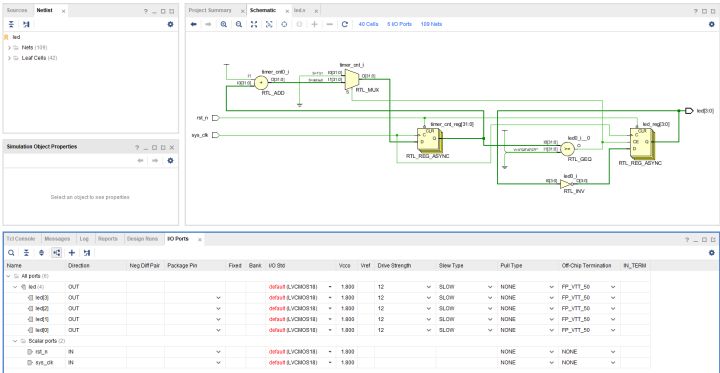

4.3 在菜單中選擇“Window -> I/O Ports”

4.4 在彈出的I/O Ports中可以看到管腳分配情況

4.5 將復位信號rst_n綁定到PL端的按鍵,給LED和時鐘分配管腳、電平標準,完成后點擊保存圖標

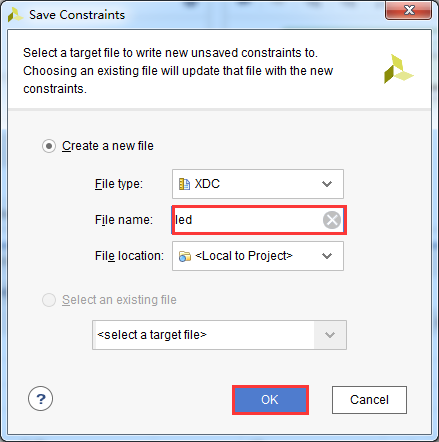

4.6 彈出窗口,要求保存約束文件,文件名我們填寫“l(fā)ed”,文件類型默認“XDC”,點擊“OK”

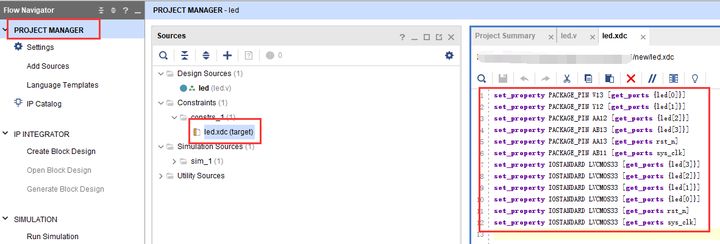

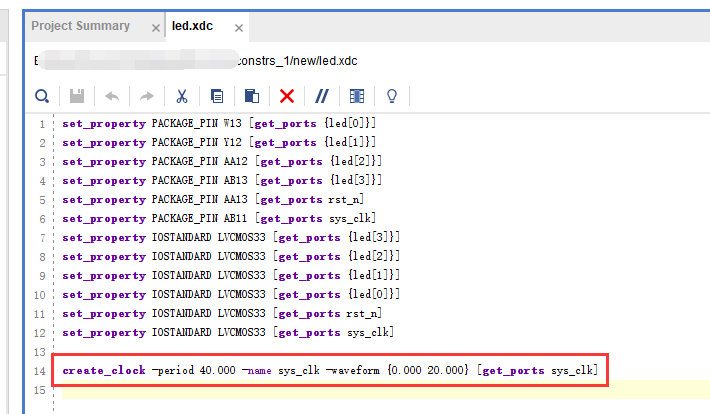

4.7 打開剛才生成的“l(fā)ed.xdc”文件,我們可以看到是一個TCL腳本,如果我們了解這些語法,完全可以通過自己編寫led.xdc文件的方式來約束管腳

下面來介紹一下最基本的XDC編寫的語法,普通IO口只需約束引腳號和電壓,管腳約束如下:

set_property PACKAGE_PIN "引腳編號" [get_ports “端口名稱”]

電平信號的約束如下:

set_property IOSTANDARD "電平標準" [get_ports “端口名稱”]

這里需要注意文字的大小寫,端口名稱是數(shù)組的話用{ }刮起來,端口名稱必須和源代碼中的名字一致,且端口名字不能和關鍵字一樣。

電平標準中“LVCMOS33”后面的數(shù)字指FPGA的BANK電壓,LED所在BANK電壓為3.3伏,所以電平標準為“LVCMOS33”。Vivado默認要求為所有IO分配正確的電平標準和管腳編號。

5. 添加時序約束

一個FPGA設計除了管腳分配以外,還有一個重要的約束,那就是時序約束,這里通過向導方式演示如果進行一個時序約束。

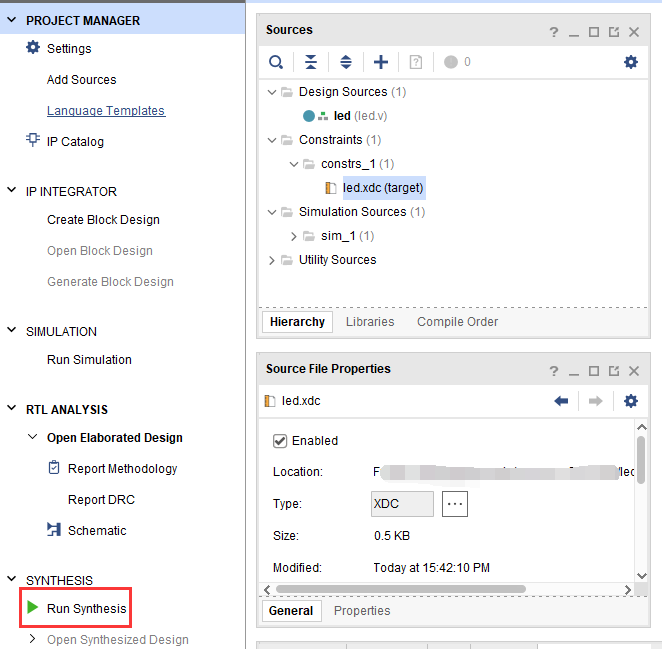

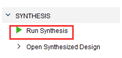

5.1 點擊“Run Synthesis”開始綜合

5.2 彈出對話框點擊“OK”

5.3 綜合完成以后點擊“Cancel”

5.4 點擊“Constraints Wizard”

5.5 在彈出的窗口中點擊“Next”

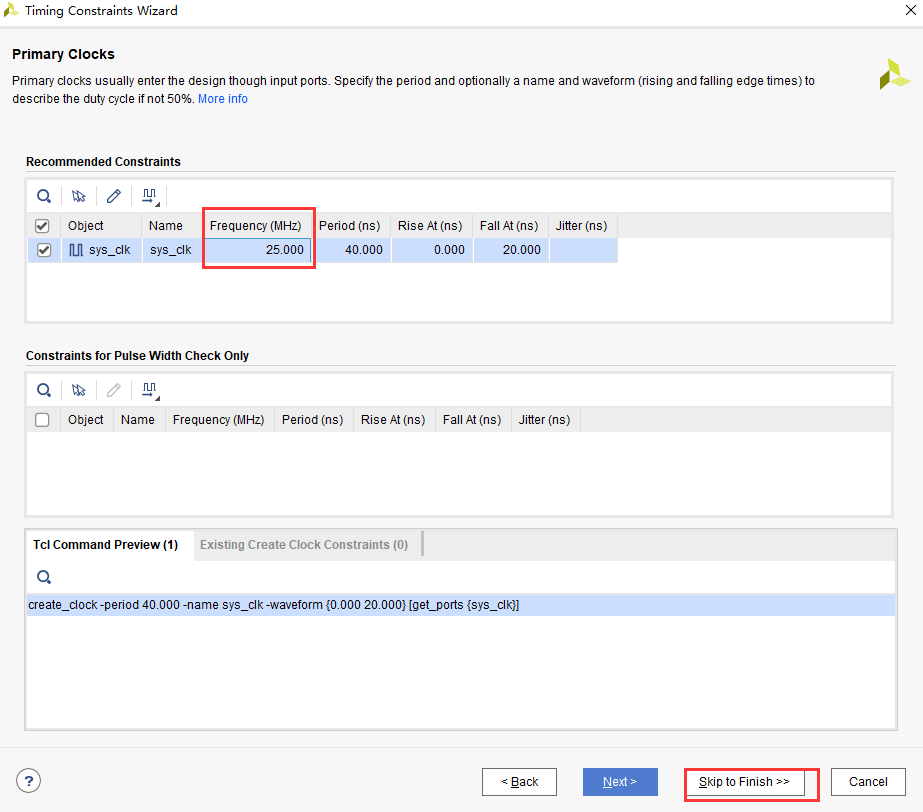

5.6 時序約束向導分析出設計中的時鐘,這里把“sys_clk_p”頻率設置為200Mhz,然后點擊“Skip to Finish”結束時序約束向導。

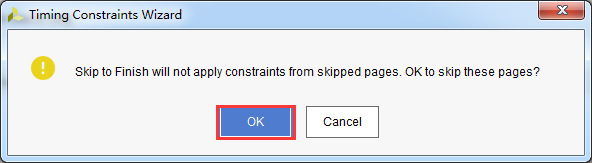

5.7 彈出的窗口中點擊“OK”

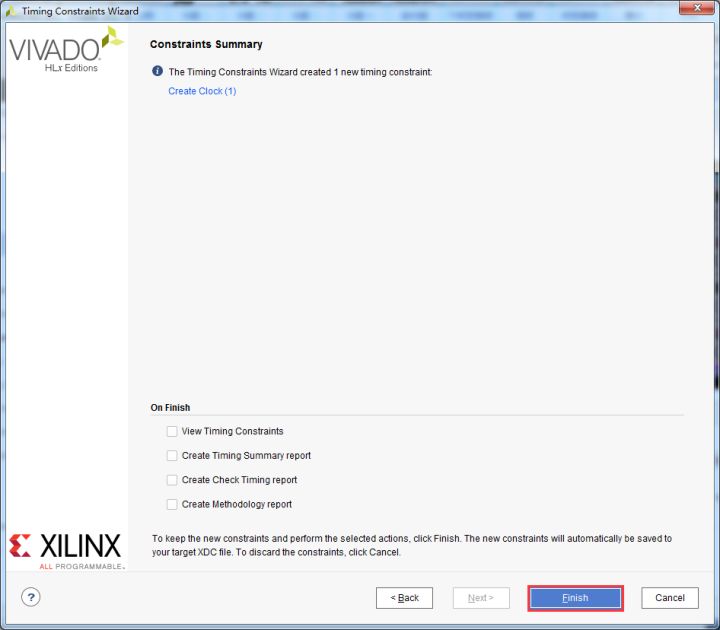

5.8 點擊“Finish”

5.9 這個時候led.xdc文件已經(jīng)更新,如果xdc文件已經(jīng)打開,會提示“Reload”重新加載文件,并保存文件

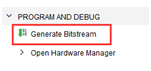

6. 生成BIT文件

6.1 編譯的過程可以細分為綜合、布局布線、生成bit文件等,這里我們直接點擊“Generate Bitstream”,直接生成bit文件。

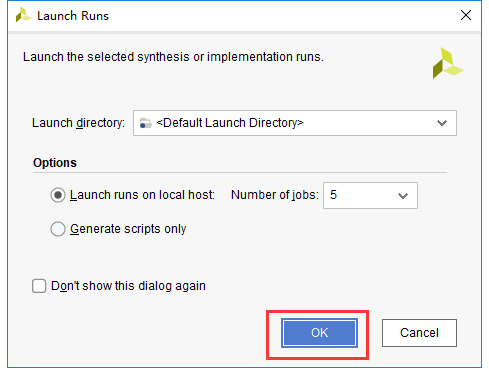

6.2 在彈出的對話框中可以選擇任務數(shù)量,這里和CPU核心數(shù)有關,一般數(shù)字越大,編譯越快,點擊“OK”

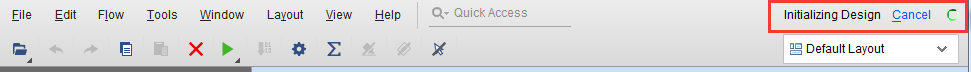

6.3 這個時候開始編譯,可以看到右上角有個狀態(tài)信息,在編譯過程中可能會被殺毒軟件、電腦管家攔截運行,導致無法編譯或很長時間沒有編譯成功。

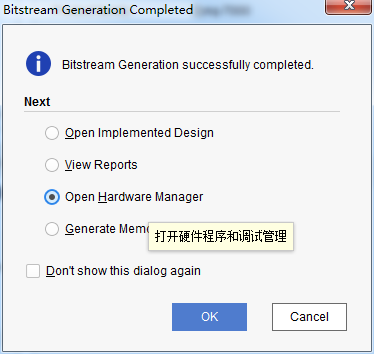

6.4 編譯中沒有任何錯誤,編譯完成,彈出一個對話框讓我們選擇后續(xù)操作,可以選擇“Open Hardware Manger”,當然,也可以選擇“Cancel”,我們這里選擇 “Cancel”,先不下載。

7. Vivado仿真

接下來我們不妨小試牛刀,利用Vivado自帶的仿真工具來輸出波形驗證流水燈程序設計結果和我們的預想是否一致(注意:在生成bit文件之前也可以仿真)。具體步驟如下:

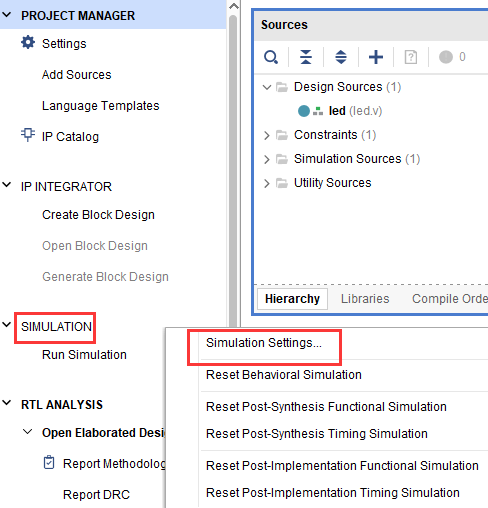

7.1 設置Vivado的仿真配置,右擊SIMULATION中Simulation Settings。

7.2 在Simulation Settings窗口中進行如下圖來配置,這里設置成50ms(根據(jù)需要自行設定),其它按默認設置,單擊OK完成。

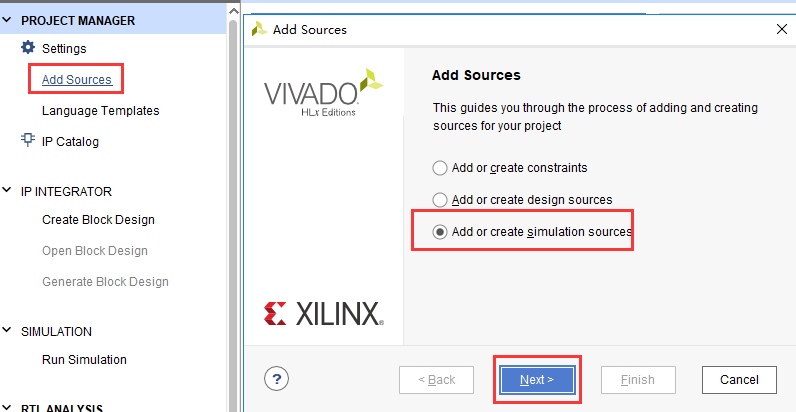

7.3 添加激勵測試文件,點擊Project Manager下的Add Sources圖標,按下圖設置后單擊Next。

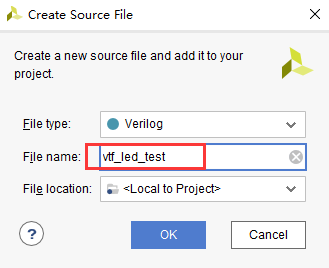

7.4 點擊Create File生成仿真激勵文件。

在彈出的對話框中輸入激勵文件的名字,這里我們輸入名為vtf_led_test。

7.5 點擊Finish按鈕返回。

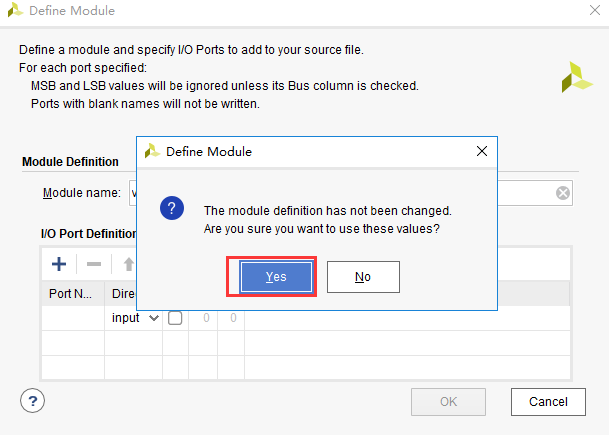

這里我們先不添加IO Ports,點擊OK。

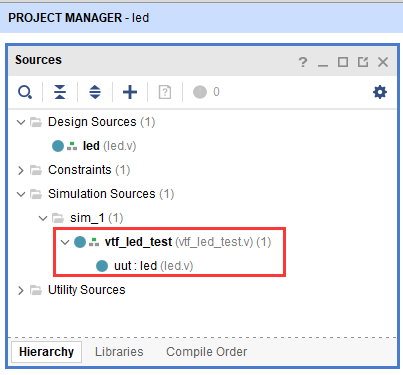

在Simulation Sources目錄下多了一個剛才添加的vtf_led_test文件。雙擊打開這個文件,可以看到里面只有module名的定義,其它都沒有。

7.6 接下去我們需要編寫這個vtf_led_test.v文件的內(nèi)容。首先定義輸入和輸出信號,然后需要實例化led_test模塊,讓led_test程序作為本測試程序的一部分。再添加復位和時鐘的激勵。完成后的vtf_led_test.v文件如下:

`timescale1ns/1ps ////////////////////////////////////////////////////////////////////////////////// // Module Name: vtf_led_test ////////////////////////////////////////////////////////////////////////////////// module vtf_led_test; // Inputs reg sys_clk; reg rst_n ; // Outputs wire[3:0] led; // Instantiate the Unit Under Test (UUT) led uut ( .sys_clk(sys_clk), .rst_n(rst_n), .led(led) ); initial begin // Initialize Inputs sys_clk =0; rst_n =0; #1000; rst_n =1; end //Create clock always#20 sys_clk =~ sys_clk; endmodule

7.7 編寫好后保存,vtf_led_test.v自動成了這個仿真Hierarchy的頂層了,它下面是設計文件led_test.v。

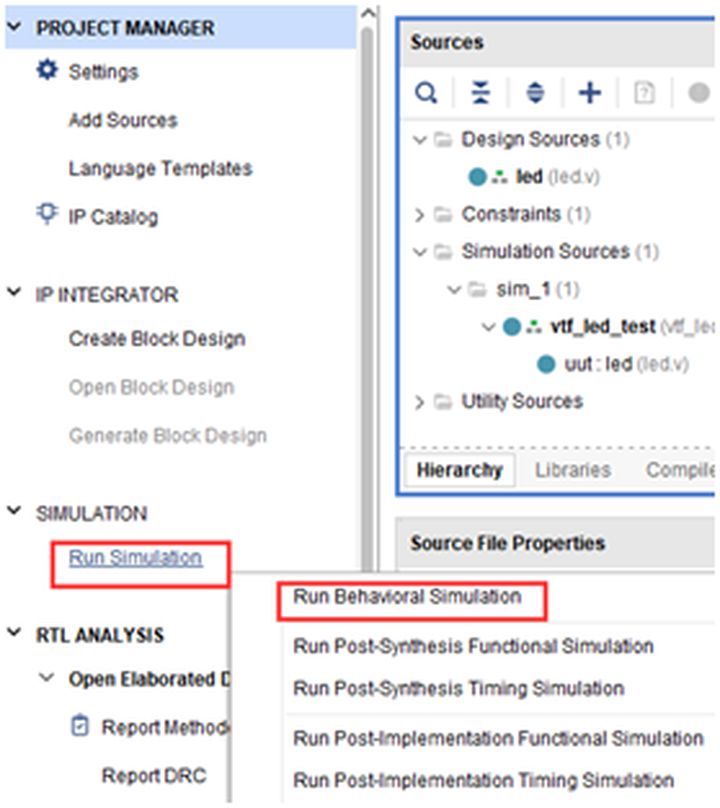

7.8 點擊Run Simulation按鈕,再選擇Run Behavioral Simulation。這里我們做一下行為級的仿真就可以了。

如果沒有錯誤,Vivado中的仿真軟件開始工作了。

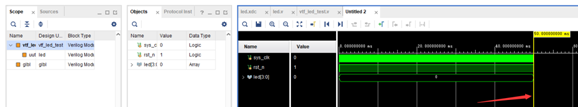

7.9 在彈出仿真界面后如下圖,界面是仿真軟件自動運行到仿真設置的50ms的波形。

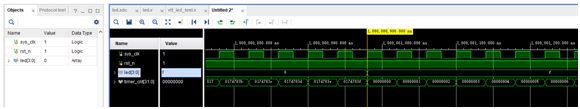

由于LED[3:0]在程序中設計的狀態(tài)變化時間長,而仿真又比較耗時,在這里觀測timer[31:0]計數(shù)器變化。把它放到Wave中觀察(點擊Scope界面下的uut,再右鍵選擇Objects界面下的timer,在彈出的下拉菜單里選擇Add Wave Window)。

添加后timer顯示在Wave的波形界面上,如下圖所示。

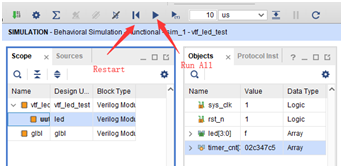

7.10 點擊如下標注的Restart按鈕復位一下,再點擊Run All按鈕。(需要耐心!!!),可以看到仿真波形與設計相符。(注意:仿真的時間越長,仿真的波形文件占用的磁盤空間越大,波形文件在工程目錄的xx.sim文件夾)

我們可以看到led的信號會變成f,說明LED燈會由亮變滅。

8. 下載

8.1 連接好開發(fā)板的JTAG接口,給開發(fā)板上電

注意拔碼開關要選擇JTAG模式,也就是全部拔到”O(jiān)N”,“ON”代表的值是0,不用JTAG模式,下載會報錯。

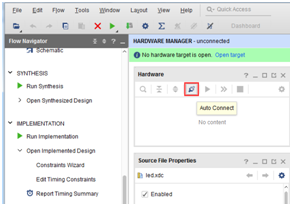

8.2 在“HARDWARE MANAGER”界面點擊“Auto Connect”,自動連接設備

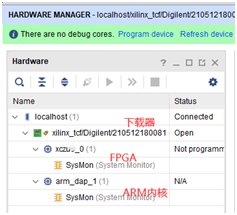

8.3 可以看到JTAG掃描到arm和FPGA內(nèi)核

8.4 選擇芯片,右鍵“Program Device...”

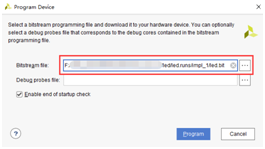

8.5 在彈出窗口中點擊“Program”

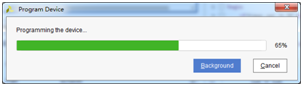

8.6 等待下載

8.7 下載完成以后,我們可以看到PL LED開始每秒變化一次。到此為止Vivado簡單流程體驗完成。后面的章節(jié)會介紹如果把程序燒錄到Flash,需要PS系統(tǒng)的配合才能完成,只有PL的工程不能直接燒寫Flash。在”體驗ARM,裸機輸出”Hello World”一章的常見問題中有介紹。

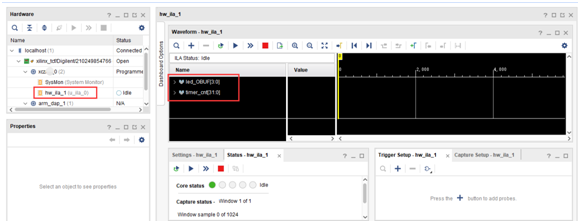

9. 在線調(diào)試

前面介紹了仿真和下載,但仿真并不需要程序燒寫到板子,是比較理想化的結果,下面介紹Vivado在線調(diào)試方法,觀察內(nèi)部信號的變化。Vivado有內(nèi)嵌的邏輯分析儀,叫做ILA,可以用于在線觀察內(nèi)部信號的變化,對于調(diào)試有很大幫助。在本實驗中我們觀察timer_cnt和led的信號變化。

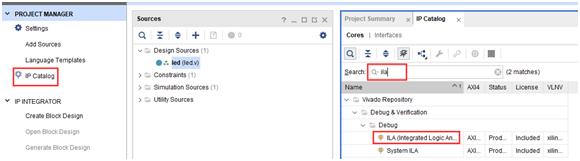

9.1 添加ILA IP核

9.1.1 點擊IP Catalog,在搜索框中搜索ila,雙擊ILA的IP

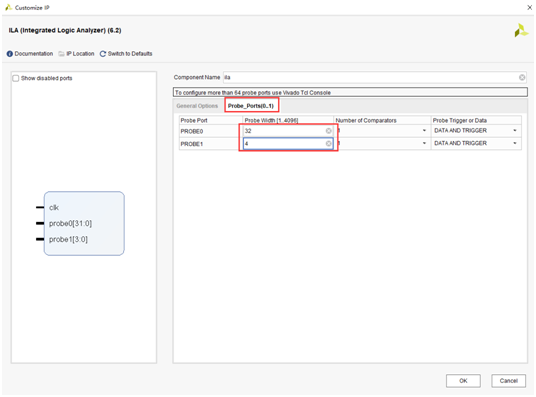

9.1.2 修改名稱為ila,由于要采樣兩個信號,Probes的數(shù)量設置為2,Sample Data Depth指的是采樣深度,設置的越高,采集的信號越多,同樣消耗的資源也會越多。

9.1.3 在Probe_Ports頁面,設置Probe的寬度,設置PROBE0位寬為32,用于采樣timer_cnt,設置PROBE1位寬為4,用于采樣led。點擊OK

彈出界面,選擇OK

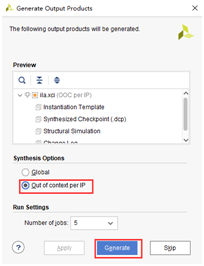

再如下設置,點擊Generate

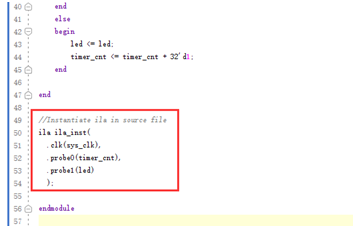

9.1.4 在led.v中例化ila,并保存

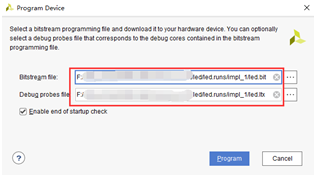

9.1.5 重新生成Bitstream

9.1.6 下載程序

9.1.7 這時候看到有bit和ltx文件,點擊program

9.1.8 此時彈出在線調(diào)試窗口,出現(xiàn)了我們添加的信號

點擊運行按鈕,出現(xiàn)信號的數(shù)據(jù)

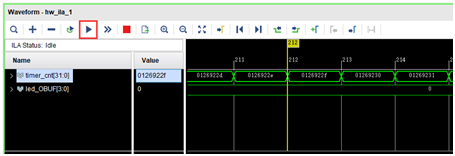

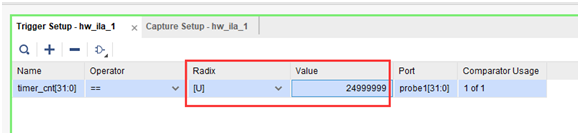

也可以觸發(fā)采集,在Trigger Setup窗口點擊“+”,深度選擇timer_cnt信號

將Radix改為U,也就是十進制,在Value中設置為24999999,也就是timer_cnt計數(shù)的最大值

再次點擊運行,即可以看到觸發(fā)成功,此時timer_cnt顯示為十六進制,而led也在此時翻轉。

9.2 MARK DEBUG

上面介紹了添加ILA IP的方式在線調(diào)試,下面介紹在代碼中添加綜合屬性,實現(xiàn)在線調(diào)試。

9.2.1 首先打開led.v,將ila的例化部分注釋掉

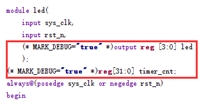

9.2.2 在led和timer_cnt的定義前面添加(* MARK_DEBUG=”true” *),保存文件。

9.2.3 點擊綜合

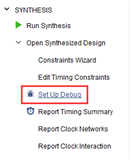

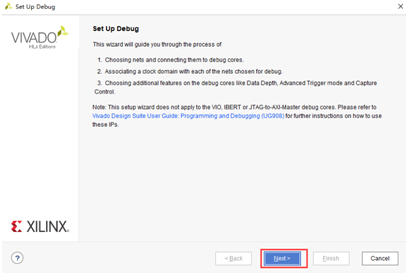

9.2.4 綜合結束后,點擊Set Up Debug

9.2.5 彈出的窗口點擊Next

按照默認點擊Next

采樣深度窗口,選擇Next

點擊Finish

點擊保存

在xdc文件中即可看到添加的ila核約束

9.2.6 重新生成bitstream

9.2.7 調(diào)試方法與前面一樣,不再贅述。

10. 實驗總結

本章節(jié)介紹了如何在PL端開發(fā)程序,包括工程建立,約束,仿真,在線調(diào)試等方法,在后續(xù)的代碼開發(fā)方式中皆可參考此方法。

審核編輯:何安

-

led

+關注

關注

242文章

23849瀏覽量

674485

發(fā)布評論請先 登錄

如何在樹莓派上安裝并運行 Arduino 集成開發(fā)環(huán)境!

如何在 Raspberry Pi AI Camera 上構建為開發(fā)人員提供實時的智能應用程序!

如何在 樹莓派 上編寫和運行 C 語言程序?

零基礎入門:如何在樹莓派上編寫和運行Python程序?

基于QT開發(fā)國產(chǎn)主板終端桌面程序 高效、穩(wěn)定、跨平臺的解決方案

如何在TMS320DM643x器件上使用EDMA3驅動程序

PICO-IMX8PL和SRG-IMX8PL:共創(chuàng)您的物聯(lián)網(wǎng)集成網(wǎng)關

如何在PL端開發(fā)程序

如何在PL端開發(fā)程序

評論