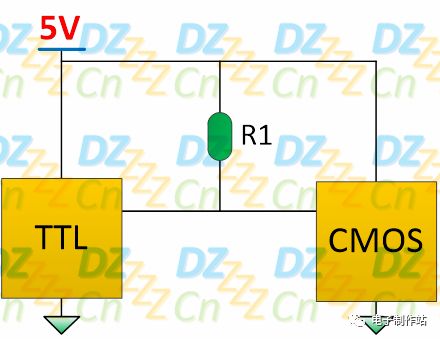

除了前一節(jié)討論的拉電阻基本使用方法外,上拉電阻也可以提升高電平的電壓閾值,以便于前后級信號相匹配,比如,TTL邏輯電平驅(qū)動CMOS邏輯電平時,我們通常會添加一個上拉電阻R1,如下圖所示:

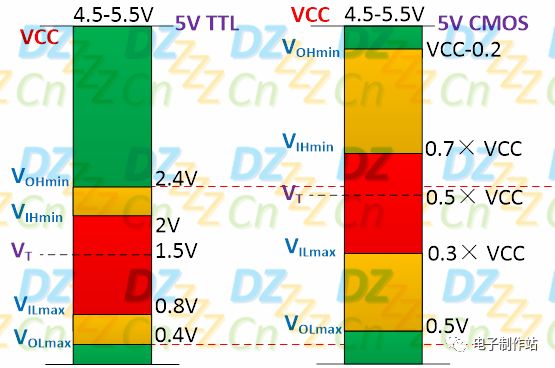

But Why? 我們先來看看TTL電平標準圖與CMOS電平標準圖,如下圖所示:

可以看到,TTL邏輯輸出的低電平最大值VOLMAX(0.4V)小于CMOS邏輯輸入低電平最大值VILMAX(0.3×VCC=1.5V),因此,TTL低電平驅(qū)動CMOS邏輯是完全沒有問題的,但是TTL邏輯輸出的高電平最小值VOHMIN(2.4V)卻低于CMOS邏輯輸入高電平的最小值VIHMIN(0.7×VCC=3.5V),換言之,CMOS邏輯可能不能夠識別TTL邏輯高電平(注意“可能”這兩個字)。

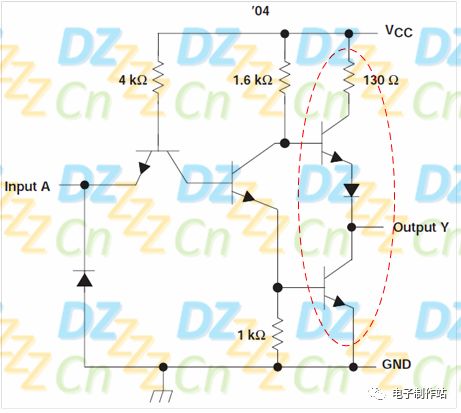

那為什么添加上拉電阻后就能夠使TTL邏輯可靠驅(qū)動CMOS邏輯呢?我們看看TTL邏輯電路的輸出結構,如下圖的所示:(下圖來自TI公司六反相器7404數(shù)據(jù)手冊)

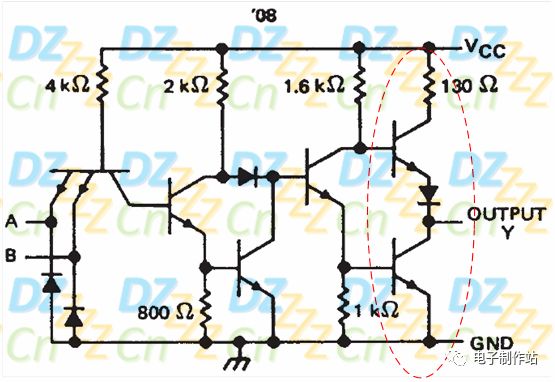

事實上,所有TTL邏輯輸出結構都是一致的,如下圖所示2輸入與門:(下圖來自TI公司四個兩輸入與門7408數(shù)據(jù)手冊)。

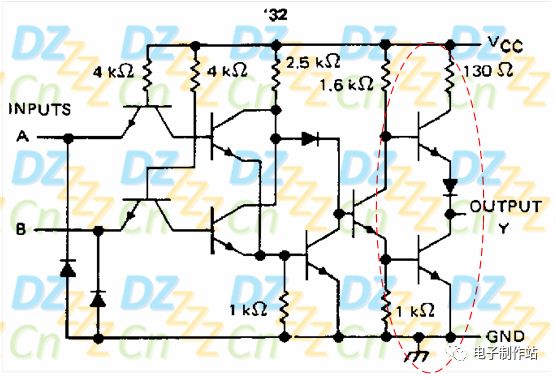

如下圖所示2輸入或門:(下圖來自TI公司四個兩輸入或門7432數(shù)據(jù)手冊)。

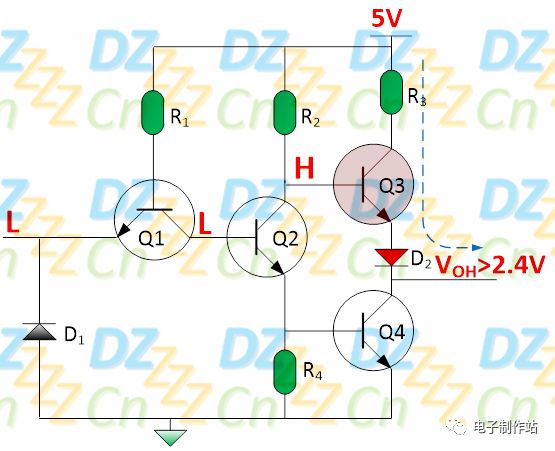

其它TTL邏輯輸出結構也是類似的,此處不再贅述。TTL邏輯輸出為高電平時內(nèi)部狀態(tài)如下圖所示:

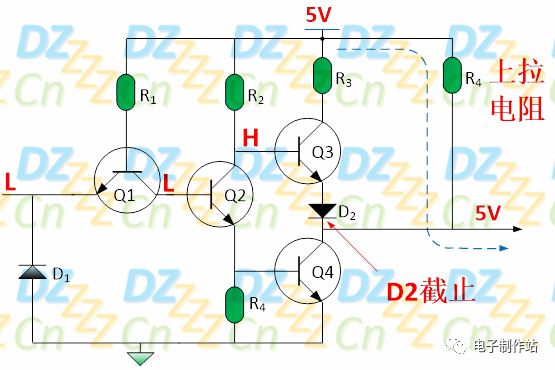

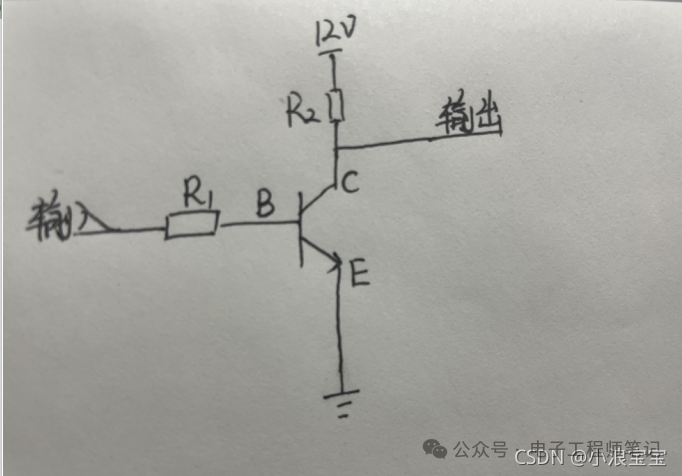

按照TTL電平標準,輸出高電平VOH至少2.4V(VOHMIN=2.4V),換言之,這個輸出電壓也可能高于或低于CMOS高電平輸入識別閾值最小值3.5V(不可靠),而添加上拉電阻后的TTL邏輯電路狀態(tài)如下圖所示:

由于上拉電阻R4的存在,使得三極管Q3與二極管D2都處于截止狀態(tài),因此輸出電平被上拉至5V高電平,妥妥地超過了CMOS邏輯高電平判斷閾值的最小值( 3.5V),這樣CMOS邏輯電路就能夠可靠地進行高電平判斷。

但是,反過來CMOS邏輯電平能夠可靠地驅(qū)動TTL邏輯電平,讀者可自行對照兩者的邏輯電平標準圖就真相大白了。

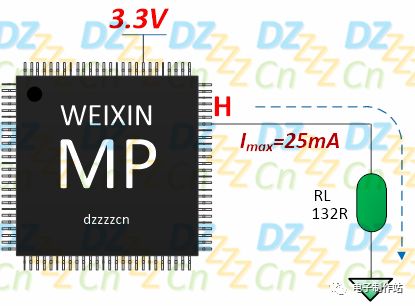

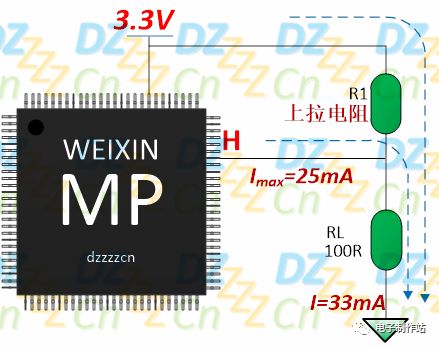

上拉電阻也可以提升單片機引腳的高電平驅(qū)動能力。前面我們已經(jīng)介紹過,任何單片機的IO引腳的驅(qū)動電流都是有限的(比如,STM32單片機引腳的驅(qū)動能力為25mA),如下圖所示:

3.3V單片機IO引腳最大可以驅(qū)動約132歐姆的電阻(負載),如果驅(qū)動的電阻小于132歐姆,輸出高電平“H”就因電流驅(qū)動能力不足而使得輸出電壓下降,這時我們可以添加一個上拉電阻,如下圖所示:

100歐姆負載需要約33mA的驅(qū)動電流,但單片機IO引腳只有25mA可以提供,額外的8mA將由3.3V直流電源通過上拉電阻R1提供。

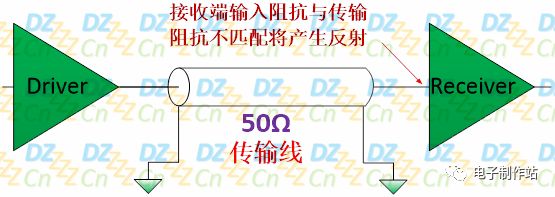

在高速數(shù)字設計電路中,信號的傳輸路徑可用傳輸線來表征,一般差分傳輸線阻抗約100歐姆左右,單端傳輸線的阻抗約為50歐姆左右,如果接收端的輸入阻抗與傳輸線阻抗不匹配(匹配就是相等的意思),則會引起信號反射,如下圖所示:

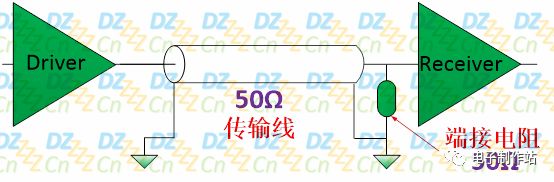

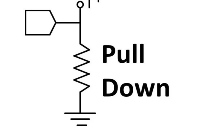

事實上,大多數(shù)接收端的輸入阻抗遠大于傳輸線阻抗,將傳輸線出來的信號直接與接收端對接必定將產(chǎn)生反射,從而引起信號完整性(Signal Integrity, SI)問題,因此,我們通常都會使用各種端接手段進行阻抗的匹配,添加下拉電阻就是其中一個手段,如下圖所示:

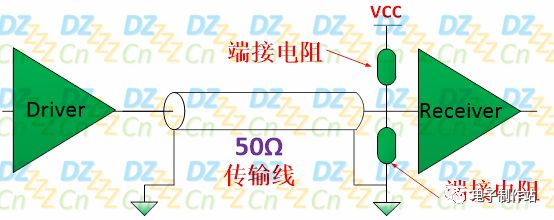

也可以使用上下拉電阻配合的方式進行阻抗的匹配(遠端戴維南端接),如下圖所示:

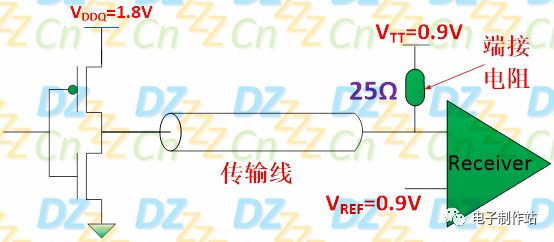

如果讀者有過DDRII SDRAM的應用經(jīng)驗,會發(fā)現(xiàn)其中有一個VTT電壓,如下圖所示:

VTT就是端接電壓(termination voltage),它通常是VDDQ的一半。差分傳輸線的端接原理也是相似的,至于更多細節(jié)方面可參考系列文章《高速數(shù)字邏輯電平標準之SSTL》及《高速PCB設計之端接》,此處不再贅述。

我們在說某個電阻是上拉電阻或下拉電阻的時候,它其實還同時有限制電流的能力,只不過在使用拉電阻過程中,上拉或下拉的功能占主導地位,也因此而得名,你可以把端接電阻稱為上拉電阻或下拉電阻,但你總不會稱其為限流電阻吧?

責任編輯:xj

原文標題:上/下拉電阻

文章出處:【微信公眾號:玩轉(zhuǎn)單片機】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

-

CMOS

+關注

關注

58文章

5988瀏覽量

238066 -

電阻

+關注

關注

87文章

5606瀏覽量

174326 -

TTL

+關注

關注

7文章

531瀏覽量

71446

原文標題:上/下拉電阻

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

浮思特 | 電子電路下拉電阻詳解:原理、計算與應用指南

三極管下拉電阻設計:穩(wěn)定與效率的平衡藝術

請問ADS1278配置管腳的上拉下拉電阻阻值選擇多少?

PGA411在設計的時候必須配置上拉和下拉電阻嗎?可否直接連到電源和地上?

DAC101S101初次上電瞬間下拉電阻的開關是默認閉合的嗎?

DDC264還沒閉合開關測量信號時,讀出的是滿量程的數(shù)據(jù),是這下拉電阻的影響嘛?

TLV320AIC3100原理圖,音頻輸入電路MIC的上拉電阻R1303和下拉電阻R1304是否需要?

【RS-485總線】詳解RS-485上下拉電阻的選擇

上/下拉電阻詳解

上/下拉電阻詳解

評論