在高速PCB設計中,“信號”始終是工程師無法繞開的一個知識點。不管是在設計環(huán)節(jié),還是在測試環(huán)節(jié),信號質量都值得關注。在本文中,我們主要來了解下影響信號質量的5大問題。

根據(jù)目前工作的結論,信號質量常見的問題主要表現(xiàn)在五個方面:過沖,回沖,毛刺,邊沿,電平。

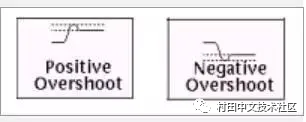

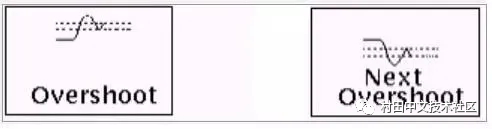

01 過沖

過沖圖

過沖帶來的問題是容易造成器件損壞,過沖過大也容易對周圍的信號造成串擾。造成過沖大的原因是不匹配,消除的方法有始端串電阻或末端并阻抗(或電阻)。

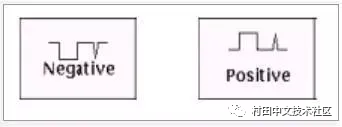

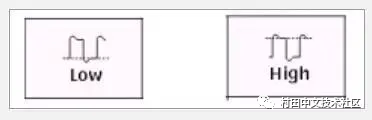

02 毛刺

毛刺圖

毛刺作用在高速器件上,容易造成誤觸發(fā)、控制信號控制錯誤或時鐘信號相位發(fā)生錯誤等問題,毛刺脈沖帶來的問題多發(fā)生在單板工作不穩(wěn)定或器件替代后出現(xiàn)問題。造成毛刺的原因很多,比如邏輯冒險,串擾、地線反彈等,其消除的方法也不盡相同。

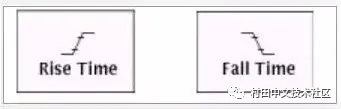

03 邊沿

邊沿圖

邊沿速度緩慢發(fā)生在信號線上時,會造成數(shù)據(jù)采樣錯誤。其產(chǎn)生原因通常是輸出端容性負載過大(負載數(shù)量過多),輸出是三態(tài)時充(放)電電流小等原因。

04 回沖

回沖圖

回沖產(chǎn)生的原因是信號線不匹配或多負載等原因,消除的方法是加匹配電阻或調整總線的拓撲結構。

05 電平

電平圖

輸入電平幅度不符合要求時,會造成器件輸出錯誤。導致電平異常的原因主要有:輸出過載,電平不匹配,三態(tài)總線、總線沖突等原因。

擴展

工程師在進行信號質量測試時,應該具備以下三方面的知識:

1)對測量工具(示波器)有清楚的了解,要了解示波器的性能,掌握示波器及其探頭的使用,清楚信號質量異常的測試與示波器菜單設置間的配合關系。

2)對異常的信號形式有全面和清楚的認識,對異常信號的異常指標有了解。

3)對被測單板的原理電路有一定的認識和了解,要求能夠對信號進行分類,了解板上的關鍵器件、關鍵總線、關鍵信號的信號質量要求和相關時序參數(shù)。

責任編輯:lq

-

pcb

+關注

關注

4367文章

23489瀏覽量

409600 -

阻抗

+關注

關注

17文章

972瀏覽量

47353 -

信號質量

+關注

關注

0文章

9瀏覽量

6892

原文標題:高速PCB設計中影響信號質量的5個方面

文章出處:【微信號:murata-eetrend,微信公眾號:murata-eetrend】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

PCB設計如何用電源去耦電容改善高速信號質量

DDR模塊的PCB設計要點

揭秘PCB阻抗在高速信號傳輸中的重要性

LVDS連接器PCB設計與制造

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

高速PCB設計EMI防控手冊:九大關鍵步驟詳解

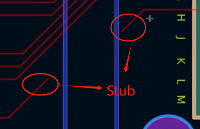

PCB設計中的Stub對信號傳輸?shù)挠绊?/a>

高速PCB設計指南

高速PCB設計中影響信號質量的5大問題

高速PCB設計中影響信號質量的5大問題

評論