作為一名電子人,咱們都知道隨著摩爾定律的提出,為半導體產業指明了之后幾十年的發展之路。然而許多人不知道的是,其實就在同一篇論文里,這位“預言家”甚至早已洞悉了摩爾定律之后的半導體創新法寶哦

我們的創始人戈登·摩爾于1965年發表了題為“將更多組件裝入集成電路”的論文。這是一篇短小精悍的著名論文,只有四頁,且配有插圖。論文第二頁包含被稱為摩爾定律的金句:

“因最大限度降低組件成本造成的復雜性大約每年增加兩倍。短期來看,這一增速有望延續、甚至提高。長遠來看,增速尚不明確,盡管沒理由認為在未來至少 10年內它會有任何變化。”

摩爾預測如今仍在持續的半導體技術的指數級增長將持續 50年以上,而非短短 10年!論文第三頁繼續表示,通過在單個封裝中集成小組件可能更有利于構建更大的系統:

“使用獨立封裝并彼此互聯的更小的功能組件構建大型系統可能更為經濟。大型功能的可用性結合功能性設計和構造,應有助于大型系統制造商快速、經濟地設計和制造各種設備。”

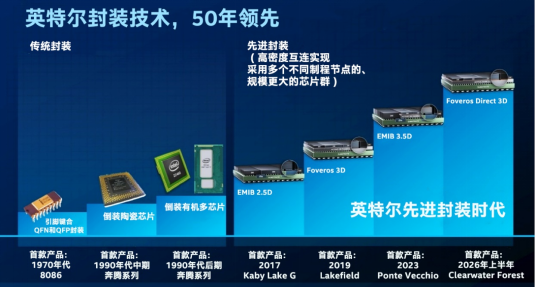

1965 年,戈登·摩爾就已洞悉到芯片級異構集成將引領未來發展。英特爾目前正朝這一方向努力:使用高級封裝將公司的所有技術整合到一個IC封裝中。

異構集成分為三個層級。這是一個簡單分類法。首先是芯片層級(器件層級)的異構集成。其次是系統層級的異構集成。最后是軟件層級的異構性。所有三個層級的異構性帶來系統的可重配置性。

第一層級:芯片異構性

芯片級異構性指器件封裝內部的異構集成,與小芯片 (chiplet) 的概念緊密相關。我們正在構建更復雜、更大的系統,而使用大型的單片半導體構建更大系統較為困難。大芯片的成品率不及小芯片。小組件在構建這些系統方面有著顯著的實用性和經濟性優勢。從系統的角度來看,使用小芯片無需為后續每個半導體制程節點重新設計每個小芯片,因而有助于我們做出更明智的半導體設計決策。某些功能以其現有形式可以完美運行。當有新技術節點上線時,沒必要重新設計這些功能。

異構集成已應用到生產中。這是一項非常重要的技術,英特爾堅定實施基于小芯片的設計策略。例如,英特爾 Stratix 10 FPGA 和英特爾Agilex FPGA 基于異構集成,且這些器件現已投入生產。實際上,英特爾 Stratix 10 FPGA 多年來一直在批量生產。

基于小芯片的 IC 設計和制造支持英特爾構建具有芯片驗證功能的系統,包括高速串行收發器、內存接口、以太網和 PCIe 端口等。基于小芯片的設計還有助于英特爾為不同工作負載開發目標架構,并將其更快地推向市場。

由于這些原因,英特爾積極支持構建以小芯片為核心的行業生態系統。為此,我們采取了多項舉措。例如:

英特爾開發了嵌入式多芯片互連橋接 (EMIB) 技術,該技術用于使用標準化互連方法對小芯片進行互連。

英特爾開發了高級接口總線 (AIB),英特爾發布的這一 PHY 是一種免版稅的開源高性能小芯片互連技術。

英特爾最近加入了 CHIPS(接口、處理器和系統的通用硬件)聯盟,該行業合作組織致力于推進基于小芯片的開發項目。

第二層級:系統異構性

第二個異構集成層級是系統層級。今天,我們生活在以數據為中心的世界中。數據無處不在。英特爾正大力推動系統級創新,以幫助高效管理海量數據。我們需要對這些數據進行許多操作,包括移動、存儲和處理。與這些任務相關的工作負載需要許多解決方案,英特爾開發并制造了大量器件來執行這些任務,包括 CPU、GPU、ASIC、FPGA 等,我們使用這些器件來構建異構系統。

這些不同的工作負載需要不同的處理架構。標量工作負載在 CPU 上可高效運行。矢量工作負載在 GPU 上可高效運行。AI 和機器學習等矩陣工作負載通常可在工作負載特定 ASIC 上實現最高運行效率。最后,空間工作負載最適合在 FPGA 上運行。因此,我們需要將所有這些可用異構架構進行組合,以高效支持數據中心中的特定工作負載。將 CPU、GPU、FPGA 和專用加速器整合起來,可幫助英特爾及其客戶智能、高效地解決問題。

第三層級:軟件異構性

第三種異構集成在軟件層級。這種集成較難實現。英特爾的方法被稱為oneAPI 計劃基于標準的跨行業開放統一編程模型,為當前構建軟件提供了基本思路。該方法與烹飪有相似之處。在廚房里,您不會問廚師是否有“烹飪”食物的特定方式。他們有許多烹飪手法,通過綜合運用各種廚具、精選食材和專心準備烹制各種美味佳肴。

同樣,我認為我們將會繼續使用多種編程和描述語言。開發人員需要一個統一的開發環境。這就是英特爾推出 oneAPI 計劃的宗旨和愿景。英特爾將前述四種工作負載類型納入這一愿景中,即標量、矢量、矩陣和空間。oneAPI 計劃提出了一個抽象層級,軟件開發人員理論上可以在一層中開發代碼,然后將該代碼部署到上面提到的許多處理架構中。

目前,這只是一個開始。英特爾不久前剛剛宣布了開源 oneAPI 計劃,以及測試版英特爾 oneAPI 工具套件。我們認為英特爾 oneAPI 工具套件的開發前路漫漫,我們對自己選擇的道路深信不疑。

今天,我們擁有面向英特爾 oneAPI 工具套件的 Data Parallel C++ 和資源庫。Data Parallel C++ 整合了 Khronos Group 的 SYCL,支持數據并行性和異構編程。Data Parallel C ++ 支持開發人員使用基于常用 C ++ 結構的“單源”風格為異構處理器編寫代碼。

融合三個異構層級

英特爾深知這三種異構性層級對行業非常重要。正因如此,我們重視在芯片層級開發高級封裝技術,在系統層級整合多種處理架構,在軟件層級推出 oneAPI 計劃、英特爾 oneAPI 統一編程環境和 Data Parallel C ++ 編程語言。在英特爾看來,半導體是一個大產業,衍生出許多新興市場,例如機器學習、人工智能和 5g,這些市場的企業需要靈活應對接口和工作負載方面的快速變化。FPGA 具有極高的靈活性,因此在這些市場的早期發展階段可發揮重要作用。

隨著這些市場的壯大,為這些市場開發系統的公司通常會開發定制 ASIC。為滿足這些市場的需求,英特爾推出了功耗更低、性能更高的英特爾 eASIC 和完全定制的 ASIC。隨著市場日趨成熟和產量增加,英特爾開發流程支持從 FPGA 順利過渡到兼容引腳的英特爾 eASIC 器件,并最終過渡到 ASIC。

英特爾 eASIC 器件在數據中心內也能高效運行,數據中心的多種應用和特定工作負載都需要加速。用 FPGA 實現的加速器設計可成為基于英特爾 eASIC 技術的小芯片。該小芯片相比 FPGA 可實現更快速度和使用更低功耗,通過 AIB 或其他互連方法可與其他器件集成到一個封裝中。

責任編輯:xj

原文標題:你只知道摩爾定律?摩爾同時提出的這一觀點也正在被驗真

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1643文章

21981瀏覽量

614534 -

英特爾

+關注

關注

61文章

10176瀏覽量

174028 -

摩爾定律

+關注

關注

4文章

638瀏覽量

79707

原文標題:你只知道摩爾定律?摩爾同時提出的這一觀點也正在被驗真

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

英特爾以系統級代工模式促進生態協同,助力客戶創新

英特爾持續推進核心制程和先進封裝技術創新,分享最新進展

英特爾代工:明確重點廣合作,服務客戶鑄信任

英特爾借助開放生態系統,加速邊緣AI創新

英特爾為企業智能化發展注入新動力

英特爾構建AI PC新平臺,引領AI應用新生態

英特爾考慮出售Altera股權

英特爾和AMD組建x86生態系統咨詢小組

英特爾將攜手AMD共同捍衛x86生態

高通探索收購英特爾芯片設計業務的可能性

英特爾醞釀出售Mobileye股權以應對挑戰

芯海科技edge BMC首秀2024英特爾網絡與邊緣計算行業峰會

英特爾積極支持構建以小芯片為核心的行業生態系統

英特爾積極支持構建以小芯片為核心的行業生態系統

評論