我們不斷向先進(jìn)的CMOS的微縮和新存儲(chǔ)技術(shù)的轉(zhuǎn)型,導(dǎo)致半導(dǎo)體器件結(jié)構(gòu)的日益復(fù)雜化。例如,在3D NAND內(nèi)存中,容量的擴(kuò)展通過(guò)垂直堆棧層數(shù)的增加來(lái)實(shí)現(xiàn),在保持平面縮放比例恒定的情況下,這帶來(lái)了更高深寬比圖形刻蝕工藝上的挑戰(zhàn),同時(shí)將更多的階梯連接出來(lái)也更加困難。人們通過(guò)獨(dú)特的整合和圖案設(shè)計(jì)方案來(lái)解決工藝微縮帶來(lái)的挑戰(zhàn),但又引入了設(shè)計(jì)規(guī)則方面的難題。

二維 (2D) 設(shè)計(jì)規(guī)則檢查 (DRC) 已不足以用來(lái)規(guī)范設(shè)計(jì)以達(dá)成特定性能和良率目標(biāo)的要求。同時(shí)完全依賴(lài)實(shí)驗(yàn)設(shè)計(jì) (DOE) 來(lái)進(jìn)行工藝表征和優(yōu)化也變得難以操作。以往工程師通過(guò)運(yùn)用DOE實(shí)驗(yàn)來(lái)節(jié)省工藝研發(fā)的成本和時(shí)間,而現(xiàn)在他們需要進(jìn)行數(shù)以百計(jì)的DOE才能達(dá)到目的,這反而需要大量的時(shí)間和物料,包括晶圓。

此外,工藝步驟之間非直觀(guān)的交互作用,以及狹窄的工藝窗口,使得使用第一性原理建模來(lái)同時(shí)進(jìn)行性能提升和良率優(yōu)化變得尤為困難。因此需要對(duì)復(fù)雜工藝流程進(jìn)行三維建模理解,而虛擬制造建模平臺(tái)Coventor SEMulator3D為此而生。

SEMulator3D能提供哪些功能?

該軟件可從一系列標(biāo)準(zhǔn)單元工藝步驟中創(chuàng)建3D虛擬工藝整合模型,以模擬工藝流程。SEMulator3D使用完全整合的工藝流程模型,可以預(yù)測(cè)工藝更改對(duì)下游工藝步驟的影響,這在過(guò)去則需要在晶圓廠(chǎng)中依靠“先制造和后測(cè)試”的循環(huán)來(lái)實(shí)現(xiàn)。

例如,工程師可以使用該軟件對(duì)替換金屬柵極 (RMG) FinFET進(jìn)行快速建模,該元件使用先溝槽金屬硬掩模 (TFMHM) 后段制程 (BEOL) 與自對(duì)準(zhǔn)通孔工藝 (SAV)。工程師在完成虛擬加工的3D模型之后,就可以進(jìn)行2D和3D的虛擬測(cè)量和電學(xué)性能參數(shù)提取。

該軟件的電學(xué)分析組件增加了電阻和電容提取功能,有助于理解工藝和設(shè)計(jì)靈敏度。該軟件提供了3D建模和驗(yàn)證電學(xué)性能的快捷平臺(tái)。SEMulator3D中使用了有預(yù)測(cè)性的工藝模型和能精確匹配實(shí)際晶圓的3D結(jié)構(gòu),比其它孤立解決方案中使用的理想化幾何結(jié)構(gòu),更能精確地反映所制造的器件,從而具有更高的精度。

DRAM演示

該演示展現(xiàn)了該平臺(tái)如何根據(jù)刻蝕設(shè)備的性能參數(shù)(如材料的刻蝕選擇比和氣流流向通量分布)的變化對(duì)器件電學(xué)性能進(jìn)行建模,形象地說(shuō)明了虛擬制造的案例。簡(jiǎn)單的DRAM器件案例研究側(cè)重于對(duì)柵極刻蝕行為和刻蝕特征的研究,通過(guò)對(duì)其做合理設(shè)定來(lái)滿(mǎn)足預(yù)先設(shè)定的電學(xué)性能和良率目標(biāo)。

該演示在虛擬制造中使用了典型的工作流程,包括四個(gè)步驟:

1. 一個(gè)標(biāo)準(zhǔn)工藝流程的建立,此藝流程支持工藝校準(zhǔn),然后生成具有預(yù)測(cè)性的3D結(jié)構(gòu)模型。

2. 添加量測(cè)參數(shù),以評(píng)價(jià)器件結(jié)構(gòu)或電學(xué)行為。量測(cè)可能包括幾何尺寸測(cè)量、3D DRC(設(shè)計(jì)規(guī)則檢查)和電學(xué)參數(shù)測(cè)量。

3. 使用DOE(實(shí)驗(yàn)設(shè)計(jì))和校準(zhǔn)。

4. 數(shù)據(jù)分析,包括對(duì)工藝實(shí)現(xiàn)和/或設(shè)計(jì)變更的敏感性分析。

標(biāo)準(zhǔn)工藝流程的建立

該演示的標(biāo)準(zhǔn)工藝流程面向2X DRAM。該工藝由Coventor根據(jù)公開(kāi)數(shù)據(jù)開(kāi)發(fā),未使用客戶(hù)機(jī)密信息

圖1:建立模型之后,電容器接觸點(diǎn)結(jié)果如圖所示。此時(shí)可以進(jìn)行電學(xué)分析,研究電容器的邊緣效應(yīng)。

在本演示中,DRAM的有源區(qū) (AA) 使用自對(duì)準(zhǔn)四重圖形技術(shù) (SAQP) 和傾角20°的光刻-刻蝕-光刻-刻蝕 (LELE或LE2) 對(duì)多余的圖形進(jìn)行去除,其間距為28 nm。掩埋字線(xiàn)使用自對(duì)準(zhǔn)雙重圖形化技術(shù) (SADP),間距為40 nm,位線(xiàn)使用SADP,間距為44 nm。工藝流程在電容器接觸點(diǎn) (CC) 處結(jié)束,這使得軟件可以進(jìn)行電學(xué)分析,并能夠分析電容器中的邊緣效應(yīng)。

添加重要度量

每個(gè)工藝步驟只需要幾個(gè)易于理解和校準(zhǔn)的幾何和物理輸入?yún)?shù)。工作流程的下一步是確定重要量工藝參數(shù)。就像在實(shí)際的晶圓廠(chǎng)一樣,單元工藝參數(shù),如沉積一致性、刻蝕的各向異性和選擇比,他們之間相互影響并與其它設(shè)計(jì)參數(shù)交互作用,最終以復(fù)雜的方式影響最終器件的結(jié)構(gòu)。

SEMulator3D支持添加兩種幾何測(cè)量。第一種是虛擬測(cè)量,支持測(cè)量模型結(jié)構(gòu)并驗(yàn)證結(jié)構(gòu)是否符合預(yù)期尺寸。第二種是結(jié)構(gòu)搜索,相關(guān)步驟可以檢查整個(gè)3D模型或某些部分,以確定測(cè)量極值,如膜厚度、線(xiàn)寬和接觸面積的數(shù)值和位置。它還可以計(jì)算電網(wǎng)組件的數(shù)量,這有助于識(shí)別電網(wǎng)短路或開(kāi)路(圖2)。

圖2:虛擬測(cè)量步驟(頂部)可幫助測(cè)量結(jié)構(gòu),包括CD、刻蝕深度和薄膜厚度。結(jié)構(gòu)搜索步驟(底部)可確定測(cè)量極值,并計(jì)算電網(wǎng)組件的數(shù)量,如識(shí)別網(wǎng)絡(luò)短路或開(kāi)路。

當(dāng)幾何偏差的位置隨工藝的變化而變化時(shí),結(jié)構(gòu)搜索特別有用。例如,圖2顯示了CC和AA之間的接口最小面積。軟件將高亮顯示該位置,而該位置容易成為器件失效的故障點(diǎn)。

器件電學(xué)性能模擬

器件的電學(xué)性能參數(shù)可以通過(guò)器件電學(xué)性能模擬來(lái)提取。通過(guò)使用與圖2相同的模型,該演示可以在SEMulator3D中進(jìn)行器件電學(xué)仿真。

圖3:SEMulator3D可識(shí)別3D結(jié)構(gòu)中的器件端口,并像TCAD中那樣仿真電學(xué)性能,但不需要進(jìn)行耗時(shí)的TCAD建模。

該軟件有助于識(shí)別3D結(jié)構(gòu)中的器件的端口和電極,并模擬器件的特性,如溫度、帶隙和電子/孔遷移率。該軟件允許手動(dòng)和自動(dòng)識(shí)別節(jié)點(diǎn)(一個(gè)或多個(gè)連接在一起的引腳),初始電壓或電流可以與選定節(jié)點(diǎn)的電壓掃描一起設(shè)置。

圖3中的電學(xué)仿真示例顯示了兩個(gè)柵極、兩個(gè)源、一個(gè)漏和一個(gè)襯底。工程師可以自由設(shè)置偏置電壓或初始電壓以及電壓掃描,如DRAM示例偏置電壓表所示。

然后,工程師可以使用該軟件自動(dòng)提取重要電學(xué)性能指標(biāo),如一個(gè)電壓點(diǎn)上的閾值電壓 (Vth)、亞閾值擺幅 (SS)、漏致勢(shì)壘下降 (DIBL) 和開(kāi)啟電流 (ION)。這些功能無(wú)需耗時(shí)和嚴(yán)格的TCAD建模即可實(shí)現(xiàn),同時(shí)可以體現(xiàn)3D工藝變化對(duì)電學(xué)性能的影響。

-

虛擬工藝

+關(guān)注

關(guān)注

0文章

5瀏覽量

6373 -

TCAD

+關(guān)注

關(guān)注

2文章

18瀏覽量

10681

發(fā)布評(píng)論請(qǐng)先 登錄

電機(jī)引線(xiàn)螺栓硬釬焊工藝研究

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

芯片封裝工藝詳解

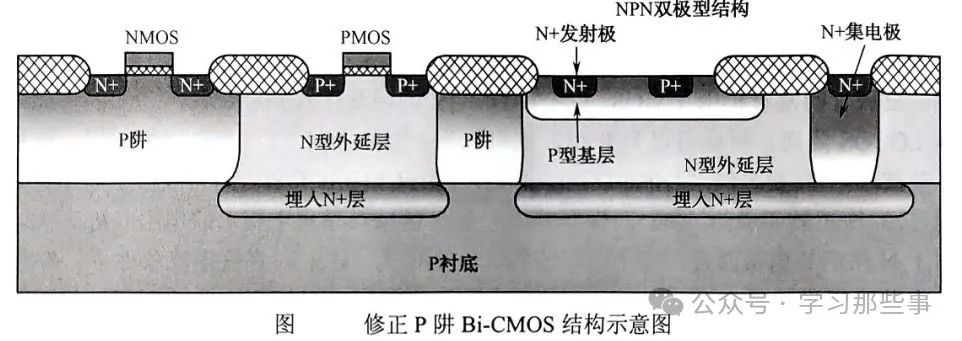

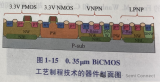

Bi-CMOS工藝解析

焊接工藝過(guò)程監(jiān)測(cè)器的應(yīng)用與優(yōu)化

塑封、切筋打彎及封裝散熱工藝設(shè)計(jì)

請(qǐng)問(wèn)DAC7731的數(shù)字部分是bipolar工藝還是cmos工藝?

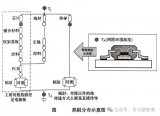

雙阱工藝的制造過(guò)程

如何通過(guò)改善工藝解決電感噪音問(wèn)題

工藝仿真可以分為哪幾個(gè)方面?

BiCMOS工藝制程技術(shù)簡(jiǎn)介

通過(guò)虛擬工藝加速工藝優(yōu)化

通過(guò)虛擬工藝加速工藝優(yōu)化

評(píng)論