弱弱的問下大家,如果一個板子沒有經過仿真只憑借設計工程師的經驗完成了設計,板子加工貼片后測試發現電源紋波超過了要求,你們下一步會做什么?只有再重新設計然后投板回來再測試看看這一條路嗎?

文章的一開始肯定是循例說一些理論知識(干貨),既然本文的內容是講電源紋波噪聲的,我們在SI領域上就必定會提到一個專業名詞,那就是下面這個詞了。

PDN,power delivery network,江湖人稱電源分配網絡,從字面的意思來理解,實際上它是一個泛指,指的是PCB或者系統上的電源網絡。而在我們SI領域中賦予了新的含義,它指的是我們仿真概念中的PDN阻抗,也就是電源網絡的頻域阻抗。下圖是高速先生在多個場合都反復用過的一張圖了。

我們知道,從電源芯片到負載芯片,其實電源網絡會經過幾個典型的地方。首先是從電源芯片出發,會經過電源芯片的封裝,然后電源網絡進入到PCB板上,PCB板上我們都會放置大大小小的電容,然后去到我們負載芯片的pin。對!只是pin,并不是真正的負載位置,因為芯片是要進行封裝的,從pin到die還要經過芯片的封裝,封裝會有電感的產生,電源網絡只有經歷了這重重的考驗才能順利達到真正的負載接收端。所以電源網絡在整段路徑都需要特定的電容才能進行濾波,例如在電源輸出端需要bulk電容,PCB上需要小點的電容,在芯片封裝里面嚴格來說還需要更小的電容,終于通過die內的強力電容完成任務。值得一提的是,不同區域的電容其實它們只能去管到屬于自己的那個頻段而已哈!上面的關于PDN阻抗的原理,雖然高速先生已經多次提起了,但是只要能再讓粉絲們熟記的話,我們是愿意重復再重復的哈。

好,上面快速的講完原理之后,我們正式進入了這個案例。我們SI工程師和硬件測試工程師對于電源噪聲的理解其實是有不同的側重點的。我們更多喜歡在頻域的角度去分析,例如上面所說的PDN阻抗,而硬件測試工程師則喜歡時域的仿真,也就是我們所說的紋波,一般用示波器進行測量。這個差異是由很多因素決定的,這里不再展開了。

回到我們一開頭的問題,我們就有這么一塊已經做出來的板子,硬件工程師測試FPGA上0.85V的電源發現遠遠超過了5%的紋波要求,然后向我們求助。

我們拿到了客戶設計的板子去看該電源網絡的情況,會發現bulk電容和一些大電容都擺放得有點遠,從設計上看其實是沒有做到很完善的。從客戶處了解到,這個項目客戶并沒有找我們進行仿真,只是靠FPGA芯片的設計指導進行布局布線和濾波電容的放置。

大家知道,當一個PCB設計已經完成并且做出來之后,其實里面的很多東西就已經是固定了。例如電源芯片和FPGA芯片的布局、布線、電源反饋點的位置等等,因此肯定做不到把位置遠的電容把它們在做好的板子上去拉近一點這個操作了,同樣也不可能把電源平面再加寬一點或者把電源銅厚再加厚,也不可能把電源反饋點的位置進行變化了。

恩,在大多數的眼中,看起來只能重新進行設計再去制板了。然而高速先生還想再糾結一把,想看看能不能在原有的板子去改動點什么能減小點噪聲。看著看著,高速先生突然關注到了一個點,那就是電容的配置。

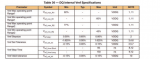

我們看到原來該電源網絡的電容配置是這樣的:

看起來是還可以,從大電容到小電容都是有的,種類也算比較齊全。但是高速先生還想看看它能不能經受我們仿真的考驗。我們通過客戶提供的最大電流進行PDN阻抗的仿真,驚訝的發現,在需要看到的10MHz前的頻域內,現在板子的PDN阻抗在5到6MHz是有明顯的超標,PDN阻抗居然是不滿足要求的。

這樣高速先生就有底氣告訴客戶,我們有希望從電容的配置著手,通過改變電容大小和種類的方法來實現在當前的板子上減小噪聲!

在原有電容位置不能挪動的情況下,我們經過多次迭代仿真,把某些電容的值進行了調整,最終給出的BOM表改成了如下的樣子。

這個時候我們優化后的PDN阻抗曲線就基本滿足目標阻抗了。

最后我們拿著這個優化后的仿真結果去慫恿,哦不是,是鼓勵客戶在原有的板子上更換新BOM表的電容配置,然后加載程序后再次進行測試!

客戶于是滿懷忐忑的心情按照高速先生的建議去做了,結果卻讓他們有了驚喜,紋波測試結果有了明顯的改善,從之前的56mV減小到了43mV,紋波基本滿足了5%的波動要求。

簡單總結下本文章的核心內容哈,那就是在電容的位置不能改變,布局布線也不能變化的情況下,最重要的是在無需重新設計和投板的前提下,我們僅僅通過PDN阻抗仿真優化來調整電容的配置來達到減小噪聲、滿足紋波測試標準的目標,為客戶節省了大量的成本和研發時間。

審核編輯:符乾江

-

電容

+關注

關注

100文章

6228瀏覽量

153213 -

功率設計

+關注

關注

0文章

21瀏覽量

3484

發布評論請先 登錄

電容的特性與ESR對紋波的影響(可下載)

實用干貨:降低電流紋波的有效妙招

ADS1675只要工作在大于等于1M的采樣率的時候,AD采集回來的波形就很爛,為什么?

電源紋波是什么_電源紋波多少算正常

只要電容配得好,紋波自然就很小

只要電容配得好,紋波自然就很小

評論