一、計(jì)算機(jī)架構(gòu)在了解計(jì)算機(jī)架構(gòu)之前,我們先來(lái)認(rèn)識(shí)幾位對(duì)計(jì)算機(jī)的發(fā)明做出關(guān)鍵共享的幾位大佬。

1. 巴貝奇機(jī)械計(jì)算機(jī)之父,英國(guó)貴族,曾孤軍奮戰(zhàn)下造出的第一臺(tái)差分機(jī),運(yùn)算精度達(dá)到了6位小數(shù),后來(lái)又設(shè)計(jì)了20位精度的差分機(jī),其設(shè)計(jì)理念已經(jīng)達(dá)到了機(jī)械設(shè)計(jì)登峰造極的境界。

1985~1991年,倫敦科學(xué)博物館為了紀(jì)念巴貝奇誕辰200周年,根據(jù)其1849年的設(shè)計(jì),用純19世紀(jì)的技術(shù)成功造出了差分機(jī)2號(hào)。

巴貝奇堪稱(chēng)上個(gè)世紀(jì)最強(qiáng)大腦,他的大腦現(xiàn)保存在英國(guó)科學(xué)博物館。

程序員的祖師奶奶Ada正是在和巴貝奇共同工作時(shí)提出了程序循環(huán)分支等等我們現(xiàn)在都習(xí)以為常的編程理念。

差分機(jī)

2. 圖靈被稱(chēng)為計(jì)算機(jī)科學(xué)之父,人工智能之父。1931年圖靈進(jìn)入劍橋大學(xué)國(guó)王學(xué)院,畢業(yè)后到美國(guó)普林斯頓大學(xué)攻讀博士學(xué)位,第二次世界大戰(zhàn)爆發(fā)后回到劍橋,后曾協(xié)助軍方破解德國(guó)的著名密碼系統(tǒng)Enigma,幫助盟軍取得了二戰(zhàn)的勝利。圖靈對(duì)于人工智能的發(fā)展有諸多貢獻(xiàn),提出了一種用于判定機(jī)器是否具有智能的試驗(yàn)方法,即圖靈試驗(yàn),至今,每年都有試驗(yàn)的比賽。

圖靈在戰(zhàn)時(shí)服務(wù)的機(jī)構(gòu)于1943年研制成功的CO-LOSSUS(巨人)機(jī),這臺(tái)機(jī)器的設(shè)計(jì)采用了圖靈提出的某些概念。它用了1500個(gè)電子管,采用了光電管閱讀器;利用穿孔紙帶輸入;并采用了電子管雙穩(wěn)態(tài)線(xiàn)路,執(zhí)行計(jì)數(shù)、二進(jìn)制算術(shù)及布爾代數(shù)邏輯運(yùn)算,巨人機(jī)共生產(chǎn)了10臺(tái),用它們出色地完成了密碼破譯工作。

強(qiáng)烈推薦這部根據(jù)圖靈生平改編的電影《模仿游戲》,一起感受下這個(gè)絕世天才不平凡的一生。

模仿游戲

3. 馮諾依曼-《計(jì)算機(jī)與人腦》計(jì)算機(jī)架構(gòu)主要有兩種:哈佛架構(gòu)、馮諾依曼架構(gòu)。現(xiàn)代計(jì)算機(jī),大部分都是基于馮諾依曼體系結(jié)構(gòu)。

我個(gè)人認(rèn)為馮諾依曼應(yīng)該是上個(gè)世紀(jì)「最聰明的人,沒(méi)有之一」。

他的個(gè)人成就在此就不說(shuō)了,大家可以自行搜索,很多成就,一口君連名字都看不懂,只有博弈論還勉強(qiáng)知道是啥意思。

本文只討論大神對(duì)計(jì)算機(jī)的貢獻(xiàn)【其實(shí)計(jì)算機(jī)并不是大神的最厲害的成就,而且他也并沒(méi)有花太多時(shí)間精力在計(jì)算機(jī)的研究上】。

1955年10月,諾伊曼,被查出患有癌癥。而他幾乎是在他生命的最后時(shí)刻,于臨終的病榻上撰寫(xiě)了關(guān)于人的神經(jīng)系統(tǒng)與計(jì)算機(jī)關(guān)系的講稿。1958年,他的講稿以《計(jì)算機(jī)與人腦》為題出版。

計(jì)算機(jī)與人腦

諾依曼從數(shù)學(xué)的角度,主要是從邏輯和統(tǒng)計(jì)數(shù)學(xué)的角度,討論了神經(jīng)系統(tǒng)的刺激——反應(yīng)和記憶等問(wèn)題,提出神經(jīng)系統(tǒng)具有數(shù)字部分和模擬部分兩方面的特征,探討了神經(jīng)系統(tǒng)的控制及邏輯結(jié)構(gòu)。

4. 馮諾依曼架構(gòu)馮諾依曼的核心是:「存儲(chǔ)程序,順序執(zhí)行」,規(guī)定計(jì)算機(jī)必須具有如下功能:

把需要的程序和數(shù)據(jù)送至計(jì)算機(jī)中;

必須具有長(zhǎng)期記憶程序、數(shù)據(jù)、中間結(jié)果及最終運(yùn)算結(jié)果的能力;

能夠完成各種算術(shù)、邏輯運(yùn)算和數(shù)據(jù)傳送等數(shù)據(jù)加工處理的能力;

能夠根據(jù)需要控制程序走向,并能根據(jù)指令控制機(jī)器的各部件協(xié)調(diào)操作;

能夠按照要求將處理結(jié)果輸出給用戶(hù)

馮諾依曼架構(gòu)

5. 哈佛架構(gòu)馮諾依曼結(jié)構(gòu)和哈佛結(jié)構(gòu)是有區(qū)別的。

馮諾依曼結(jié)構(gòu)是程序存儲(chǔ)區(qū)和數(shù)據(jù)存儲(chǔ)器都是可以放到內(nèi)存中,統(tǒng)一編碼的,而哈弗結(jié)構(gòu)是分開(kāi)編址的。

哈佛架構(gòu)

6. 哪些處理器是哈佛架構(gòu)、馮諾依曼架構(gòu)?「哈佛架構(gòu)」

MCU(單片機(jī))幾乎都是用哈佛結(jié)構(gòu),譬如廣泛使用的51單片機(jī)、典型的STM32單片機(jī)(核心是ARM Cortex-M系列的)都是哈佛結(jié)構(gòu)。

「馮諾依曼架構(gòu)」

PC和服務(wù)器芯片(譬如Intel AMD),ARM Cortex-A系列嵌入式芯片(譬如核心是ARM Cortex-A9的三星exynos-4412,譬如華為的麒麟970等手機(jī)芯片)等都是馮諾依曼結(jié)構(gòu)。這些系統(tǒng)都需要大量?jī)?nèi)存,所以工作內(nèi)存都是DRAM,因?yàn)樗麄兏m合使用馮諾依曼系統(tǒng)。

「混合結(jié)構(gòu)」

實(shí)際上現(xiàn)代的CPU(準(zhǔn)確說(shuō)叫SoC)基本都不是純粹的哈佛結(jié)構(gòu)或馮諾依曼機(jī)構(gòu),而都是混合結(jié)構(gòu)的。

比如三星exynos 4412,使用ARM的Cortex-A9核心。基于exynos 4412開(kāi)發(fā)板上都配備了1024MB的DDR SDRAM,和8GB的EMMC。

正常工作時(shí)所有的程序和數(shù)據(jù)都從EMMC中加載到DDR中,也就是說(shuō)不管你是指令還是數(shù)據(jù),存儲(chǔ)都是在EMMC中,運(yùn)行時(shí)都在DDR中,再通過(guò)cache和寄存器送給CPU去加工處理。這就是典型的馮諾依曼系統(tǒng)。

但是,exynos 4412內(nèi)部仍然有一定容量的64KB irom和64KB iram,這些irom和iram是用于SoC引導(dǎo)和啟動(dòng)的,芯片上電后首先會(huì)執(zhí)行內(nèi)部irom中固化的代碼,其實(shí)執(zhí)行這些代碼時(shí)4412就好像一個(gè)MCU一樣,irom就是他的flash,iram就是他的SRAM,這又是典型的哈佛結(jié)構(gòu)。

這就是混合式結(jié)構(gòu)設(shè)計(jì),而非純粹設(shè)計(jì)。之所以采用混合式設(shè)計(jì)其實(shí)就是為了各取所長(zhǎng)而已。

不管白貓黑貓,解決問(wèn)題就是好貓。

二、計(jì)算機(jī)組成計(jì)算機(jī)系統(tǒng)=硬件系統(tǒng)+軟件系統(tǒng) 硬件是計(jì)算機(jī)系統(tǒng)的物質(zhì)基礎(chǔ),軟件是計(jì)算機(jī)系統(tǒng)的靈魂。硬件和軟件是相輔相成的,不可分割的整體。

計(jì)算機(jī)組成

1)。輸入設(shè)備輸入設(shè)備的任務(wù)是把人們編好的程序和原始數(shù)據(jù)送到計(jì)算機(jī)中去,并且將它們轉(zhuǎn)換成計(jì)算機(jī)內(nèi)部所能識(shí)別和接受的信息方式。常用的有鍵盤(pán)、鼠標(biāo)、掃描儀等。

2)。輸出設(shè)備輸出設(shè)備的任務(wù)是將計(jì)算機(jī)的處理結(jié)果以人或其他設(shè)備所能接受的形式送出計(jì)算機(jī)。常用的有顯示器、打印機(jī)、繪圖儀等。

3)。存儲(chǔ)器、CPU見(jiàn)第三節(jié)

4)。 計(jì)算機(jī)的總線(xiàn)結(jié)構(gòu)將各大基本部件,按某種方式連接起來(lái)就構(gòu)成了計(jì)算機(jī)的硬件系統(tǒng)。

系統(tǒng)總線(xiàn)包含有三種不同功能的總線(xiàn),即數(shù)據(jù)總線(xiàn)DB(Data Bus)、地址總線(xiàn)AB(Address Bus)和控制總線(xiàn)CB(Control Bus)。

數(shù)據(jù)總線(xiàn)DB 用于傳送數(shù)據(jù)信息。數(shù)據(jù)總線(xiàn)的位數(shù)是微型計(jì)算機(jī)的一個(gè)重要指標(biāo),通常與微處理的字長(zhǎng)相一致。例如Intel 8086微處理器字長(zhǎng)16位,其數(shù)據(jù)總線(xiàn)寬度也是16位。

地址總線(xiàn)AB 專(zhuān)門(mén)用來(lái)傳送地址的。地址總線(xiàn)的位數(shù)決定了CPU可直接尋址的內(nèi)存空間大小,比如8位微機(jī)的地址總線(xiàn)為16位,則其最大可尋址空間為216=64KB,16位微型機(jī)的地址總線(xiàn)為20位,其可尋址空間為220=1MB。控制總線(xiàn)CB 用來(lái)傳送控制信號(hào)和時(shí)序信號(hào)。控制信號(hào)中,有的是微處理器送往存儲(chǔ)器和I/O接口電路的,如讀/寫(xiě)信號(hào),片選信號(hào)、中斷響應(yīng)信號(hào)等;也有是其它部件反饋給CPU的,比如:中斷申請(qǐng)信號(hào)、復(fù)位信號(hào)、總線(xiàn)請(qǐng)求信號(hào)、限備就緒信號(hào)等。控制總線(xiàn)的具體情況取決于CPU。

在這里插入圖片描述

三、 CPU工作原理CPU內(nèi)部主要包括運(yùn)算器和控制器。

指令

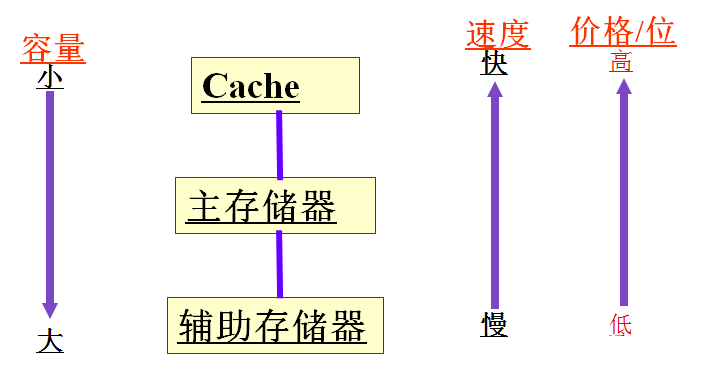

1) 存儲(chǔ)器存儲(chǔ)器是用來(lái)存放程序和數(shù)據(jù)的部件,它是一個(gè)記憶裝置,也是計(jì)算機(jī)能夠?qū)崿F(xiàn)“存儲(chǔ)程序控制”的基礎(chǔ)。

包括:Cache、主存儲(chǔ)器、輔助存儲(chǔ)器。

「高速緩沖存儲(chǔ)器(Cache)」CPU可以直接訪(fǎng)問(wèn),用來(lái)存放當(dāng)前正在執(zhí)行的程序中的活躍部分,以便快速地向CPU提供指令和數(shù)據(jù)。

「主存儲(chǔ)器」可由CPU直接訪(fǎng)問(wèn),用來(lái)存放當(dāng)前正在執(zhí)行的程序和數(shù)據(jù)。

「輔助存儲(chǔ)器」設(shè)置在主機(jī)外部,CPU不能直接訪(fǎng)問(wèn),用來(lái)存放暫時(shí)不參與運(yùn)行的程序和數(shù)據(jù),需要時(shí)再傳送到主存。

存儲(chǔ)器

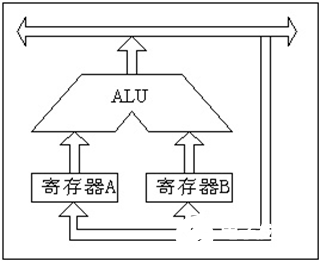

2) 運(yùn)算器運(yùn)算器的核心是算術(shù)邏輯運(yùn)算部件ALU,還包括若干個(gè)寄存器(如累加寄存器、暫存器等)。

ALU可以執(zhí)行算術(shù)運(yùn)算(包括加減乘數(shù)等基本運(yùn)算及其附加運(yùn)算)和邏輯運(yùn)算(包括移位、邏輯測(cè)試或兩個(gè)值比較)。相對(duì)控制單元而言,運(yùn)算器接受控制單元的命令而進(jìn)行動(dòng)作,即運(yùn)算單元所進(jìn)行的全部操作都是由控制單元發(fā)出的控制信號(hào)來(lái)指揮的,所以它是執(zhí)行部件。

運(yùn)算器

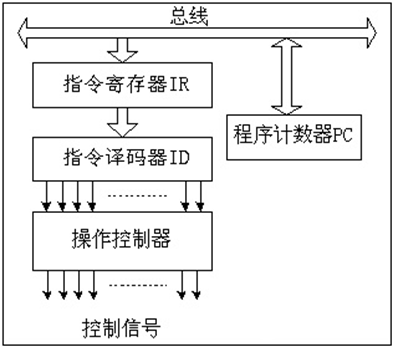

3) 控制器控制單元是整個(gè)CPU的指揮控制中心,由程序計(jì)數(shù)器PC(Program Counter), 指令寄存器IR(Instruction Register)、指令譯碼器ID(Instruction Decoder)和操作控制器OC(Operation Controller)等組成,對(duì)協(xié)調(diào)整個(gè)電腦有序工作極為重要。

它根據(jù)用戶(hù)預(yù)先編好的程序,依次從存儲(chǔ)器中取出各條指令,放在指令寄存器IR中,通過(guò)指令譯碼(分析)確定應(yīng)該進(jìn)行什么操作,然后通過(guò)操作控制器OC,按確定的時(shí)序,向相應(yīng)的部件發(fā)出微操作控制信號(hào)。操作控制器OC中主要包括節(jié)拍脈沖發(fā)生器、控制矩陣、時(shí)鐘脈沖發(fā)生器、復(fù)位電路和啟停電路等控制邏輯。

控制器

4) CPU的運(yùn)行原理總結(jié)控制單元在時(shí)序脈沖的作用下,將指令計(jì)數(shù)器里所指向的指令地址(這個(gè)地址是在內(nèi)存里的)送到地址總線(xiàn)上去,然后CPU將這個(gè)地址里的指令讀到指令寄存器進(jìn)行譯碼。

對(duì)于執(zhí)行指令過(guò)程中所需要用到的數(shù)據(jù),會(huì)將數(shù)據(jù)地址也送到地址總線(xiàn),然后CPU把數(shù)據(jù)讀到CPU的內(nèi)部存儲(chǔ)單元(就是內(nèi)部寄存器)暫存起來(lái),最后命令運(yùn)算單元對(duì)數(shù)據(jù)進(jìn)行處理加工。

周而復(fù)始,一直這樣執(zhí)行下去。

5) 指令執(zhí)行過(guò)程一條指令的執(zhí)行通常包括以下4個(gè)步驟:

指令執(zhí)行過(guò)程

1、取指令:CPU的控制器從內(nèi)存讀取一條指令并放入指令寄存器。2、指令譯碼:指令寄存器中的指令經(jīng)過(guò)譯碼,決定該指令應(yīng)進(jìn)行何種操作(就是指令里的操作碼)、操作數(shù)在哪里(操作數(shù)的地址)。3、 執(zhí)行指令,分兩個(gè)階段“取操作數(shù)”和“進(jìn)行運(yùn)算”。4、 修改指令計(jì)數(shù)器,決定下一條指令的地址。

6) ARM技術(shù)特征ARM的成功,一方面得益于它獨(dú)特的公司運(yùn)作模式,另一方面,當(dāng)然來(lái)自于ARM處理器自身的優(yōu)良性能。作為一種先進(jìn)的RISC處理器,ARM處理器有如下特點(diǎn)。

體積小、低功耗、低成本、高性能。

支持Thumb(16位)/ARM(32位)雙指令集,能很好地兼容8位/16位器件。

大量使用寄存器,指令執(zhí)行速度更快。

大多數(shù)數(shù)據(jù)操作都在寄存器中完成。

尋址方式靈活簡(jiǎn)單,執(zhí)行效率高。

指令長(zhǎng)度固定。此處有必要講解一下RISC微處理器的概念及其與CISC微處理器的區(qū)別。

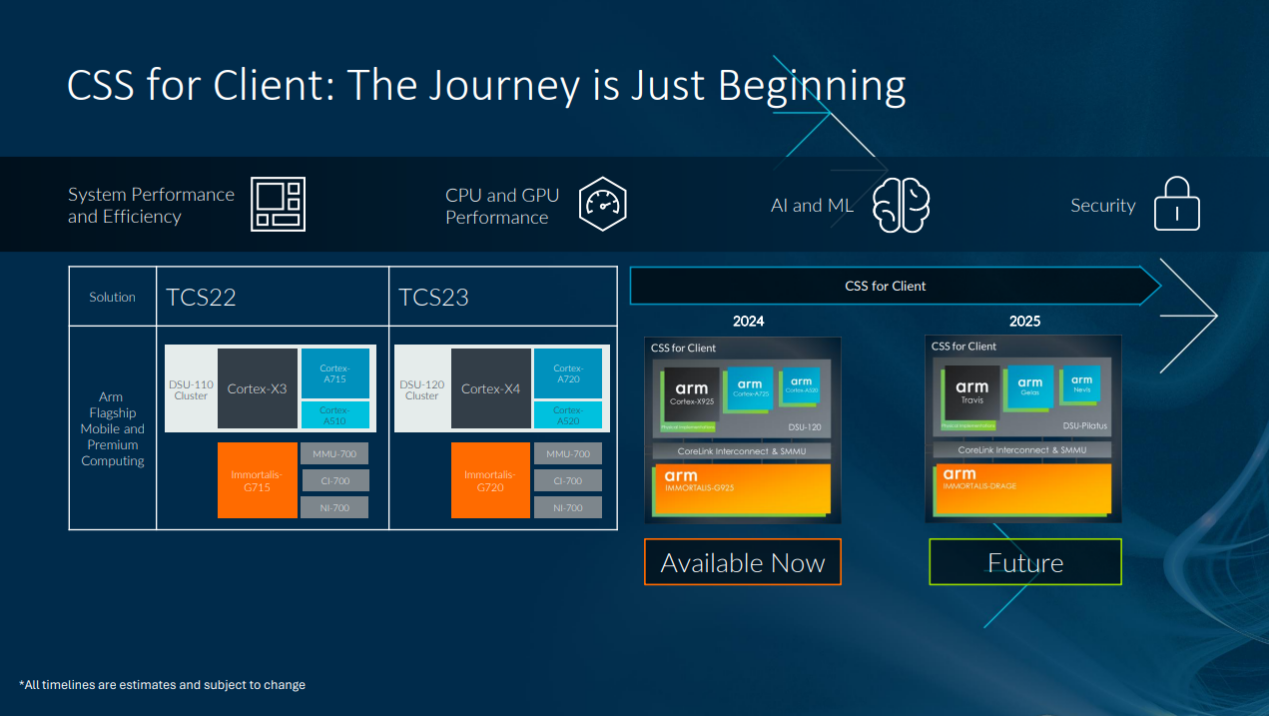

7) ARM體系架構(gòu)的發(fā)展體系架構(gòu)的定義:體系架構(gòu)定義了指令集(ISA)和基于這一體系架構(gòu)下處理器的編程模型。基于同種體系架構(gòu)可以有多種處理器,每個(gè)處理器性能不同,所面向的應(yīng)用不同,每個(gè)處理器的實(shí)現(xiàn)都要遵循這一體系結(jié)構(gòu)。ARM體系架構(gòu)為嵌入系統(tǒng)發(fā)展商提供很高的系統(tǒng)性能,同時(shí)保持優(yōu)異的功耗和效率。

ARM體系架構(gòu)為滿(mǎn)足ARM合作者及設(shè)計(jì)領(lǐng)域的一般需求正穩(wěn)步發(fā)展。目前,ARM體系架構(gòu)共定義了8個(gè)版本,從版本1到版本8,ARM體系的指令集功能不斷擴(kuò)大,不同系列的ARM處理器,性能差別很大,應(yīng)用范圍和對(duì)象也不盡相同,但是,如果是相同的ARM體系架構(gòu),那么基于它們的應(yīng)用軟件是兼容的。

下面我們簡(jiǎn)單介紹下 V7/V8架構(gòu)。

v7架構(gòu)

ARMv7架構(gòu)是在ARMv6架構(gòu)的基礎(chǔ)上誕生的。該架構(gòu)采用了Thumb-2技術(shù),它是在ARM的Thumb代碼壓縮技術(shù)的基礎(chǔ)上發(fā)展起來(lái)的,并且保持了對(duì)現(xiàn)存ARM解決方案的完整的代碼兼容性。Thumb-2技術(shù)比純32位代碼少使用31%的內(nèi)存,減小了系統(tǒng)開(kāi)銷(xiāo),同時(shí)能夠提供比已有的基于Thumb技術(shù)的解決方案高出38%的性能。ARMV7架構(gòu)還采用了NEON技術(shù),將DSP和媒體處理能力提高了近4倍。并支持改良的浮點(diǎn)運(yùn)算,滿(mǎn)足下一代3D圖形、游戲物理應(yīng)用及傳統(tǒng)嵌入式控制應(yīng)用的需求。

v8架構(gòu)

ARMv8架構(gòu)是在32位ARM架構(gòu)上進(jìn)行開(kāi)發(fā)的,將被首先用于對(duì)擴(kuò)展虛擬地址和64位數(shù)據(jù)處理技術(shù)有更高要求的產(chǎn)品領(lǐng)域,如企業(yè)應(yīng)用、高檔消費(fèi)電子產(chǎn)品。ARMv8架構(gòu)包含兩個(gè)執(zhí)行狀態(tài):AArch64和AArch32。AArch64執(zhí)行狀態(tài)針對(duì)64位處理技術(shù),引入了一個(gè)全新指令集A64,可以存取大虛擬地址空間;而AArch32執(zhí)行狀態(tài)將支持現(xiàn)有的ARM指令集。目前的ARMv7架構(gòu)的主要特性都將在ARMv8架構(gòu)中得以保留或進(jìn)一步拓展,如TrustZone技術(shù)、虛擬化技術(shù)及NEON advanced SIMD技術(shù)等。

8) ARM 微處理器架構(gòu)ARM內(nèi)核采用RISC體系架構(gòu)。ARM體系架構(gòu)的主要特征如下。

采用大量的寄存器,它們都可以用于多種用途。

采用Load/Store體系架構(gòu)。

每條指令都條件執(zhí)行。

采用多寄存器的Load/Store指令。

能夠在單時(shí)鐘周期執(zhí)行的單條指令內(nèi)完成一項(xiàng)普通的移位操作和一項(xiàng)普通的ALU操作。

通過(guò)協(xié)處理器指令集來(lái)擴(kuò)展ARM指令集,包括在編程模式中增加了新的寄存器和數(shù)據(jù)類(lèi)型。

如果把Thumb指令集也當(dāng)做ARM體系架構(gòu)的一部分,那么在Thumb體系架構(gòu)中還可以高密度16位壓縮形式表示指令集。

9) ARM指令A(yù)RM指令是RISC(Reduced Instruction Set Computing),即精簡(jiǎn)執(zhí)令運(yùn)算集,RISC把著眼點(diǎn)放在如何使計(jì)算機(jī)的結(jié)構(gòu)更加簡(jiǎn)單和如何使計(jì)算機(jī)的處理速度更加快速上。RISC選取了使用頻率最高的簡(jiǎn)單指令,拋棄復(fù)雜指令,固定指令長(zhǎng)度,減少指令格式和尋址方式,不用或少用微碼控制。這些特點(diǎn)使得RISC非常適合嵌入式處理器。

RISC可以實(shí)現(xiàn)以相對(duì)少的晶體管設(shè)計(jì)出極快的微處理器。通過(guò)研究發(fā)現(xiàn),只有大約20%的指令是最常用的,把處理器能執(zhí)行的指令數(shù)目減少到最低限度,對(duì)它們的執(zhí)行過(guò)行優(yōu)化,就可以極大地提高處理的工作速度。

一般來(lái)說(shuō),RISC處理器比同等的CISC(Complex Instruction Set Computer,復(fù)雜指令集計(jì)算機(jī))處理器要快50%-75%,同時(shí)RISC處理器更容易設(shè)計(jì)和糾錯(cuò)。

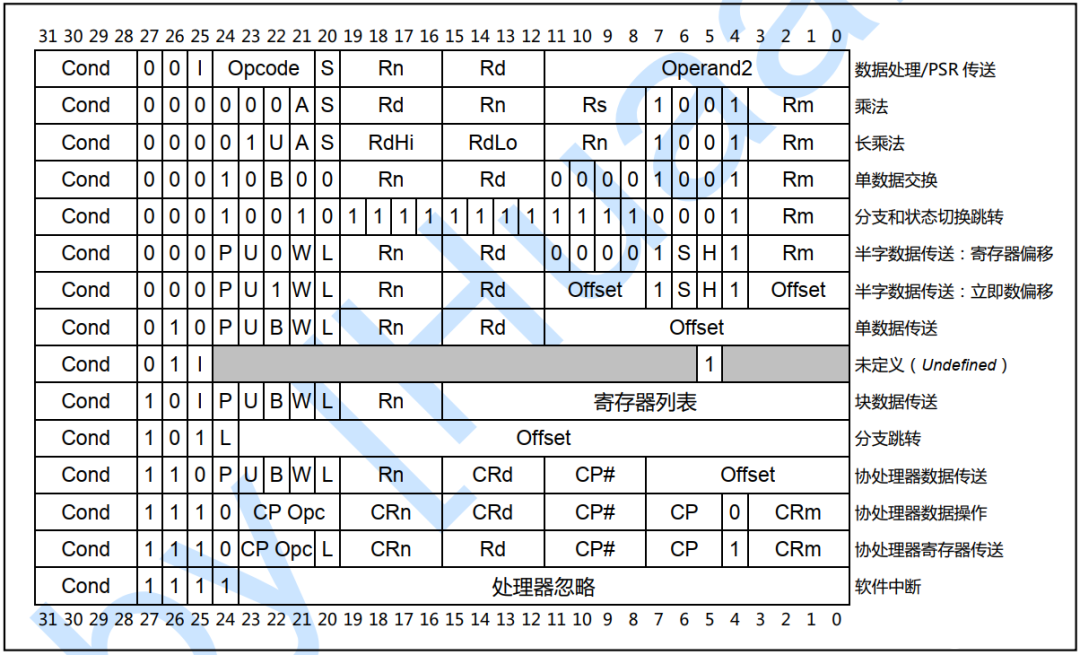

一般指令格式如下:

指令格式

「操作碼:」操作碼就是匯編語(yǔ)言里的mov,add,jmp等符號(hào)碼;

「操作數(shù)地址:」用于說(shuō)明該指令需要的操作數(shù)所在的地方,是在內(nèi)存里還是在CPU的內(nèi)部寄存器里。

實(shí)際上的機(jī)器指令格式遠(yuǎn)比這個(gè)復(fù)雜,下圖是常用的ARM指令格式:

ARM 指令格式

關(guān)于這些機(jī)器指令格式,后面我們會(huì)挑選其中幾個(gè)分析,對(duì)于我們大部分讀者來(lái)說(shuō),沒(méi)有必要花太多精力去研究這些機(jī)器指令,只需要大概了解即可。

關(guān)于CPU我們從宏觀上把握到這個(gè)程度就OK了,后面我們會(huì)逐步進(jìn)入后續(xù)階段的學(xué)習(xí),介紹ARM寄存器模式、異常、尋址、匯編指令,以及C代碼中嵌入的匯編語(yǔ)言的寫(xiě)法。

四、SOCSOC:系統(tǒng)芯片是一個(gè)將計(jì)算機(jī)或其他電子系統(tǒng)集成單一芯片的集成電路。系統(tǒng)芯片可以處理數(shù)字信號(hào)、模擬信號(hào)、混合信號(hào)甚至更高頻率的信號(hào)。

從狹義角度講,它是信息系統(tǒng)核心的芯片集成,是將系統(tǒng)關(guān)鍵部件集成在一塊芯片上; 從廣義角度講, SoC是一個(gè)微小型系統(tǒng),如果說(shuō)中央處理器(CPU)是大腦,那么SoC就是包括大腦、心臟、眼睛和手的系統(tǒng)。

1. ARM base Soc嵌入式系統(tǒng)中常常要使用系統(tǒng)芯片。系統(tǒng)芯片的集成規(guī)模很大,一般達(dá)到幾百萬(wàn)門(mén)到幾千萬(wàn)門(mén)。SOC相對(duì)比較靈活,它可以將arm架構(gòu)的處理器與一些專(zhuān)用的外圍芯片集成到一起,組成一個(gè)系統(tǒng)。

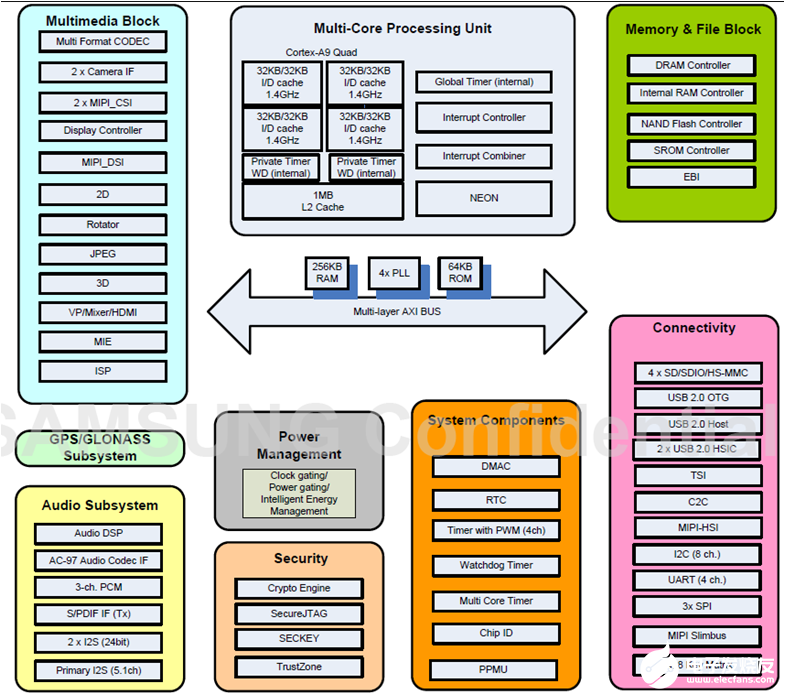

下圖是一個(gè)典型的基于ARM架構(gòu)的SOC架構(gòu)圖。

ARM base Soc

一個(gè)典型的基于ARM的Soc架構(gòu)通常包含以下幾個(gè)主要部件:

ARM Processor core 處理器核

Clocks and Reset Controller 時(shí)鐘和復(fù)位電路

Interrupt Controller 中斷控制器

ARM Propherals 外部設(shè)備

GPIO

DMA Port

External Memory Interface 外部?jī)?nèi)存接口

On chip RAM 偏上RAM

AHB、APB總線(xiàn)

其實(shí)現(xiàn)有的ARM處理器如Hisi-3507、exynos-4412等處理器都是一個(gè)SOC系統(tǒng),尤其是應(yīng)用處理器它集成了許多外圍的器件,為執(zhí)行更復(fù)雜的任務(wù)、更復(fù)雜的應(yīng)用提供了強(qiáng)大的支持。

該架構(gòu)是我們理解匯編指令和編寫(xiě)裸機(jī)程序的基石。

當(dāng)我們拿到一個(gè)新的SOC的datasheet,首先就要根據(jù)這個(gè)架構(gòu),來(lái)查看SOC的「RAM空間、時(shí)鐘頻率、包括哪些外部設(shè)備的控制器,各個(gè)外設(shè)控制器的操作原理,各個(gè)外設(shè)對(duì)GPIO的引腳復(fù)用情況、各個(gè)控制器的SFR地址、中斷控制器是如何管理眾多中斷源的等等」。

2. 三星 Exynos 44122012年初,三星正式推出了自家的首款四核移動(dòng)處理器Exynos4412。

下面三星的exynos 4412的SOC。

Exynos 4412 SCP結(jié)構(gòu)框圖

如上圖所示,exynos 4412主要包括以下模塊:

4(quad)個(gè)Cortex-A9處理器

1MB的 L2 Cache

Interrupt Controller 中斷控制器,管理所有的中斷源

Interrupt Combiner 中斷控制器,管理soc內(nèi)的一些中斷源

NEON ARM 架構(gòu)處理器擴(kuò)展結(jié)構(gòu),旨在通過(guò)加速多媒體(video/audio)編解碼,用戶(hù)界面,2D/3D圖形及游戲來(lái)提高人對(duì)多媒體的體驗(yàn)

DRAM、Internal RAM、NAND Flash、SROM Controller 各種存儲(chǔ)設(shè)備的控制器

SDIO、USB、I2C、UART、SPI等總線(xiàn)

RTC、Watchdog Timer

Audio Subsystem 聲音子系統(tǒng)

IIS(Integrate Interface of Sound)接口 ,集成語(yǔ)音接口

Power Management電源管理

Multimedia Block 多媒體模塊

這款新Exynos四核處理器,擁有32nm HKMG(高K金屬柵極技術(shù))制程,支持雙通道LPDDR21066。三星公司已將這顆圖形處理器主頻由此前的266MHz提升至400MHz,新聞稿指出其會(huì)比現(xiàn)有的雙核機(jī)型整體性能提升60%,圖像處理能力提升50%。

三星智能手機(jī)Galaxy S III手機(jī)就采用了Exynos4412處理器。

學(xué)習(xí)ARM就必須深刻了解soc架構(gòu),官方提供的datasheet是我們學(xué)習(xí)ARM、編寫(xiě)驅(qū)動(dòng)程序的基石,該手冊(cè)內(nèi)容比較多,我們并不需要每一章都掌握,用到哪個(gè)地方,我們就去學(xué)習(xí)即可。責(zé)任編輯:haq

-

ARM

+關(guān)注

關(guān)注

134文章

9312瀏覽量

375168 -

cpu

+關(guān)注

關(guān)注

68文章

11040瀏覽量

216044 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7632瀏覽量

90225

發(fā)布評(píng)論請(qǐng)先 登錄

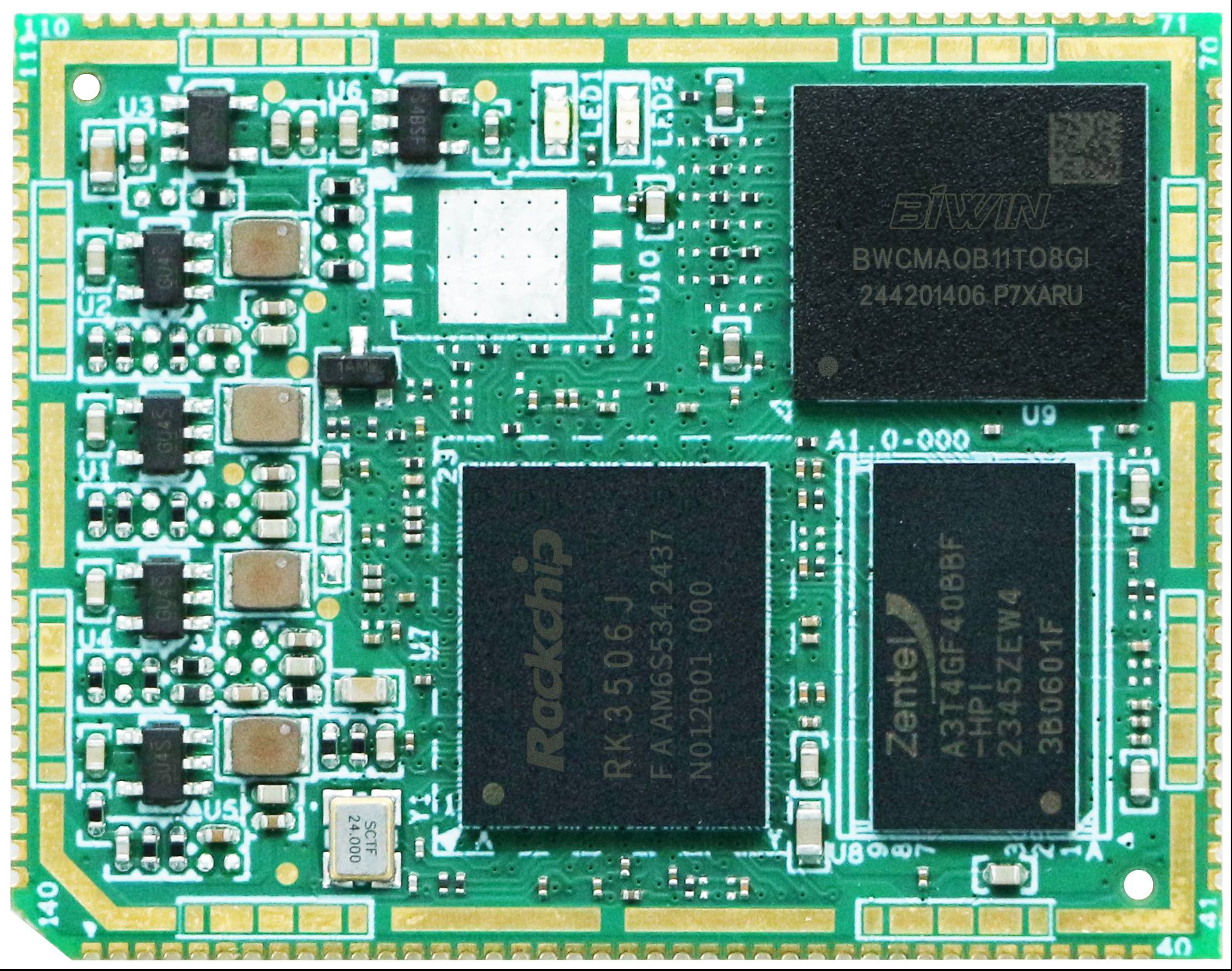

瑞芯微RK3506(3核ARM+Cortex-A7 + ARM Cortex-M0)工業(yè)核心板選型資料

從零開(kāi)始學(xué)電源

Arm解讀Armv9 CPU為何是打造高性能、高能效移動(dòng)計(jì)算的關(guān)鍵

詳解Arm Cortex-A320 CPU的特性

從CPU到GPU:渲染技術(shù)的演進(jìn)和趨勢(shì)

用MCUXPresso for VS Code插件 從0開(kāi)始打造HelloWorld

英偉達(dá)進(jìn)軍ARM架構(gòu)CPU市場(chǎng),預(yù)計(jì)2025年推出新產(chǎn)品線(xiàn)

gd32vf103 timer內(nèi)部計(jì)數(shù)器是自增的,位寬64位,溢出后是從0開(kāi)始嗎?

Arm CPU如何推動(dòng)AI創(chuàng)新

ARM處理器和CPU有什么區(qū)別

從STM32到基于Arm的MSPM0的遷移指南

從遷移到基于Arm STM32的MSPMO指南

將軟件從8位(字節(jié))可尋址CPU遷移至C28x CPU

從Renesas RL78到基于Arm的MSPM0的遷移指南

從AI手機(jī)到AI PC,Arm拿什么打造AI盛宴?

從0開(kāi)始學(xué)ARM-CPU原理

從0開(kāi)始學(xué)ARM-CPU原理

評(píng)論