很多情況下,拍攝的視頻會(huì)有不盡人意的地方,這就需要對(duì)視頻進(jìn)行視頻處理(即幀圖像處理)以達(dá)到所期望的效果。視頻處理是一個(gè)龐大繁瑣又耗時(shí)的工程,尋常視頻處理都是在PC機(jī)上采用CPU+GPU的異構(gòu)計(jì)算來(lái)進(jìn)行;FPGA的出現(xiàn)及其高效的并行運(yùn)算性能,使得CPU+FPGA的異構(gòu)計(jì)算更加適合進(jìn)行高強(qiáng)度的批處理運(yùn)算,zynq系列兼具處理系統(tǒng)和可編程邏輯的SoC片上系統(tǒng)也使得使用FPGA進(jìn)行視頻處理這類運(yùn)算需求量大的工程時(shí)更加得心應(yīng)手。

進(jìn)行幀圖像處理設(shè)計(jì)隨著客戶需求的提高變得越來(lái)越復(fù)雜,復(fù)雜的設(shè)計(jì)變得越來(lái)越難以調(diào)試:在何處設(shè)置探針,重復(fù)進(jìn)行編譯,放置和布線,查看,重置探針,一遍又一遍。調(diào)試中重復(fù)過(guò)程花費(fèi)時(shí)間過(guò)多,很少有時(shí)間調(diào)試根本原因。

虹科FPGA調(diào)試工具--VSTAR

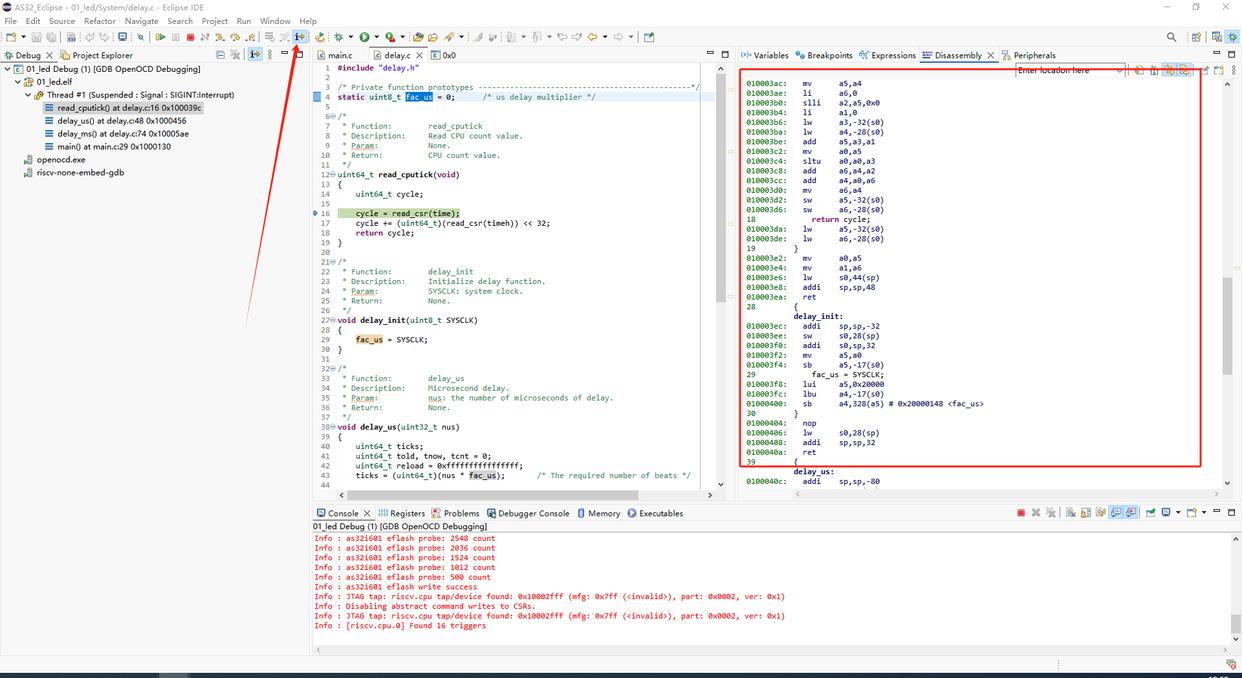

此處我們展示虹科FPGA調(diào)試工具在視頻處理設(shè)計(jì)中進(jìn)行調(diào)試并大幅縮短調(diào)試周期的案例。 我們對(duì)視頻的幀圖像處理采用復(fù)雜程度中等的圖像旋轉(zhuǎn)算法,期望達(dá)到視頻某片段旋轉(zhuǎn)縮小至消失并鏈接下一視頻片段的效果。 圖像旋轉(zhuǎn)算法映射到具有300 MHz AXI流和200 MHz AXI總線的Xilinx Kintex-7 FPGA K705開(kāi)發(fā)板上。

視頻處理流程框圖

在設(shè)計(jì)中向圖像旋轉(zhuǎn)算法人為的注入會(huì)造成工程出現(xiàn)預(yù)期之外的邏輯錯(cuò)誤,但可以正確通過(guò)編譯、布局布線、綜合和仿真。在VSTAR GUI 中打開(kāi)該設(shè)計(jì),注入VSTAR的驗(yàn)證IP并選定clk時(shí)間信號(hào)。

根據(jù)設(shè)計(jì)以及調(diào)試需要,選擇了三組總線探針進(jìn)行監(jiān)測(cè),VSTAR會(huì)根據(jù)選定的探針自動(dòng)生成設(shè)計(jì)規(guī)則,當(dāng)然如果發(fā)現(xiàn)自動(dòng)設(shè)計(jì)的規(guī)則不太合適也可以自己手動(dòng)進(jìn)行設(shè)計(jì)規(guī)則的設(shè)定。

下載好bit流文件并運(yùn)行后,VSTAR開(kāi)始自動(dòng)檢測(cè)所選探針的錯(cuò)誤情況,如果監(jiān)測(cè)到設(shè)計(jì)規(guī)則之外的,并顯示故障,通過(guò)GTKWave上的VCD向用戶顯示。

VSTAR用于圖像旋轉(zhuǎn)器有效信號(hào)的探針設(shè)置

VSTAR為圖像旋轉(zhuǎn)器的有效信號(hào)自動(dòng)生成的規(guī)則之一

由下圖監(jiān)測(cè)結(jié)果可以看出,正常運(yùn)轉(zhuǎn)時(shí),所監(jiān)測(cè)的探針信號(hào)符合設(shè)計(jì)規(guī)則,但當(dāng)達(dá)到人為設(shè)計(jì)的錯(cuò)誤觸發(fā)條件以后,圖像旋轉(zhuǎn)器出現(xiàn)信號(hào)跳轉(zhuǎn)錯(cuò)誤,違背了設(shè)計(jì)規(guī)則,由于設(shè)定錯(cuò)誤緩存區(qū)為1次,所以此次出現(xiàn)錯(cuò)誤后會(huì)直接結(jié)束監(jiān)測(cè),并展示VSTAR IP Status狀態(tài)窗口,顯示具體錯(cuò)誤描述。

可根據(jù)出現(xiàn)錯(cuò)誤的信號(hào)以及錯(cuò)誤發(fā)生的時(shí)間去專向分析產(chǎn)生錯(cuò)誤的原因,從而大幅縮短調(diào)試周期。

監(jiān)測(cè)結(jié)果

責(zé)任編輯:xj

原文標(biāo)題:虹科VSTAR縮短FPGA視頻處理調(diào)試周期

文章出處:【微信公眾號(hào):FPGA技術(shù)支持】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

視頻處理

+關(guān)注

關(guān)注

2文章

99瀏覽量

19128 -

FGPA

+關(guān)注

關(guān)注

1文章

26瀏覽量

16261 -

虹科電子

+關(guān)注

關(guān)注

0文章

660瀏覽量

14784

原文標(biāo)題:虹科VSTAR縮短FPGA視頻處理調(diào)試周期

文章出處:【微信號(hào):HK-FPGA_Dep,微信公眾號(hào):FPGA技術(shù)支持】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

調(diào)試工具:Eclipse調(diào)試工具欄與窗口的深入分析

是否可以通過(guò) AIROC 藍(lán)牙測(cè)試和調(diào)試工具 v1.4 或 HCI 命令輸出突發(fā)波形?

請(qǐng)問(wèn)AIROC? Bluetooth?測(cè)試和調(diào)試工具_1.4.2是否支持CYW9RPIWIFIBT-EVK ?

RT-Trace調(diào)試工具正式發(fā)布!

基于STM32 的聯(lián)合調(diào)試偵聽(tīng)設(shè)備解決方案(原理圖、PCB源文件、調(diào)試工具、視頻)

重磅預(yù)售!RT-Trace調(diào)試工具

Segger RTT調(diào)試工具的使用方法

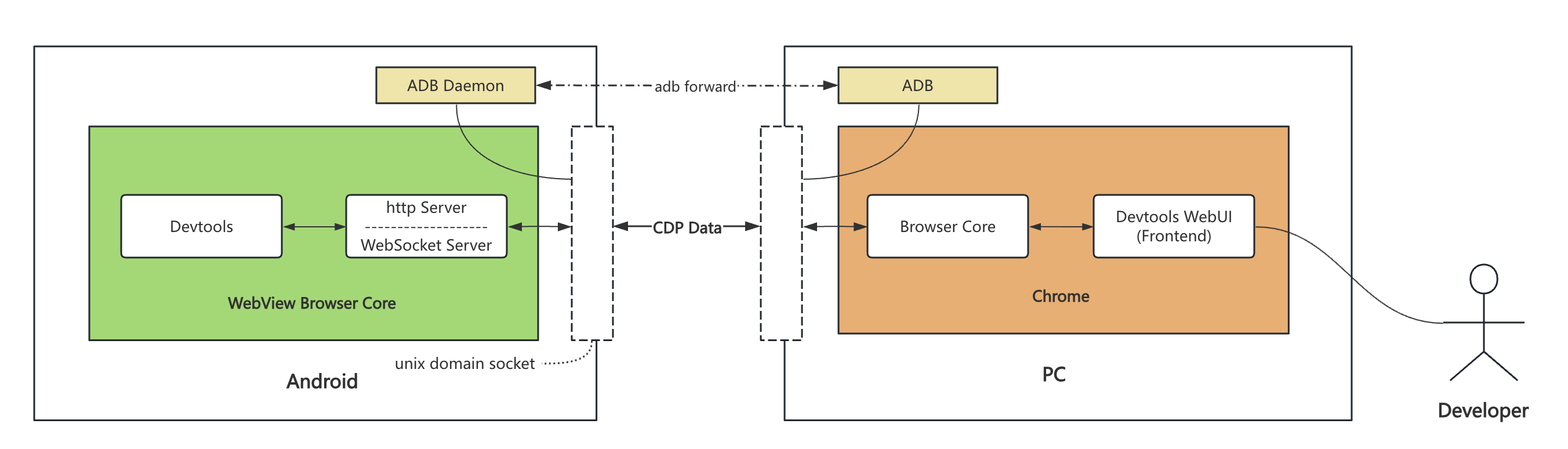

揭秘Chrome DevTools:從原理到自定義調(diào)試工具

虹科直播回放 | IO-Link技術(shù)概述與虹科IO-Link OEM

芯科科技Z-Wave設(shè)備測(cè)試工具介紹

Web端TCP/UDP測(cè)試工具!小白必學(xué)~

更強(qiáng)的無(wú)線(雙)串口數(shù)據(jù)記錄 調(diào)試工具

虹科FPGA調(diào)試工具:VSTAR

虹科FPGA調(diào)試工具:VSTAR

評(píng)論