單片機的基準電壓一般為3.3V,如果外部信號超過了AD測量范圍,可以采用電阻分壓的方法,但是要注意阻抗匹配問題。比如,SMT32的模數輸入阻抗約為10K,如果外接的分壓電阻無法遠小于該阻值,則會因為信號源輸出阻抗較大,AD的輸入阻抗較小,從而輸入阻抗對信號源信號的電壓造成分壓,最終導致電壓讀取誤差較大。

因此對于使用單片機讀取外部信號電壓,外接分壓電阻必須選用較小的電阻,或者在對功耗有要求的情況下,可選用大阻值的電壓分壓后,使用電壓跟隨器進行阻抗匹配(電壓跟隨器輸入阻抗可達到幾兆歐姆,輸出阻抗為幾歐姆甚至更小)。如果信號源的輸出阻抗較大,可采用電壓跟隨器匹配后再接電阻分壓。

對于外置的ADC芯片,在選型時,要留意其類型(SAR型、開關電容型、FLASH型、雙積分型、Sigma-Delta型),不同類型的ADC芯片輸入阻抗不同——

1、SAR型:這種ADC內阻都很大,一般500K以上。即使阻抗小的ADC,阻抗也是固定的。所以即使只要被測源內阻穩定,只是相當于電阻分壓,可以被校正;

2、開關電容型:如TLC2543之類,其要求很低的輸入阻抗用于對內部采樣電容快速充電。這時最好有低阻源,否則會引起誤差。實在不行,可以外部并聯一很大的電容,每次被取樣后,大電容的電壓下降不多。因此并聯外部大電容后,開關電容輸入可以等效為一個純阻性阻抗,可以被校正;

3、FLASH型(直接比較型):大多高速ADC都是直接比較型,也稱閃速型(FLASH),一般都是低阻抗的。要求低阻源。對外表現純阻性,可以和運放直接連接;

4、雙積分型:這種類型大多輸入阻抗極高,幾乎不用考慮阻抗問題;

5、Sigma-Delta型:這是目前精度最高的ADC類型,需要重點注意如下問題:

測量范圍問題:SigmaDelta型ADC屬于開關電容型輸入,必須有低阻源。所以為了簡化外部設計,內部大多集成有緩沖器。緩沖器打開,則對外呈現高阻,使用方便。但要注意了,緩沖器實際是個運放。那么必然有上下軌的限制。大多數緩沖器都是下軌50mV,上軌AVCC-1.5V。在這種應用中,共莫輸入范圍大大的縮小,而且不能到測0V。一定要特別小心!一般用在電橋測量中,因為共模范圍都在1/2VCC附近。不必過分擔心緩沖器的零票,通過內部校零寄存器很容易校正的;

輸入端有RC濾波器的問題:SigmaDelta型ADC屬于開關電容型輸入,在低阻源上工作良好。但有時候為了抑制共模或抑制乃奎斯特頻率外的信號,需要在輸入端加RC濾波器,一般DATASHEET上會給一張最大允許輸入阻抗和C和Gain的關系表。這時很奇怪的一個特性是,C越大,則最大輸入阻抗必須隨之減小!剛開始可能很多人不解,其實只要想一下電容充電特性久很容易明白的。還有一個折衷的辦法是,把C取很大,遠大于幾百萬倍的采樣電容Cs(一般4~20PF),則輸入等效純電阻,分壓誤差可以用GainOffset寄存器校正。

運放千萬不能和SigmaDelta型ADC直連:前面說過,開關電容輸入電路電路周期用采樣電容從輸入端采樣,每次和運放并聯的時候,會呈現低阻,和運放輸出阻抗分壓,造成電壓下降,負反饋立刻開始校正,但運放壓擺率(SlewRate)有限,不能立刻響應。于是造成瞬間電壓跌落,取樣接近完畢時,相當于高阻,運放輸出電壓上升,但壓擺率使運放來不及校正,結果是過沖。而這時正是最關鍵的采樣結束時刻。所以,運放和SD型ADC連接,必須通過一個電阻和電容連接(接成低通)。而RC的關系又必須服從datasheet所述規則。

差分輸入和雙極性的問題:SD型ADC都可以差分輸入,都支持雙極性輸入。但這里的雙極性并不是指可以測負壓,而是Vi+ Vi-兩腳之間的電壓。假設Vi-接AGND,那么負壓測量范圍不會超過-0.3V。正確的接法是Vi+ Vi- 共模都在-0.3~VCC之間差分輸入。一個典型的例子是電橋。另一個例子是Vi-接Vref,Vi+對Vi-的電壓允許雙極性輸入

責任編輯:lq

-

單片機

+關注

關注

6063文章

44928瀏覽量

647143 -

adc

+關注

關注

99文章

6641瀏覽量

548311 -

電壓

+關注

關注

45文章

5698瀏覽量

117314

原文標題:關于使用單片機讀取外部電壓ADC阻抗匹配的問題

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

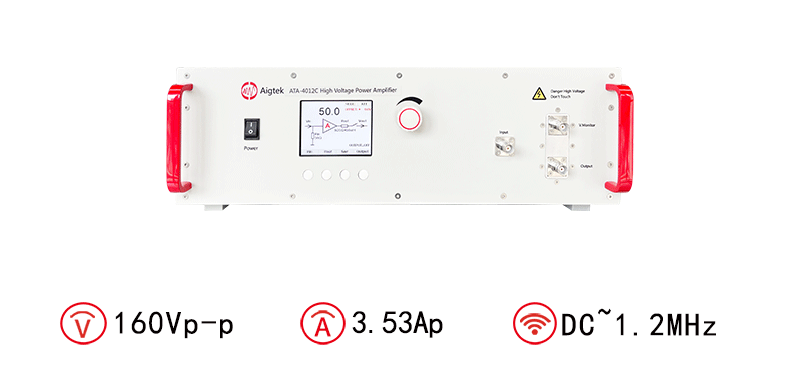

Aigtek:功率放大器如何進行阻抗匹配

如何用單片ADC和DAC去匹配改善電路呢?

利用兩個元件實現 L 型網絡阻抗匹配

在阻抗匹配中50歐姆好像是一個很特殊的值,為什么呢?

OPA847與OPA861之間沒有阻抗匹配,實際做成電路會有問題嗎?

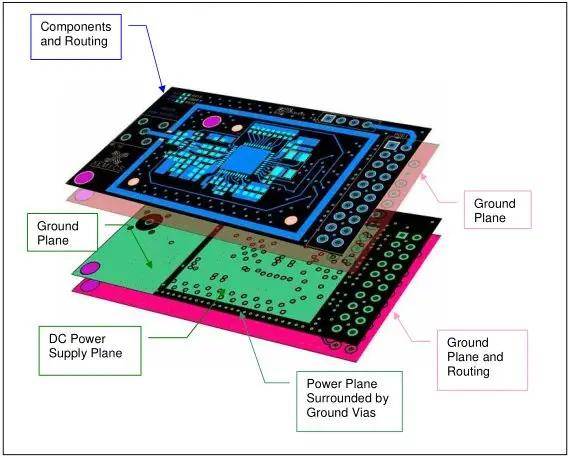

PCB阻抗匹配過孔的多個因素你知道哪些?

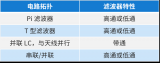

電路的阻抗如何匹配

示波器的幾種模式有什么區別以及阻抗匹配的顯示問題?

阻抗匹配有煩惱?來嘮一嘮~

關于使用單片機讀取外部電壓ADC阻抗匹配的問題

關于使用單片機讀取外部電壓ADC阻抗匹配的問題

評論