原理圖上看似輕描淡寫,PCB設(shè)計(jì)加班到半夜。隨著信號(hào)速率越來越高,原理圖的內(nèi)容在PCB設(shè)計(jì)上去實(shí)現(xiàn)變得越來越難,圖紙上任意的一根理想連線或者器件到了PCB工程師這里可能也無從下手。不信?那就接著往下看唄!

隨著速率越來越高,原理圖上的一根連接線在PCB設(shè)計(jì)上就包括了阻抗匹配,長(zhǎng)度約束,加工偏差,板材選型,等長(zhǎng)設(shè)計(jì),過孔設(shè)計(jì)等內(nèi)容。那么廣大硬件工程師可能會(huì)不服氣了:那就不說線,說下元器件,這一塊是我們的強(qiáng)項(xiàng)了吧!我們?cè)谄骷x型上也花了很多時(shí)間,而且也要很熟悉硬件原理的,然后你們?cè)赑CB上把封裝建出來然后放到PCB板就可以了嘛。乍一聽,好像硬件工程師們扳回一局了,但是高速先生依然要和你們“爭(zhēng)執(zhí)”下去,我們要說的是,即使是一個(gè)簡(jiǎn)單的電容,其實(shí)在PCB設(shè)計(jì)也是很有學(xué)問的哦,你們確定了解嗎?

今天我們來講一下高速串行信號(hào)中非常常見的AC耦合電容。對(duì)!就是下面原理圖里面的這個(gè)玩意。我們今天就來研究一下它對(duì)高速信號(hào)的影響。

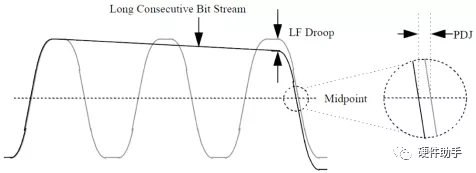

作為一個(gè)電容,可能更多的粉絲會(huì)在電源網(wǎng)絡(luò)中見到過它們。一般來說,電容用在電源網(wǎng)絡(luò)中起到去耦的作用,也就是抑制高頻噪聲的作用。一般來說,我們加入了不同容值的電容,就能夠起到降低某些頻段的PDN阻抗的作用。如下所示,我們加入了一個(gè)在高速鏈路中常有的0.1uF電容,也能夠壓低10M到25MHz頻段的阻抗。為什么是這個(gè)頻段,為什么不能壓掉全頻段的阻抗,這個(gè)高速先生也提過很多次了,今天它不是主角,就不再重復(fù)了。

那么如果同樣的電容放在了高速串行鏈路中后,它對(duì)高速信號(hào)的性能有什么影響呢?為了公平起見,我們還是從原理上和PCB設(shè)計(jì)這兩點(diǎn)去分析哈。

首先從原理上而言,當(dāng)然大家都知道AC耦合電容是用于隔直流,也就是在共模信號(hào)隔掉。從這一點(diǎn)來看,貌似就是一個(gè)很簡(jiǎn)單的原理。但是我們需要知道,電容本身其實(shí)就不是理想的東西,即使它不焊接到PCB上面去,它也是由下面的等效參數(shù)來組成一個(gè)電容,我們把這些參數(shù)叫做電容的寄生參數(shù)。

所以從仿真中就能看到,一段若干長(zhǎng)度的傳輸線加上一個(gè)0402的電容的情況下,電容本身帶入的寄生參數(shù)會(huì)增加一定的損耗。

其實(shí)這個(gè)時(shí)候大家就會(huì)驚訝的發(fā)現(xiàn),同樣的0.1uF電容,如果采用不同的封裝大小時(shí),結(jié)果肯定會(huì)有所不同。

因?yàn)榉庋b越大的電容,它本身的寄生參數(shù)也就越大,因此寄生電感帶來的損耗會(huì)更大。所以單從這個(gè)器件選型的角度看,選擇封裝越小的電容影響也是越小的。

當(dāng)然從上面的內(nèi)容看,從0201到0603的電容選型,仿佛覺得對(duì)損耗的影響也不是很大嘛,再說如果選擇0201的話,其實(shí)基本就沒有影響了唄。恩!這個(gè)觀點(diǎn)高速先生其實(shí)勉強(qiáng)算同意吧,那么我們?cè)賮砜纯慈绻堰@個(gè)電容加到PCB板上之后會(huì)怎么樣呢?

高速先生大概做了一個(gè)3D的模型,可以用來分析下一個(gè)0402的電容放在PCB焊盤上到底對(duì)信號(hào)質(zhì)量有什么影響。

這個(gè)時(shí)候你們就會(huì)發(fā)現(xiàn),影響到信號(hào)性能的因素就不僅僅是電容本身的寄生參數(shù)了,反而是變成了如何去優(yōu)化電容體+焊盤的阻抗了。阻抗如果不匹配的話,它對(duì)回波損耗和插入損耗的因素是非常大的。有多大呢?高速先生列出我們仿真的數(shù)據(jù)如下,一個(gè)未經(jīng)過仿真優(yōu)化的電容結(jié)構(gòu)帶來的插入損耗和回波損耗的結(jié)果如下:

這個(gè)時(shí)候我們?cè)賮韺?duì)比下理想的電容和放到PCB上未優(yōu)化的電容對(duì)于損耗的對(duì)比。

這個(gè)時(shí)候你們就能明顯看到差別了吧。這其實(shí)也說明了仿真對(duì)電容優(yōu)化的重要性,電容絕不只是擺到PCB焊盤上面就OK了哈。

當(dāng)然時(shí)間關(guān)系,其實(shí)還有很多關(guān)于電容在PCB上要注意的點(diǎn)來不及說哈,例如不同封裝大小的電容的優(yōu)化方向,電容在高速鏈路中不同位置的區(qū)別等等。

編輯:hfy

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4781瀏覽量

89209 -

高速信號(hào)

+關(guān)注

關(guān)注

1文章

240瀏覽量

17988 -

耦合電容

+關(guān)注

關(guān)注

2文章

155瀏覽量

20213

發(fā)布評(píng)論請(qǐng)先 登錄

AC耦合電容優(yōu)化(上)

AC耦合電容優(yōu)化(下)

PCB設(shè)計(jì)之電容

AC耦合電容的影響,你真的知道嗎?

如何正確理解AC耦合電容

AC耦合電容的選取

高速PCB設(shè)計(jì)電容的應(yīng)用

完成閉環(huán)設(shè)計(jì),基于仿真軟件的AC耦合電容阻抗優(yōu)化

ViaExpert仿真AC耦合電容阻抗優(yōu)化設(shè)計(jì)方案解析

PCB設(shè)計(jì):AC耦合電容的影響

PCB設(shè)計(jì):AC耦合電容的影響

評(píng)論