隨著速率的不斷提高,信號能夠在鏈路中傳輸的難度越來越大,信號質量會不斷下降,我們把高速信號在傳輸中遇到各種問題統稱為信號完整性問題。通常我們認為信號完整性問題主要是從時域上去衡量,通過對波形質量的判斷,我們把信號完整性問題分為以下幾類:反射,串擾,振鈴,地彈。另一方面我們在高速鏈路的表征上,人們又習慣使用S參數的形式去衡量一個通道的優劣,包括了回波損耗,插入損耗,串擾等指標。那么頻域上的各種損耗的表征和比較直觀的時域波形或眼圖之間有什么關聯呢?用時域的波形來判斷信號質量的確很清晰,然而波形卻不容易給我們以有效的優化手段。因此本文著重介紹如何使用頻域的S參數來分析問題,看看從S參數角度去看信號完整性問題,能否得到關于鏈路通道更多的信息。

從時域推導S參數損耗

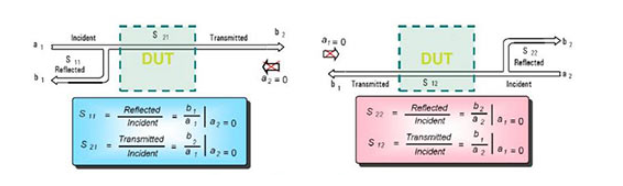

圖1是對一個兩端口的S參數的表征過程,通過測量入射波形和反射波,從而計算出回波損耗S11和插入損耗S21,然后用dB值進行表征。

圖1 S參數的表征

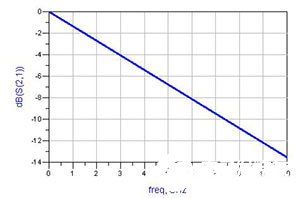

因此當我們看到一個鏈路的損耗如圖2時,其實我們可以用時域的方式去推導它。

圖2 鏈路損耗曲線

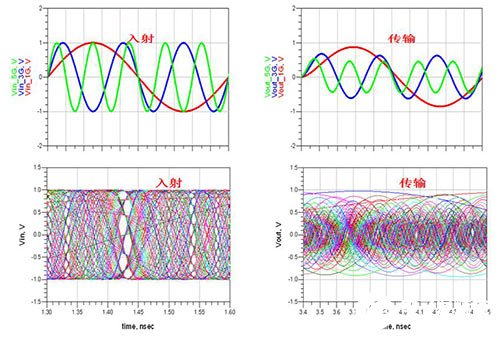

我們知道損耗曲線就是通過發送不同頻率的正弦波,然后去計算反射波、傳輸波與入射波的比值得到的,假設如圖3所示分別發送1GHz、3GHz、5GHz的正弦波,幅度為峰峰值2V,那么會得到傳輸前后的波形如下:

圖3 正弦波的入射與傳輸波形

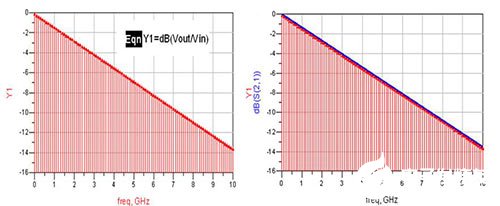

那么當時域有很多不同頻率的正弦波時,就能得到很多傳輸后的波形,同時從圖3也可以看到,不同頻率的正弦波傳輸后的幅度是不相同的,而且頻率越高的正弦波幅度越小。那么按照圖1 的損耗計算公式,如果有很多個傳輸波形比上入射波形,就會得到上述圖2的頻域損耗波形了,如圖4所示,分別為幅度和dB的表征。

圖4 從時域推導頻域損耗曲線

損耗和阻抗

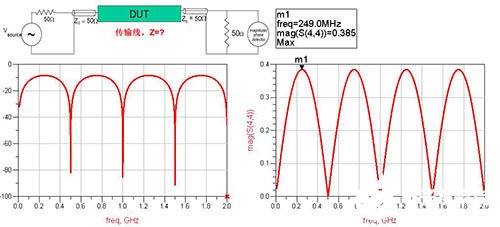

我們知道阻抗不匹配是影響信號完整性的主要原因之一,它會造成波形的過沖,反射,振鈴問題的出現,如果我們僅僅觀察波形的話,似乎很難知道鏈路的阻抗到底是多少,但是從頻域S參數的回波損耗去看卻可以很方便的估算出鏈路的阻抗。就好像圖5所示一樣,我們通過仿真或者測試的手段得到了鏈路的回波損耗曲線(分別用dB和幅度表征)后,那我們怎么能夠推導出鏈路傳輸線的阻抗呢?

圖5 鏈路的回波損耗推導阻抗

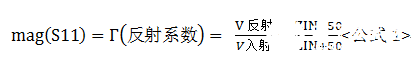

首先關于輸入阻抗ZIN有如下的公式1:

然后對于ZIN的最大值反映在圖5的回波損耗曲線上就能看到最差的結果,如圖5中m1所示,在249MHz處有回損的最大值0.385。

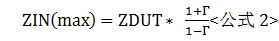

于是又有下面的公式2:

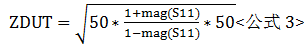

因此結合以上兩個公式就能得到傳輸線阻抗ZDUT的公式3:

因此把回波損耗中mag(S11)=0.385代入公式就得到了傳輸線阻抗ZDUT=75歐姆

損耗與波形(眼圖)

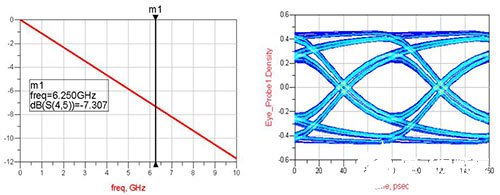

對于硬件工程師或者測試工程師而言,最直觀的判斷信號質量好壞的標準還是通過時域的信號質量,也就是波形或者眼圖。無論是像DDR這種并行信號的波形或者像高速串行信號的眼圖結果,它們的好壞可以很容易通過相關的電平標準和眼圖模板衡量出來。但是如果得到了一個惡劣的時域結果,可能就不是所有人都知道鏈路哪里需要優化和怎樣去優化。時域分析在這個時候就暴露了它的不足,不好的時域波形(眼圖)能夠體現的鏈路的設計問題其實不多,這也導致了很多缺少信號完整性或者高速理論的同行遇到一個較差的時域結果常常無從下手,很難去對PCB鏈路進行優化。如上文所說,S參數的確可以反映出更多PCB鏈路的特點和信息,通過對S參數的查看和探究,經常可以得到更多關于PCB鏈路優化的方向和信息,我們就以下面這個PCB設計仿真比較常見的例子進行說明。如圖6所示,我們仿真一個12.5Gbps的高速信號通道,如果該通道傳輸線的阻抗控制得很好(差分100歐姆),線長在10inch,我們加上收發芯片的模型進行眼圖仿真,就能得到一個比較好的眼圖結果,通過相關的眼圖模板進行衡量,無論是眼高還是眼寬都有很大的裕量,從S參數上看,可以看到此時的損耗在6.25GHz基頻處為7.3dB,整個損耗曲線隨著頻率的升高線性下降,是比較理想的無源參數結果。

圖6 比較理想的損耗和眼圖結果

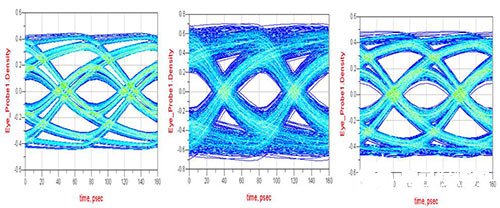

然而如果同樣的網絡,換一個PCB設計工程師進行設計后,在PCB鏈路處理得不夠好的情況下,我們可以得到像圖7這些比較差的眼圖結果,眼高眼寬裕量都是比較小,當然我們知道這樣的設計肯定導致了比較嚴重的信號完整性問題,產品的質量和穩定性也是不好的。

圖7 不理想的眼圖結果

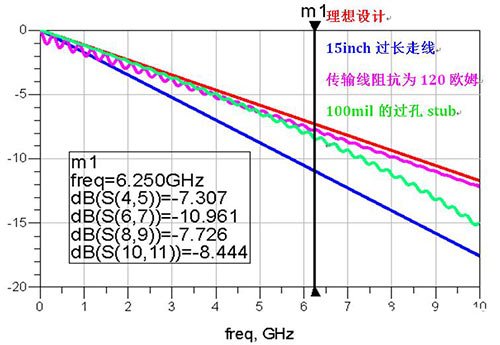

如果換作是你仿真或者測試得到了這樣的眼圖結果后,你能夠很快的找到到底PCB鏈路出現了什么問題導致的嗎?這三個不理想的眼圖結果無論是眼高還是眼寬都比較接近,前面說到的,從時域上看只能看到像過沖,振鈴,或者眼圖閉合的現象,但是原因卻不容易定位到,實際上它們都是PCB鏈路上3種比較典型的鏈路設計問題導致的,分別是線長過長,傳輸線阻抗控制不對和存在換層過孔比較長的stub(殘樁)。如果從它們的S參數去看的話,我們就能看到它們的差異,如圖8所示:

圖8 幾種情況的損耗曲線

首先,從圖8的曲線,至少我們能很清楚的看到幾種情況的差異,對于PCB仿真工程師而言,從頻域的損耗曲線上能看到的東西就更多了。首先我們對比紅色和藍色的損耗曲線,紅色我們知道是10inch的走線,阻抗控制得很理想(100歐姆差分),而且鏈路中沒有換層過孔的stub,因此正如同上面所說的,損耗曲線在整個頻域上線性度比較好,沒有諧振點出現。而我們看藍色的曲線,同樣它的線性度也很好,也沒有諧振點的出現,和紅色曲線的區別僅僅是損耗成比例的增大了,因此我們可以判斷出藍色曲線阻抗同樣控制得很好,只是線長過長導致損耗的增加而已。然后我們看粉紅色的損耗曲線,和理想紅色曲線對比,發現粉紅色曲線呈周期的振蕩,每個振蕩的諧振點頻率間隔相同,根據前面對S參數與阻抗的分析就可以判斷,最有可能導致這種周期振蕩的原因就是傳輸線阻抗控制得不好。最后我們分析綠色的損耗曲線,我們能看到似乎也是周期性的曲線振蕩,但是另外還有一個更明顯的特點,就是越往高頻時,有一個很迅速的非線性跌落,這種比較窄帶的跌落通過是由于鏈路存在分支導致的,因為有分支,在分支反射位置才會出現波形相反相位的疊加,從而導致在該頻率的時候幾乎沒有能量傳輸過去,而對于點對點的高速串行信號鏈路來說,分支主要就是換層過孔的stub,實際上過孔stub的存在和長短,對于高速信號能否良好傳輸有著決定性的影響。

結語

本文主要介紹了如何通過S參數去得到更多的PCB設計信息,從而去探究通道信號質量不理想的原因和找到優化改善的方向。我們去了解信號質量的手段應該是多樣化的,除了傳統的查看時域的波形(眼圖)外,還要從頻域上去衡量。畢竟頻域和時域是相互聯系的。時域具有直觀性,的確是第一時間要去衡量的指標,但是當時域結果不理想且憑經驗又很難去定位問題的時候,從頻域的角度去補充就會是一個很好的選擇。信號完整性的問題表現的形式有很多很多,而且隨著速率的不斷提高,還會有更多的問題出現,本文介紹的S參數表征信號完整性問題僅僅只是冰山一角,S參數能夠提供的信息絕不僅僅如此,篇章所限,只列出以上幾個比較典型的應用。當然無論是從頻域S參數還是時域去分析信號完整性問題,具備一定的理論基礎肯定是前提,只有掌握了較豐富的理論知識,才有可能從得到的各種信號完整性現象中抽絲剝繭,從現象看到本質。

編輯:hfy

-

PCB設計

+關注

關注

396文章

4784瀏覽量

89272 -

信號完整性

+關注

關注

68文章

1435瀏覽量

96455

發布評論請先 登錄

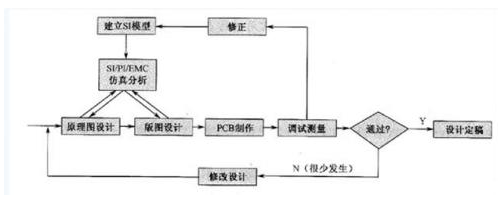

基于信號完整性分析的高速數字PCB的設計方法

基于信號完整性分析的高速數字PCB板的設計開發

基于信號完整性分析的PCB設計流程步驟

基于信號完整性的高速PCB設計流程解析

如何通過S參數去得到更多PCB設計的信號完整性

如何通過S參數去得到更多PCB設計的信號完整性

評論