在過(guò)去的幾年中,已經(jīng)發(fā)布了許多涉及用于半導(dǎo)體器件的高級(jí)封裝體系結(jié)構(gòu)的公告。這些架構(gòu)為產(chǎn)品設(shè)計(jì)人員提供了極大的靈活性,使其能夠異構(gòu)集成在封裝上不同硅工藝上優(yōu)化的不同IP,從而顯著提高性能。

對(duì)高級(jí)封裝的最近興趣是由對(duì)增加封裝上帶寬的需求,對(duì)來(lái)自多個(gè)代工廠的各種IP進(jìn)行集成的需求以及對(duì)提高產(chǎn)量彈性的需求所驅(qū)動(dòng)的。有機(jī)封裝是出色的異構(gòu)集成主流平臺(tái),可在緊湊的外形尺寸中實(shí)現(xiàn)空間轉(zhuǎn)換,并在物理上實(shí)現(xiàn)了封裝上的互連(電源效率高,帶寬高)(圖1)。

圖1英特爾Agilex FPGA提供了一個(gè)封裝上異構(gòu)集成的示例。資料來(lái)源:英特爾

先進(jìn)封裝的目標(biāo)之一是開(kāi)發(fā)越來(lái)越密集的橫向和縱向互連,以使用這些互連創(chuàng)建的管芯到管芯鏈接具有最小的功率損耗和延遲,同時(shí)又能確保信號(hào)完整性。本質(zhì)上,重點(diǎn)是創(chuàng)建接近單片互連性能的封裝上互連,并且在封裝上創(chuàng)建的復(fù)合設(shè)備的行為就像一個(gè)虛擬的單片實(shí)體。

2D和3D架構(gòu)

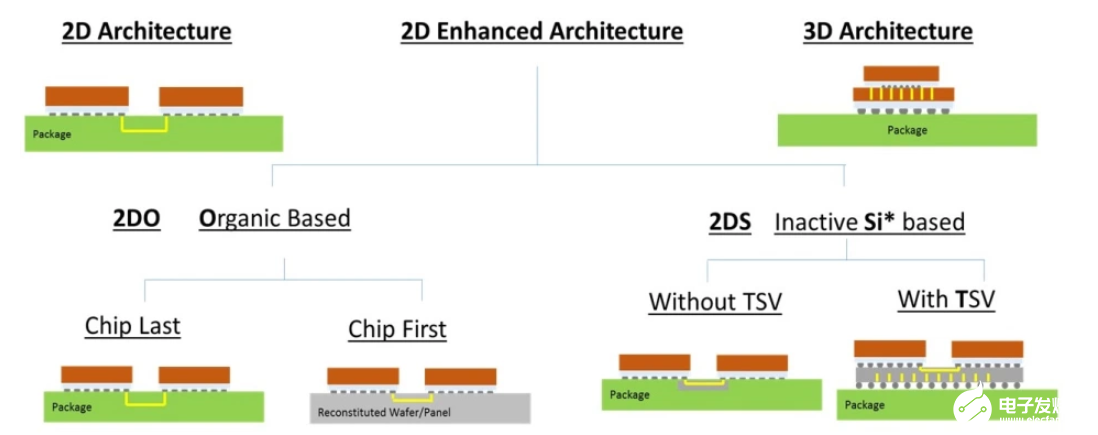

封裝上互連以及具有這些互連的更廣泛的封裝體系結(jié)構(gòu)可以在封裝的xy平面中分為2D和3D(圖2)。

圖22D和3D架構(gòu)的互連術(shù)語(yǔ)。資料來(lái)源:電子封裝協(xié)會(huì),IEEE

2D架構(gòu)定義為兩個(gè)或更多有源硅器件并排放置在封裝上并在封裝上互連的架構(gòu)。如果互連是“增強(qiáng)型的”(互連密度比主流有機(jī)封裝更高,并且可以使用有機(jī)介質(zhì)完成),則該體系結(jié)構(gòu)還可以進(jìn)一步細(xì)分為2D有機(jī)(2DO)體系結(jié)構(gòu)。同樣,如果增強(qiáng)型體系結(jié)構(gòu)使用無(wú)機(jī)介質(zhì)(硅,玻璃或陶瓷中介層或橋接器),則該體系結(jié)構(gòu)進(jìn)一步細(xì)分為2DS體系結(jié)構(gòu)。

3D架構(gòu)被定義為兩個(gè)或更多有源硅器件在沒(méi)有封裝代理的情況下堆疊并互連的架構(gòu)。在此定義中,短語(yǔ)“在沒(méi)有封裝代理的情況下互連”僅表示有源硅片之間的互連不通過(guò)封裝,因此它們的設(shè)計(jì)和性能不直接取決于封裝體系結(jié)構(gòu)。

互連密度

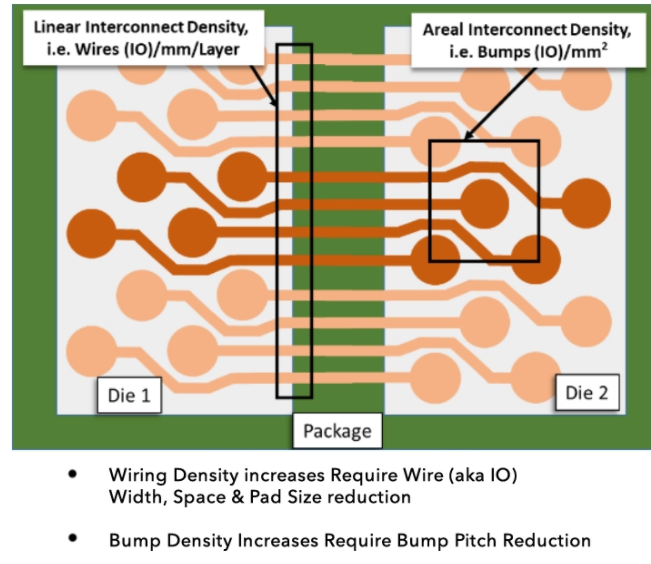

物理互連密度可以通過(guò)兩個(gè)關(guān)鍵指標(biāo)來(lái)捕獲(圖3)。線密度表示從芯片邊緣向外逃逸的導(dǎo)線數(shù)量,以進(jìn)行側(cè)向的芯片到芯片互連,而面密度表示用于形成垂直連接的凸塊數(shù)量。

圖3可以通過(guò)這兩個(gè)關(guān)鍵指標(biāo)來(lái)捕獲線性和區(qū)域互連密度。資料來(lái)源:英特爾

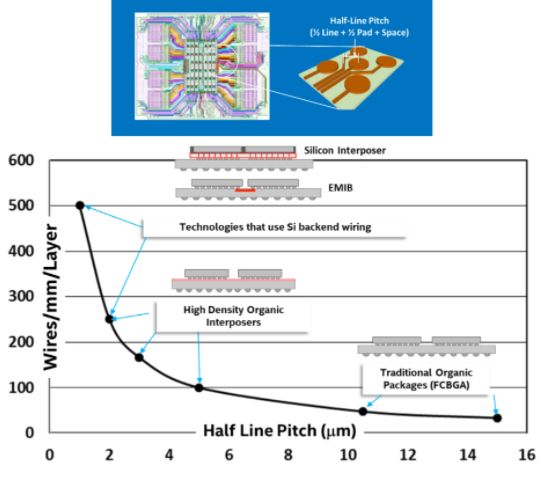

圖4和圖5描述了不同包裝技術(shù)的線性和平面密度的包絡(luò)線。如兩個(gè)圖所示,使用不同的互連體系結(jié)構(gòu),可以實(shí)現(xiàn)廣泛的互連密度。通常,使用硅后端布線的技術(shù)具有最高的布線密度,因?yàn)樗鼈兲峁┝烁?xì),間距更緊密的布線(圖4)。

圖4該圖顯示了不同高級(jí)封裝體系結(jié)構(gòu)的線性互連密度包絡(luò)。資料來(lái)源:英特爾

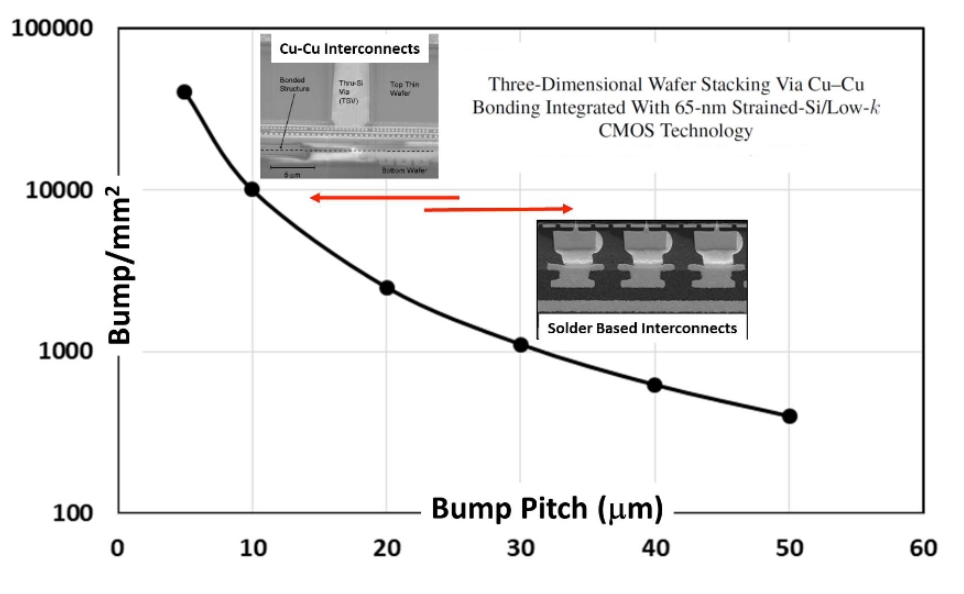

這些技術(shù)可以實(shí)現(xiàn)并行,寬且緩慢的芯片到芯片鏈接,并且需要特別注意鏈接設(shè)計(jì),以解決布線密度增加帶來(lái)的信號(hào)完整性問(wèn)題。隨著凸點(diǎn)間距的縮小,平面的凸點(diǎn)密度與凸點(diǎn)間距的平方的倒數(shù)成正比(圖5)。

圖5該圖顯示了面積互連密度與凸塊間距和架構(gòu)的關(guān)系。資料來(lái)源:英特爾

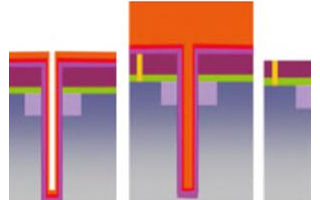

如今,大多數(shù)面積的芯片到芯片和芯片到封裝的互連都使用焊料來(lái)形成接頭。隨著凸點(diǎn)間距的縮小,從焊料到使用Cu-Cu互連(約20-25μm)將有過(guò)渡,以實(shí)現(xiàn)持續(xù)的互連密度縮放。因此,工業(yè)上的重點(diǎn)是增加Cu-Cu互連的技術(shù)范圍。

互連密度縮放的一個(gè)常見(jiàn)的根本原因是需要增加封裝上裸片到裸片鏈路的帶寬。帶寬縮放速率可用于定義互連縮放路線圖。根據(jù)《異構(gòu)集成路線圖2019年版》,互連技術(shù)擴(kuò)展路線圖可實(shí)現(xiàn)鏈路帶寬的世代加倍。

圖6顯示了用于異構(gòu)集成的高級(jí)包裝體系結(jié)構(gòu)的一些示例。

圖6一些先進(jìn)的軟件包體系結(jié)構(gòu)在所有三個(gè)維度上提供了更多的分區(qū)機(jī)會(huì)和規(guī)模擴(kuò)展。資料來(lái)源:英特爾

軟件包與系統(tǒng)設(shè)計(jì)師之間的協(xié)作

隨著高級(jí)包裝技術(shù)的發(fā)展,它們將通過(guò)異構(gòu)集成提供更高的包裝性能,從而使性能越來(lái)越高的系統(tǒng)成為可能。通過(guò)加強(qiáng)包裝和系統(tǒng)設(shè)計(jì)人員之間的協(xié)作伙伴關(guān)系,可以更好地實(shí)現(xiàn)此系統(tǒng)性能。

下面列出了一些合作伙伴關(guān)系將如何幫助最大化系統(tǒng)性能的示例:

系統(tǒng)板的功能,材料和設(shè)計(jì)必須不斷發(fā)展以支持更高的速度和更高的帶寬信令。封裝和系統(tǒng)協(xié)同設(shè)計(jì)方法可創(chuàng)建功耗最大化,成本優(yōu)化的系統(tǒng)鏈接,從而最大程度地提高帶寬,從而有助于最大化系統(tǒng)性能。

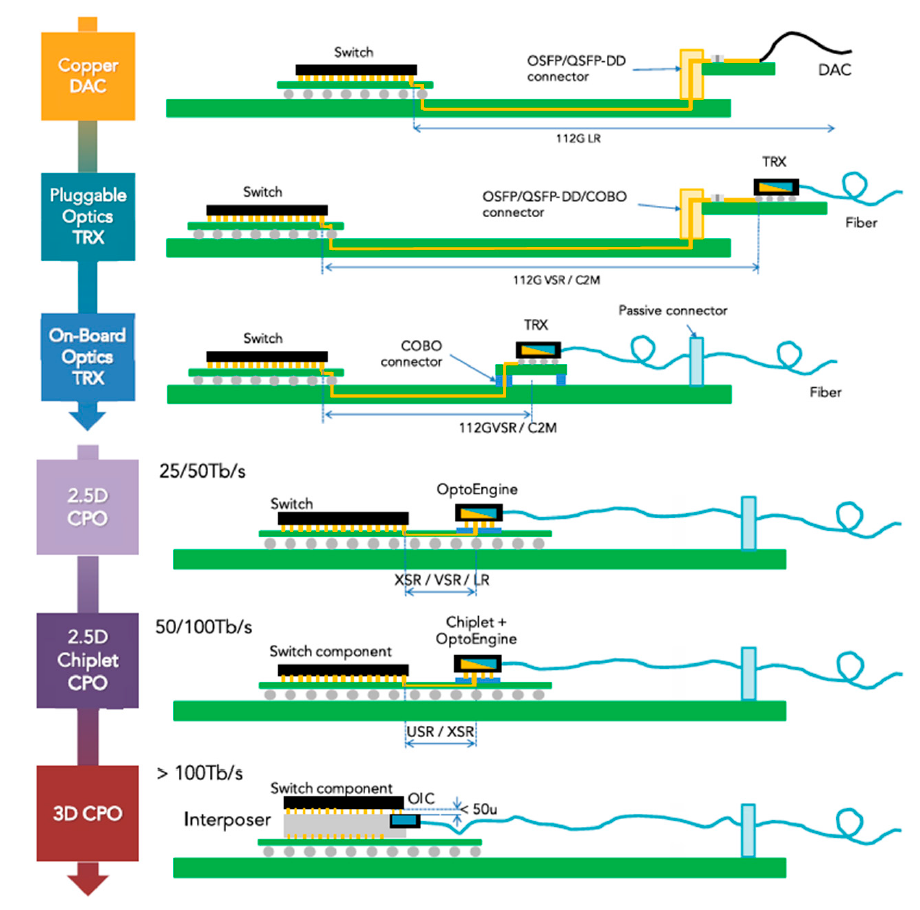

可以預(yù)見(jiàn),除了電氣鏈路之外,將來(lái)還將需要光子學(xué)和無(wú)線鏈路以最大程度地?cái)U(kuò)大覆蓋范圍和帶寬。開(kāi)發(fā)和擴(kuò)散這些不同的信令技術(shù)將需要協(xié)作以實(shí)現(xiàn)標(biāo)準(zhǔn)化的模塊化可擴(kuò)展性。

將需要專注于開(kāi)發(fā)有效的系統(tǒng)電源傳輸網(wǎng)絡(luò)。

符合系統(tǒng)尺寸和可靠性要求的整體系統(tǒng)冷卻方法將確保系統(tǒng)冷卻能力不會(huì)限制系統(tǒng)性能。

模塊化和可伸縮性將需要在系統(tǒng)級(jí)別使用的各種連接器技術(shù)中構(gòu)建。

總之,當(dāng)今有許多先進(jìn)的包裝技術(shù)可用來(lái)提高包裝上異構(gòu)集成IP的性能。這些技術(shù)著重于擴(kuò)展互連密度,以幫助擴(kuò)展封裝上芯片對(duì)芯片鏈接之間的帶寬并提高性能。軟件包與系統(tǒng)設(shè)計(jì)人員之間的緊密合作,以優(yōu)化軟件包系統(tǒng)集成,將有助于最大化系統(tǒng)性能。

RAVI MAHAJAN,英特爾研究員,是技術(shù)發(fā)展的組裝和測(cè)試未來(lái)技術(shù)的英特爾共同主任。

編輯:hfy

-

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1432瀏覽量

96433 -

系統(tǒng)設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

163瀏覽量

21935 -

半導(dǎo)體器件

+關(guān)注

關(guān)注

12文章

776瀏覽量

32761

發(fā)布評(píng)論請(qǐng)先 登錄

分享兩種前沿片上互連技術(shù)

芯片互連技術(shù)深度解析:焊球、銅柱與微凸點(diǎn)的奧秘

半導(dǎo)體封裝革新之路:互連工藝的升級(jí)與變革

光電共封裝技術(shù)CPO的演變與優(yōu)勢(shì)

英特爾IEDM 2024大曬封裝、晶體管、互連等領(lǐng)域技術(shù)突破

研究透視:芯片-互連材料

一文了解晶圓級(jí)封裝中的垂直互連結(jié)構(gòu)

先進(jìn)封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進(jìn)展

探索倒裝芯片互連:從原理到未來(lái)的全面剖析

柔性基板異質(zhì)集成系統(tǒng)的印刷互連技術(shù)

硅通孔三維互連與集成技術(shù)

芯片和封裝級(jí)互連技術(shù)的最新進(jìn)展

高密度互連,引爆后摩爾技術(shù)革命

TE推出AMPMODU互連系統(tǒng)產(chǎn)品特色是什么?-赫聯(lián)電子

銅互連,尚能飯否?

高級(jí)封裝技術(shù):創(chuàng)建接近單片互連性能的封裝上互連

高級(jí)封裝技術(shù):創(chuàng)建接近單片互連性能的封裝上互連

評(píng)論