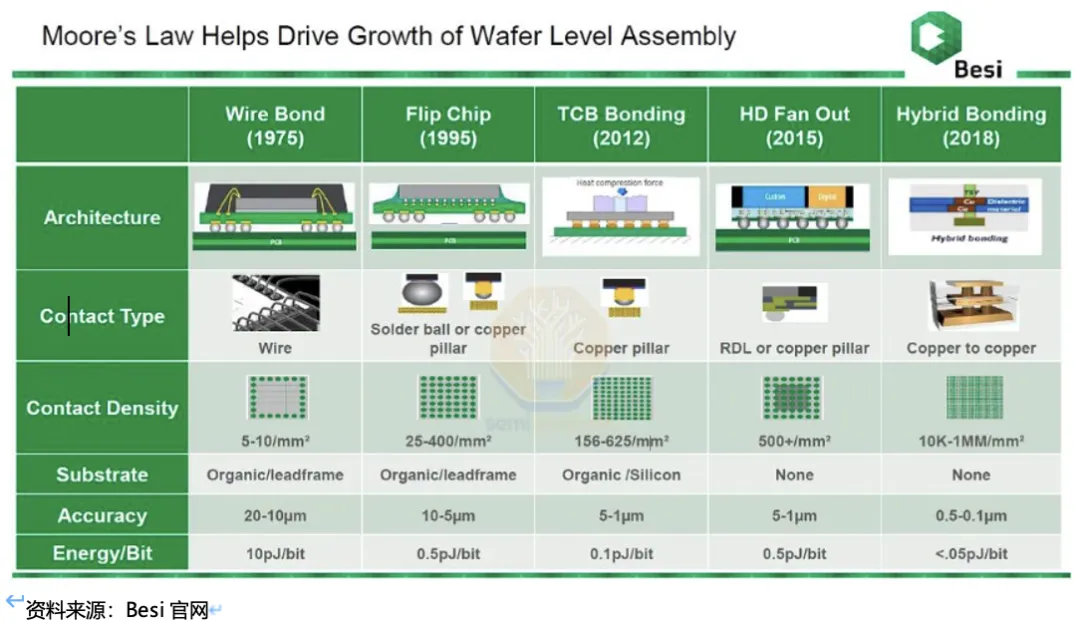

隨著電子設(shè)備向小型化、高性能化發(fā)展,芯片封裝技術(shù)也在不斷演進(jìn)。高密度芯片封裝是滿足現(xiàn)代電子產(chǎn)品需求的關(guān)鍵技術(shù)之一,而芯片互連技術(shù)作為封裝的核心環(huán)節(jié),經(jīng)歷了從焊球到銅柱再到微凸點(diǎn)的技術(shù)革新。本文將從高密度芯片封裝的發(fā)展歷程出發(fā),解析焊球、銅柱及微凸點(diǎn)三種互連技術(shù)的定義、材料、制作工藝、適用范圍、用途及典型案例,并將這些技術(shù)融入芯片封裝發(fā)展的歷史背景中,展現(xiàn)其在不同階段的作用與意義。

芯片封裝發(fā)展歷程與互連技術(shù)的演進(jìn)

1. 早期階段:20世紀(jì)90年代——焊球技術(shù)的興起

背景:隨著集成電路(IC)復(fù)雜度的提升,傳統(tǒng)的引線鍵合技術(shù)已無法滿足高密度封裝的需求。焊球技術(shù)(Ball Grid Array, BGA)應(yīng)運(yùn)而生,成為主流互連技術(shù)。BGA通過將焊球陣列排列在芯片底部,實(shí)現(xiàn)了更高的引腳密度和更短的信號傳輸路徑。

焊球技術(shù)

·定義:通過將焊球排列成陣列形式,實(shí)現(xiàn)芯片與基板互連的技術(shù)。

·材料:通常采用錫鉛(Sn-Pb)合金或無鉛合金(如Sn-Ag-Cu)。

·制作工藝:在芯片底部制作焊盤,通過絲網(wǎng)印刷或電鍍技術(shù)形成焊球,再通過回流焊實(shí)現(xiàn)連接。

·適用范圍:中等密度封裝,適用于消費(fèi)電子、通信設(shè)備等領(lǐng)域。

·典型案例:Intel的早期處理器封裝、手機(jī)基帶芯片封裝。

意義:焊球技術(shù)解決了傳統(tǒng)引線鍵合技術(shù)的引腳密度和信號傳輸瓶頸,推動了高密度封裝的發(fā)展。

2. 中期階段:20世紀(jì)90年代——銅柱技術(shù)的引入

背景:隨著芯片尺寸的縮小和I/O數(shù)量的增加,焊球的尺寸和間距逐漸接近物理極限。銅柱技術(shù)(Copper Pillar)因其更高的機(jī)械強(qiáng)度和更小的間距優(yōu)勢,逐漸在高性能芯片封裝中得到應(yīng)用。

銅柱技術(shù)

·定義:通過銅柱實(shí)現(xiàn)芯片與基板互連的技術(shù),具有更高的機(jī)械強(qiáng)度和更小的間距。

·材料:純銅或銅合金,頂部涂覆錫銀(Sn-Ag)合金。

·制作工藝:在芯片底部制作銅柱,通過熱壓焊將銅柱與基板連接。

·適用范圍:高密度封裝,適用于高性能計算、服務(wù)器等領(lǐng)域。

·典型案例:NVIDIA的高性能GPU封裝、高端服務(wù)器處理器封裝。

意義:銅柱技術(shù)進(jìn)一步提升了封裝密度和性能,滿足了高性能計算和服務(wù)器領(lǐng)域的需求。

3. 現(xiàn)階段:2010年代至今——微凸點(diǎn)技術(shù)的突破

背景:隨著摩爾定律的延續(xù),芯片特征尺寸進(jìn)一步縮小,傳統(tǒng)的焊球和銅柱技術(shù)已難以滿足超高性能和超小尺寸封裝的需求。微凸點(diǎn)技術(shù)(Micro Bump)通過更小的尺寸和更高的密度,成為3D封裝和異構(gòu)集成的主流選擇。

微凸點(diǎn)技術(shù)

·定義:通過微米級凸點(diǎn)實(shí)現(xiàn)芯片與基板或芯片與芯片互連的技術(shù)。

·材料:錫銀(Sn-Ag)合金或銅鎳(Cu-Ni)合金。

·制作工藝:在芯片表面制作微凸點(diǎn),通過熱壓焊或回流焊實(shí)現(xiàn)互連。

·適用范圍:超高密度封裝,適用于3D封裝、異構(gòu)集成等領(lǐng)域。

·典型案例:AMD的3D V-Cache技術(shù)、蘋果M系列處理器的異構(gòu)集成。

意義:微凸點(diǎn)技術(shù)推動了3D封裝和異構(gòu)集成的發(fā)展,為芯片性能的進(jìn)一步提升提供了技術(shù)支持。

焊球、銅柱及微凸點(diǎn)技術(shù)對比

| 技術(shù)特性 | 焊球技術(shù) | 銅柱技術(shù) | 微凸點(diǎn)技術(shù) |

| 定義 | 焊球陣列互連 | 銅柱互連 | 微米級凸點(diǎn)互連 |

| 材料 | Sn-Pb或Sn-Ag-Cu | 純銅或銅合金 | Sn-Ag或Cu-Ni合金 |

| 制作工藝 | 絲網(wǎng)印刷、回流焊 | 電鍍、熱壓焊 | 光刻、熱壓焊 |

| 適用范圍 | 中等密度封裝 | 高密度封裝 | 超高密度封裝 |

| 用途 | 芯片與基板互連 | 高性能芯片互連 | 3D封裝、異構(gòu)集成 |

| 典型案例 | Intel早期處理器 | NVIDIA GPU | AMD 3D V-Cache |

| 歷史發(fā)展 | 1990年代興起 | 2000年代引入 | 2010年代突破 |

| Pad節(jié)距 | 0.5 mm - 1.0 mm | 0.2 mm - 0.5 mm | 0.05 mm - 0.2 mm |

總結(jié)

焊球、銅柱及微凸點(diǎn)技術(shù)分別代表了芯片互連技術(shù)在不同發(fā)展階段的核心突破。從20世紀(jì)90年代的焊球技術(shù)到21世紀(jì)初的銅柱技術(shù),再到2010年代至今的微凸點(diǎn)技術(shù),每一種技術(shù)都在特定的歷史階段解決了封裝密度和性能的瓶頸問題,推動了芯片封裝技術(shù)的不斷演進(jìn)。焊球技術(shù)適用于中等密度封裝,Pad節(jié)距為0.5 mm - 1.0 mm;銅柱技術(shù)適用于高密度封裝,Pad節(jié)距為0.2 mm - 0.5 mm;微凸點(diǎn)技術(shù)則適用于超高密度封裝,Pad節(jié)距為0.05 mm - 0.2 mm。未來,隨著3D封裝和異構(gòu)集成的進(jìn)一步發(fā)展,微凸點(diǎn)技術(shù)將繼續(xù)引領(lǐng)芯片互連技術(shù)的創(chuàng)新潮流,為電子設(shè)備的小型化和高性能化提供更強(qiáng)大的支持

-

芯片

+關(guān)注

關(guān)注

459文章

52487瀏覽量

440629 -

焊球

+關(guān)注

關(guān)注

0文章

11瀏覽量

6130

原文標(biāo)題:芯片互連技術(shù)解析:焊球、銅柱及微凸點(diǎn)

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

從焊料工程師視角揭秘先進(jìn)封裝里凸點(diǎn)制作那些事兒?

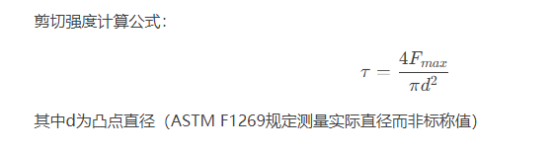

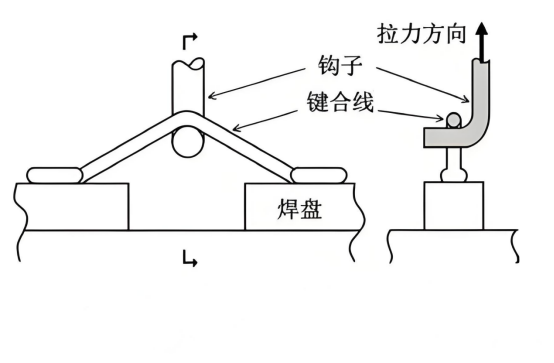

LTCC焊球可靠性提升方案:推拉力測試儀的測試標(biāo)準(zhǔn)與失效診斷

從工藝到設(shè)備全方位解析錫膏在晶圓級封裝中的應(yīng)用

XSR芯片間互連技術(shù)的定義和優(yōu)勢

ASTM F1269標(biāo)準(zhǔn)解讀:推拉力測試機(jī)在BGA焊球可靠性測試中的應(yīng)用

BGA封裝焊球推力測試解析:評估焊點(diǎn)可靠性的原理與實(shí)操指南

深度解析激光錫焊中鉛與無鉛錫球的差異及大研智造解決方案

焊接強(qiáng)度測試儀如何助力冷/熱焊凸塊焊接質(zhì)量評估,一文詳解

什么是先進(jìn)封裝中的Bumping

BGA芯片封裝凸點(diǎn)工藝:技術(shù)詳解與未來趨勢

先進(jìn)封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進(jìn)展

芯片互連技術(shù)深度解析:焊球、銅柱與微凸點(diǎn)的奧秘

芯片互連技術(shù)深度解析:焊球、銅柱與微凸點(diǎn)的奧秘

評論