近日有消息稱,蘋果已著手進行新一代A15系列處理器開發,預期會采用臺積電5nm加強版N5P制程,明年第三季開始投片。

據傳蘋果將在A15芯片中使用臺積電的5納米技術

晶圓代工龍頭臺積電及微影設備大廠ASML于上周法人說明會透露了更多3納米細節,臺積電3納米采用鰭式場效電晶體FinFET架構及極紫外光EUV微影技術,邏輯密度與5納米相較將大幅增加70%,且EUV光罩層數將倍增且超過20層。

為此,臺積電積極采購EUV曝光機設備,未來三到五年仍將是擁有全球最大EUV產能的半導體廠,包括家登及崇越等供應商可望受惠。

臺積電EUV微影技術已進入量產且制程涵蓋7+納米、6納米、5納米,據設備業者消息,臺積電7+納米采用EUV光罩層最多達四層,超微新一代 Zen 3 架構處理器預期是采用該制程量產。

6納米已在第四季進入量產,EUV光罩層數較7+納米增加一層,包括聯發科、輝達、英特爾等大廠都將采用6納米生產新一代產品。

臺積電下半年開始量產5納米制程,主要為蘋果量產A14及A14X處理器,包括超微、高通、輝達、英特爾、博通、邁威爾等都會在明年之后導入5納米制程量產新一代產品。

5納米EUV光罩層數最多可達14層,所以Fab 18廠第一期至第三期已建置龐大EUV曝光機臺設備因應強勁需求,臺積電明年將推出5納米加強版N5P制程并導入量產,后年將推出5納米優化后的4納米制程,設備業者預期N5P及4納米的EUV光罩層數會較5納米增加。

臺積電在日前的法說會中宣布,3納米研發進度符合預期且會是另一個重大制程節點,與5納米制程相較,3納米的邏輯密度可增加70%,在同一功耗下可提升15%的運算效能,在同一運算效能下可減少30%功耗。

3納米制程采用的EUV光罩層數首度突破20層,業界預估最多可達24層。

ASML執行長Peter Wennink在日前法說會中指出,5納米邏輯制程采用的EUV光罩層數將超過10層,3納米制程采用的EUV光罩層數會超過20層,隨著制程微縮EUV光罩層數會明顯增加,并取代深紫外光DUV多重曝光制程。

臺積電5納米及3納米的EUV光罩層數倍數增加,提供EUV光罩盒EUV Pod的家登受惠最大,今、明兩年產能均已被大客戶預訂一空。

至于EUV產能大幅提高,代理EUV光阻液的崇越接單暢旺,訂單同樣排到明年下半年。

責任編輯:tzh

-

處理器

+關注

關注

68文章

19826瀏覽量

233818 -

芯片

+關注

關注

459文章

52271瀏覽量

437312 -

半導體

+關注

關注

335文章

28685瀏覽量

233710 -

晶圓

+關注

關注

52文章

5130瀏覽量

129261

發布評論請先 登錄

MediaTek推出新一代Kompanio Ultra處理器

米爾NXP i.MX 91核心板發布,助力新一代入門級Linux應用開發

nRF54系列新一代無線 SoC

Nordic新一代旗艦芯片nRF54H20深度解析

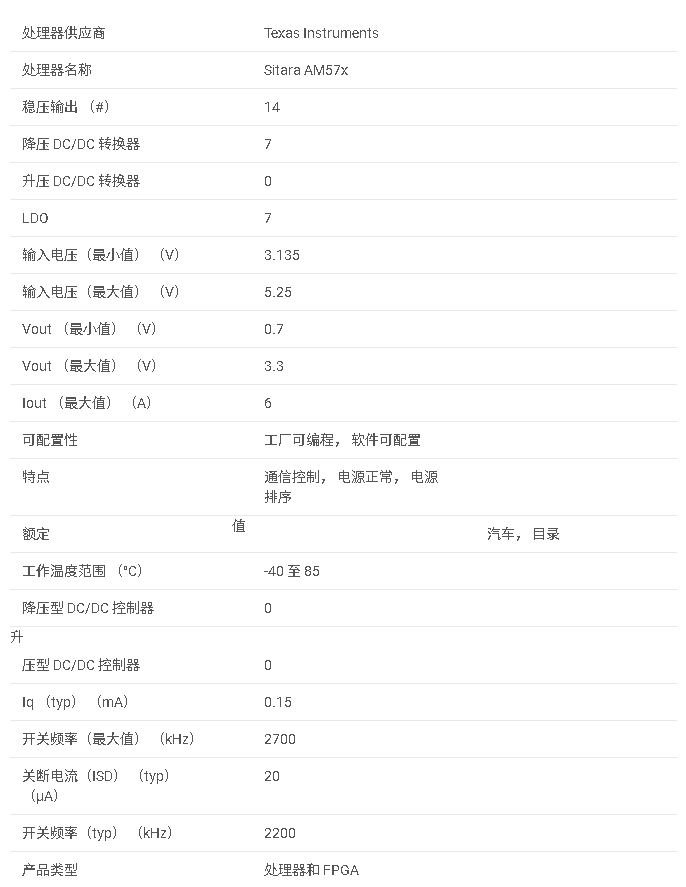

TPS659037 用于 ARM Cortex A15 處理器的電源管理 IC (PMIC)數據手冊

蘋果已著手進行新一代A15系列處理器開發

蘋果已著手進行新一代A15系列處理器開發

評論