走線出現(xiàn)小方塊的示意圖如下所示:

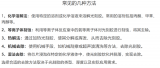

這種情況出現(xiàn)并不影響pcb生產(chǎn)以及布線的聯(lián)通性,只是影響美觀性能,去除的方法比較簡單,這個是由模塊復(fù)用以后,沒有打散模塊引起的。將模塊的打散即可。操作如下:

首先切換模式到布局模式,點擊菜單欄setup-Application Mode,然后選擇Placement Edit模式;

Find面板里面選擇模塊Groups;

鼠標(biāo)移動到Groups上面,整個模塊會顯示臨時高亮的顏色,點擊鼠標(biāo)右鍵,選擇Disband groups即可

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4349文章

23403瀏覽量

406418 -

allegro

+關(guān)注

關(guān)注

42文章

699瀏覽量

146883 -

走線

+關(guān)注

關(guān)注

3文章

118瀏覽量

24190

發(fā)布評論請先 登錄

Allegro Skill封裝功能之導(dǎo)出單個封裝介紹

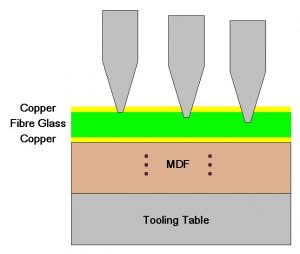

深入了解 PCB 制造技術(shù):銑削

PCB生產(chǎn)線:沖破技術(shù)瓶頸,領(lǐng)航電子征途

芯片濕法刻蝕殘留物去除方法

有什么方法可以去除晶圓鍵合邊緣缺陷?

金屬方塊電阻的測試條件

Poly方塊電阻的測試條件

PW方塊電阻的測試條件

去除晶圓表面顆粒的原因及方法

國產(chǎn)力量崛起!鴻道Intewell操作系統(tǒng)推動我國制造業(yè)不斷升級

基于FPGA的“俄羅斯方塊”設(shè)計(附代碼)

Cadence快板PCB培訓(xùn)

Allegro X 23.11 版本更新 I PCB 設(shè)計:DFA_BOUND 用于 DFA 規(guī)則設(shè)定

PCB技術(shù):Allegro中去除走線小方塊的方法

PCB技術(shù):Allegro中去除走線小方塊的方法

評論