作者: 小魚,Xilinx學術合作

一. 概述

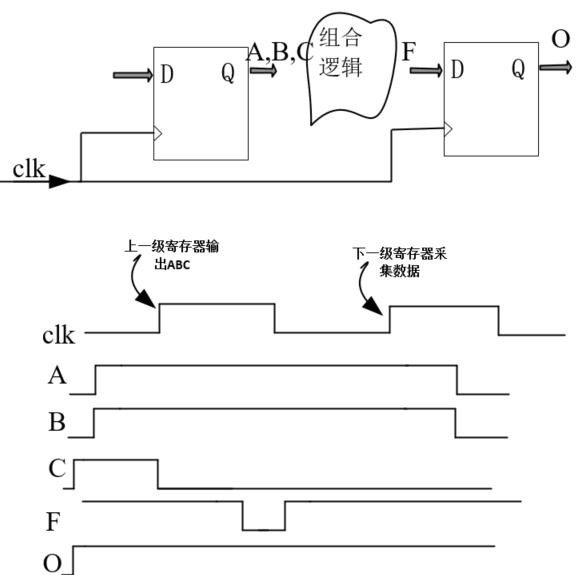

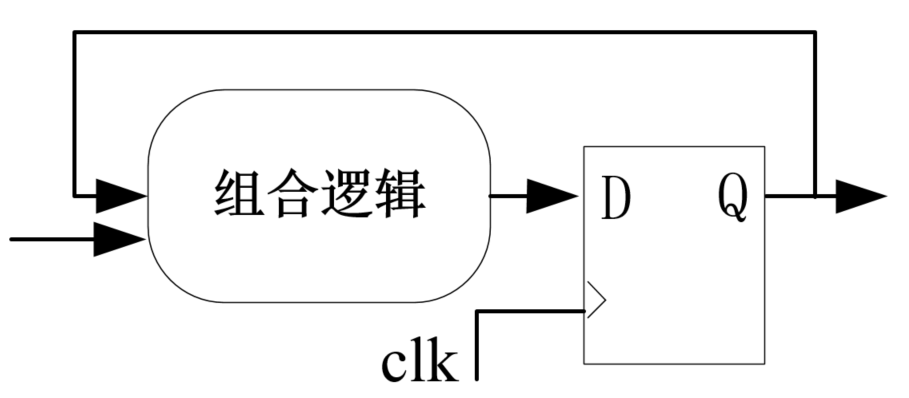

時序邏輯示意圖,如下圖所示。數據從一個寄存器出來,經過組合邏輯到達下一個寄存器。

在學習數字電路的過程中,我們都知道時序邏輯,但是大家對時序邏輯真的了解嗎?

(1)純組合邏輯電路的缺點在哪?

(3)純組合邏輯電路完成不了什么功能?

(2)為什么需要時鐘和寄存器呢?

帶著這三個疑問我們來認識一下時序邏輯電路。

二. 同步時序邏輯電路的作用

1. 時序邏輯電路對于組合邏輯的毛刺具有容忍度,從而改善電路的時序特性。同時電路的更新由時鐘控制。

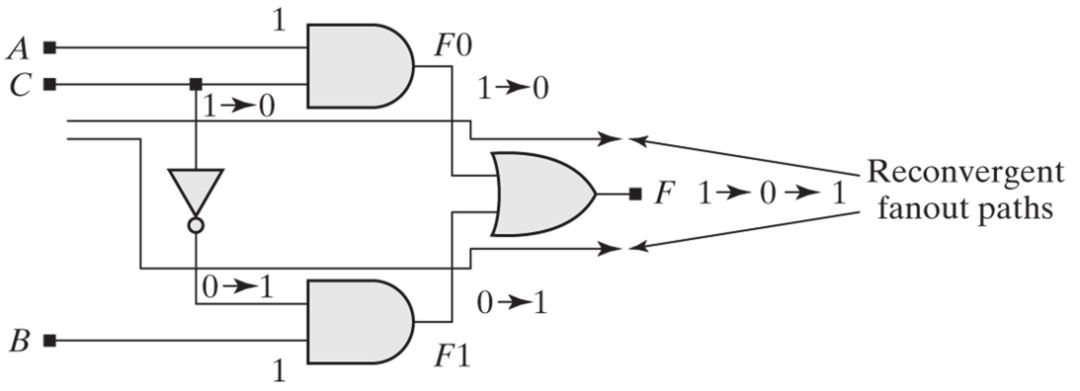

比如,在組合邏輯中當各路信號的路徑長度不一樣時那么組合邏輯的輸出就會出現毛刺。如下圖所示。F0和F1到達最后一個或門的路徑長度不一樣,那么在F端就會出現毛刺。

圖片來自書籍《Verilog HDL高級數字設計》

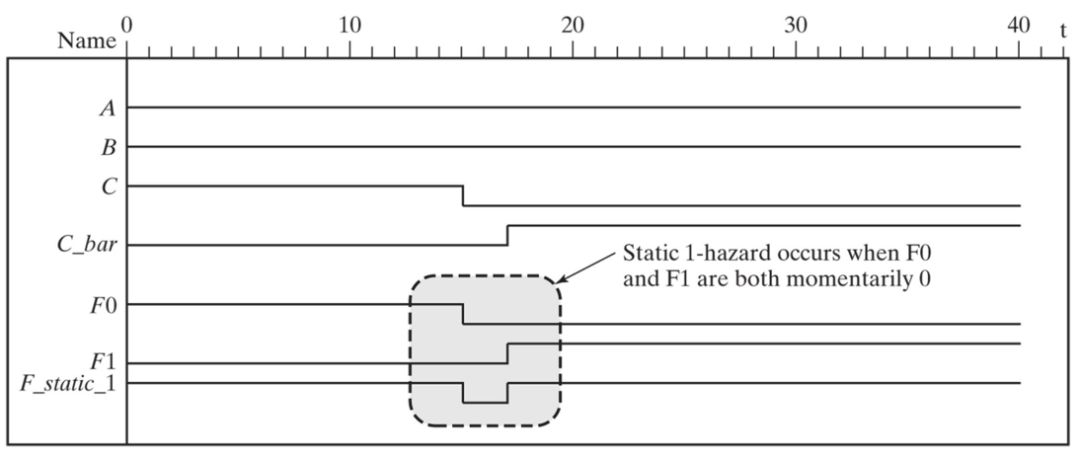

毛刺信號如下圖影印部分所示,由于C經過一個非門才到達下面的與門,故F1相對于F0有延遲,那么在F端就會造成毛刺,這個毛刺就是有短暫的時間輸出為0。

圖片來自書籍《Verilog HDL高級數字設計》

但是利用時序電路,數據A,B,C的觸發是在時鐘沿,輸出信號F也是在時鐘沿去采,而這個時鐘沿到來的時間是在F輸出穩定之后,故對電路的毛刺具有容忍度。如下圖,可以看到最后寄存器的輸出O就不存在毛刺。

這個特性使得在時序邏輯電路里面,電路的輸出被采集到寄存器里面,并送往下一級電路的時候都是確定的而且是準確的,從而整體電路都是隨著時鐘沿在更新。

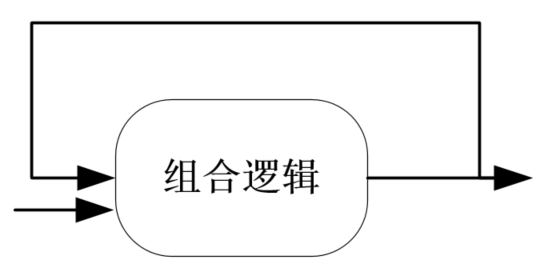

2. 純組合邏輯只能由當前輸入決定當前輸出,而不能實現帶反饋的邏輯,如下圖所示,這樣的話,你的電路就會陷入死循環而無法使用。

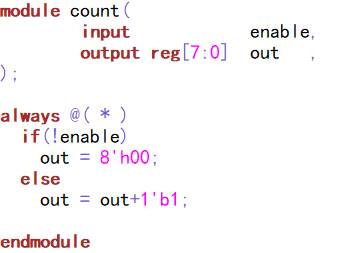

比如做一個計數器,如果我們用如下的組合邏輯的方式描述就會出問題。

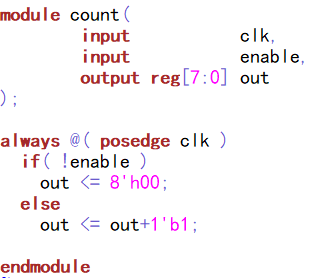

而這種帶反饋的邏輯,必須要通過寄存器把輸出暫存起來,再由時鐘沿去控制數據的反饋更新,這樣電路才有意義。

故計數器的正確描述方式如下。

編輯:hfy

-

FPGA

+關注

關注

1643文章

21964瀏覽量

614111 -

寄存器

+關注

關注

31文章

5421瀏覽量

123343

發布評論請先 登錄

數字電路設計之同步時序邏輯電路

數字電路設計之同步時序邏輯電路

評論