由于Vivado下載程序步驟和ISE有較大差異,特此寫此文章,希望對大家有所幫助。

1,下載文件生成

在.bit文件生成后,在TCL中輸入

write_cfgmem -format mcs -interface spix4 -size 16 -loadbit "up 0x0 F:/Git/XGA/Display_HDMI/Display.runs/impl_2/Display.bit" -file FPGA_TOP.mcs

spix4為模式設置。

-size 16為Flash大小,單位Byte。

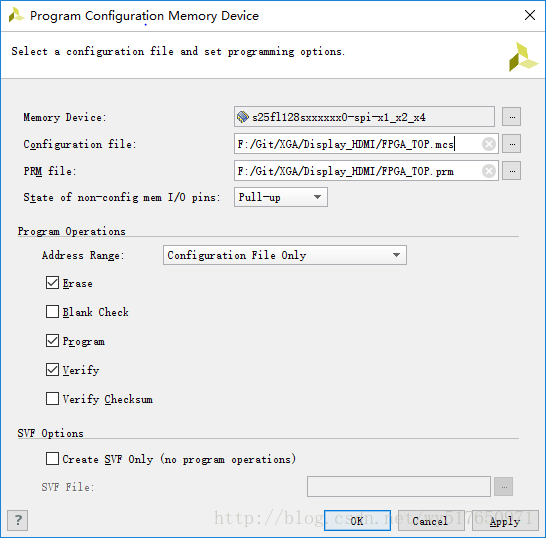

即可得到FPGA_TOP.mcs和FPGA_TOP.prm兩個文件,后邊需要用到這兩個文件。

A&Q:提示bit位寬錯誤

ERROR: [Writecfgmem 68-20] SPI_BUSWIDTH property is set to "1" on bitfile F:/Git/XGA/Display_HDMI/Display.runs/impl_2/Display.bit. This property has to be set to "4" to generate a configuration memory file for the SPIX4 interface. Please ensure that a valid value has been set for the property BITSTREAM.Config.SPI_buswidth and rerun this command.

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

輸入如上命令,將BIT位寬更改為4bit。

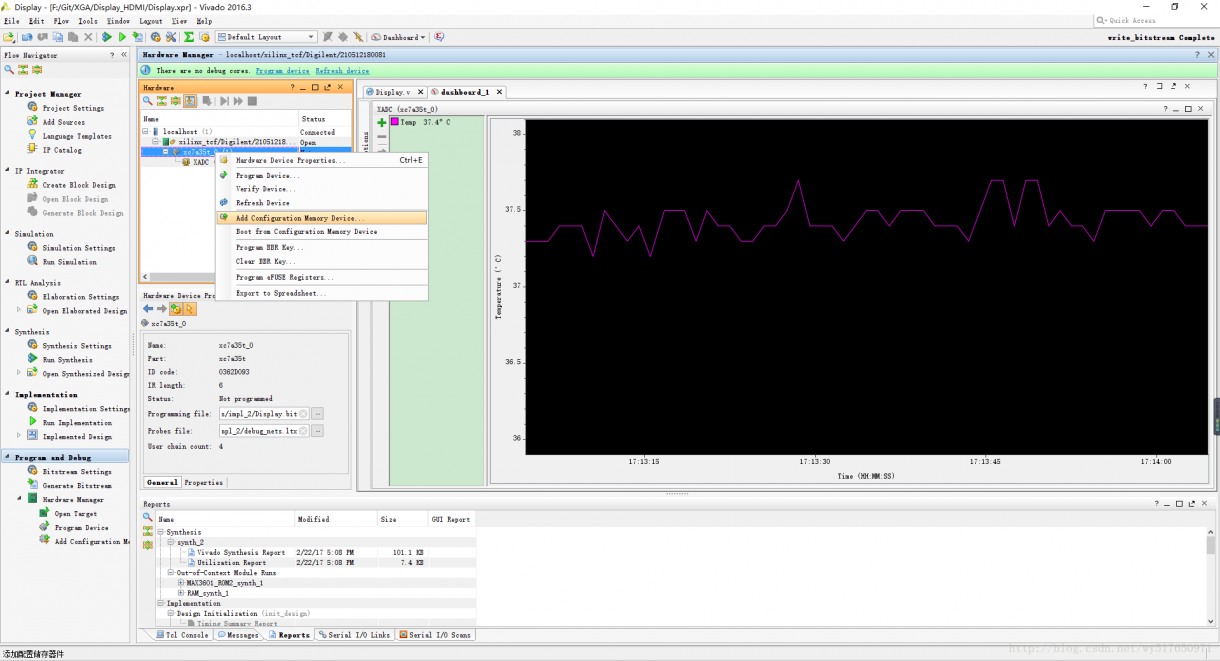

2,程序下載

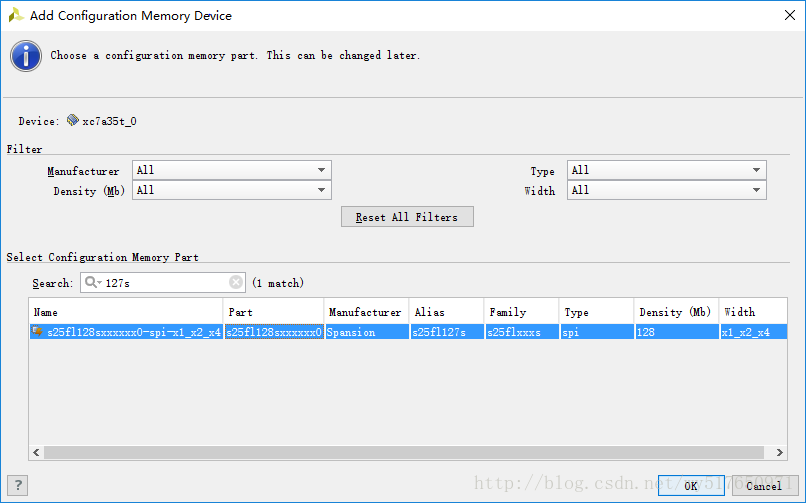

選擇你所使用的的Flash,如果此選項中沒有,則可去官網查詢該系列FPGA時候支持此款Flash。

點擊OK即可。

A&Q:下載進去,重新上電后,程序不運行。

1,檢查SPI_clk是否有時鐘產生。

A,有,則證明FPGA上電配置正確。

B,無

a,檢查MODE配置模式,一般我們配置為SPI主模式,即MODE[2:0]=001;

b,檢查MODE上下拉電阻,官方手冊上推薦使用100歐,Nexys4則使用1K。這個電阻不宜過大,否則造成上電啟動失敗。

編輯:hfy

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614052 -

ISE

+關注

關注

1文章

102瀏覽量

37452 -

Vivado

+關注

關注

19文章

828瀏覽量

68217

發布評論請先 登錄

ISE/Isim的Vivado許可證不起作用

Vivado 2013.4和ISE 14.7的下載具有錯誤的MD5校驗和

Vivado的PR許可證是否與ISE不同?

如何卸載ISE webpack并使用Vivado webpack代替

怎么將Vivado項目轉換為ISE項目

Vivado和ISE哪個更好?

如何使用腳本運行ISE/VIVADO

在Vivado 2015.4和ISE 14.7中實現的相同設計之間的資源利用率是否會有任何差異?

無法下載vivado安裝程序怎么辦

Vivado與ISE的開發流程以及性能差異

ISE約束導入vivado總共分幾步

Vivado下載程序步驟和ISE差異問題

Vivado下載程序步驟和ISE差異問題

評論