本篇主要介紹PCIe總線的AC耦合電容、總線的去加重等高速信號調整技術。

AC耦合電容可以參考之前的文章《邏輯電平之差分互連AC耦合電容(7)》,本文主要針對PCIe接口介紹AC耦合電容的實際使用。

信號調整相關資料可以參考之前的文章《高速信號調整技術》,本文主要針對PCIe介紹其使用的具體的調整技術。

1、AC耦合電容

一般使用AC耦合電容是為了提供直流偏壓。直流偏壓就是濾除信號的直流分量,使信號關于0軸對稱。

從這個作用看,其實理想電容應該可以放在通道的任何一個地方。但實際電路中的電容并非理想的,有寄生電感的存在,而且焊盤和換層過孔都是阻抗不連續點。

那為什么PCIe要求放在發送端呢?其實仔細看PCIe規范是說如果是兩塊板連接時,要放在發送的那塊板上。如果發送接收在同一塊板上,那么就隨意吧,但最好靠近一端。

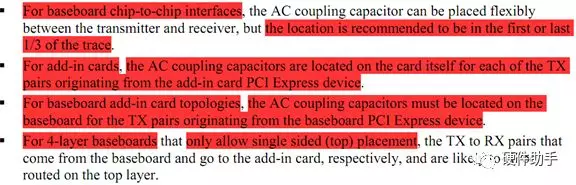

下面是從PCIe 3.0規范中摘取出來的截圖,可以清晰的看到對AC耦合電容位置的準確描述!

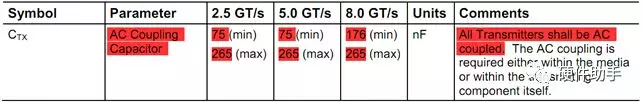

PCIe總線還規定了耦合電容的大小范圍,詳細參見規范中的表4-18,摘取如下:

PCIe協議規定的AC耦合電容規范

All platforms that have transmitters supporting 8.0 GT/s must implement the 176-265nF CTX value. Platforms operating at 2.5 or 5.0 GT/s only may implement over arange of 75 to 265 nF. (如果是PCIe 3.0則AC耦合電容必須選擇大一些!!!這就是為什么大部分時候我們看到參考設計中的AC耦合電容都選擇0.1uF,而有時候會遇到有的設計的耦合電容不是0.1uF,而是0.22uF之類的值,對此不要感到驚訝。)

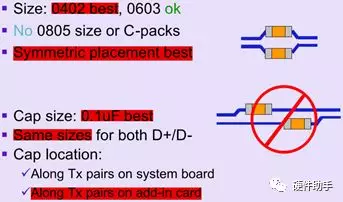

針對AC耦合電容,PCB布局布線一定要講求對稱!!!

2、高速信號調整

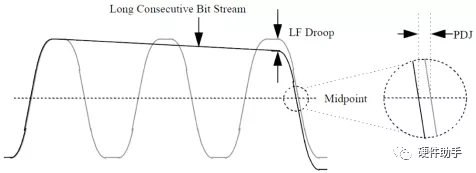

由于PCIe的速率越來越高,而普通的PCB板材和接插件對信號的傳輸損耗較嚴重,因此PCIe G1和G2在發送端都采用了去加重技術(De-emphasis),即發送端在發送信號時對跳變位之后的信號(代表信號中的低頻成分)減小幅度發送,這樣可以部分補償一下傳輸線路對高頻成分的衰減,從而得到比較好的眼圖(信號擺幅小,眼圖高度低,功耗小,EMC輻射小)。

PCIe G1中采用的是-3.5dB的去加重,G2中采用的是-3.5dB和-6dB的去加重。對于G3,由于信號速率更高,需要采用更加復雜的二階去加重技術,即除了跳變位減小幅度(De-emphasis)發送外,在跳變位的前一位也要增大幅度發送,這個增大的幅度通常叫做Preshoot。

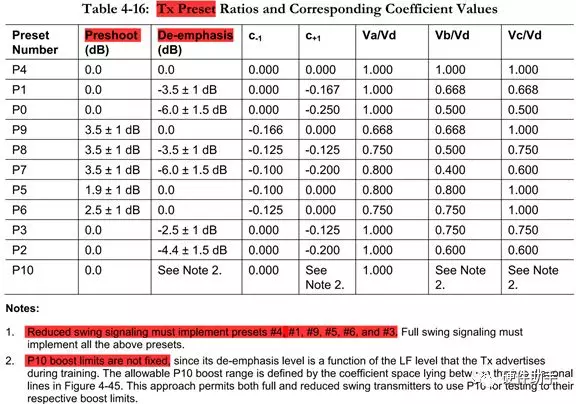

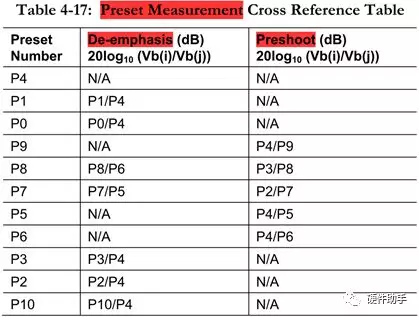

為了應對復雜的鏈路環境,PCIe G3中規定了共11種不同的Preshoot和De-emphasis的組合(Preset),實際應用中Tx和Rx端可以在Link Training階段協商出一個最優的Preset值。

PCIe G3除了在發送端對信號高頻進行補償,在接收端還要對信號做均衡(Equalization),就是在Rx端的接收芯片內增加一個均衡電路,可以抬高接收到的信號中的高頻分量,從而對線路的損耗進行進一步的補償。均衡器的強弱也有很多檔可選,在Link Training階段Tx和Rx端會協商出一個最佳的組合。

編輯:hfy

-

AC

+關注

關注

1文章

590瀏覽量

85044 -

PCIe

+關注

關注

16文章

1322瀏覽量

84670 -

耦合電容

+關注

關注

2文章

155瀏覽量

20210

發布評論請先 登錄

擴頻時鐘技術分享:SSC技術是什么、SSC對測試高速總線信號的影響

別忽視!高速電路可能毀于未優化的AC耦合電容

AC耦合電容的選取

完成閉環設計,基于仿真軟件的AC耦合電容阻抗優化

ViaExpert仿真AC耦合電容阻抗優化設計方案解析

PCIe總線AC耦合及高速信號調整技術

PCIe總線AC耦合及高速信號調整技術

評論