作者: Hello,Panda

一、寫在前面

FPGA 是可編程芯片,因此FPGA 的設(shè)計方法包括硬件設(shè)計和軟件設(shè)計兩部分。硬件包括 FPGA 芯片電路、存儲器、輸入輸出接口電路以及其他設(shè)備;軟件即是相應(yīng)的 HDL 程序以及最新非常流行的基于高層次綜合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。

(1)選擇FPGA(SoC)的若干理由

a)FPGA具有現(xiàn)場可編程能力,即使產(chǎn)品已經(jīng)投入市場,也可根據(jù)特殊應(yīng)用重新配置硬件;

b)FPGA具有強(qiáng)大的并行處理能力;

c)FPGA具有比ASIC設(shè)計更短的設(shè)計周期和更低設(shè)計成本;

d)FPGA比較易用;

e)隨著半導(dǎo)體技術(shù)的突飛猛進(jìn),F(xiàn)PGA 越來越成為一種融合處理、HBM存儲、接口于一體的超級芯片。

(2)設(shè)計提醒

強(qiáng)烈推薦FPGA設(shè)計遵循自頂向下的設(shè)計流程,也就是說從系統(tǒng)級設(shè)計開始,劃分為若干個二級單元,然后再把各個二級單元劃分為下一層次的基本單元,一直下去,直到能夠使用基本模塊或者IP 核直接實(shí)現(xiàn)為止。

需要特別提醒的是,大規(guī)模邏輯設(shè)計必須先有完整明確的需求和實(shí)現(xiàn)方案后再啟動硬件平臺和軟件設(shè)計。否則,任何一個小的改動都可能導(dǎo)致極大的糾正成本甚至整個系統(tǒng)全盤推翻重來。

二、設(shè)計小Tips

(1)明確FPGA設(shè)計需求

和所有的設(shè)計一樣,F(xiàn)PGA設(shè)計過程是一個迭代過程,首先是有一個系統(tǒng)的想法,然后將這一想法細(xì)化到具體交易中。

圖1 需求評估拓?fù)?/p>

(2)如何選型

FPGA的硬件設(shè)計選型主要考慮如下因素:

1)器件的供貨渠道和開發(fā)工具支持

2)器件的硬件資源

a)邏輯資源;

b) IO資源(FPGA負(fù)荷過重、發(fā)熱,影響速度、穩(wěn)定性和壽命);

c) 布線資源(影響速度);

d)DSP(乘法器、矢量浮點(diǎn)加速器)資源;

e)存儲器資源(內(nèi)部RAM塊和內(nèi)部和外部的DDR/SRAM)等;

f) 時鐘資源;

g) 串行收發(fā)器;

h) 硬核及集成塊。

3)器件的電氣接口特性

4) 器件的速度等級

5) 器件的封裝和價格等

(3)嵌入式設(shè)計流程

圖2 設(shè)計流程

這個流程看上去有點(diǎn)像操作系統(tǒng)的層次結(jié)構(gòu),硬件就是FPGA邏輯和底層單元;中間件就是平臺相關(guān)的可以重復(fù)利用的標(biāo)準(zhǔn)協(xié)議和接口;應(yīng)用層執(zhí)行產(chǎn)品的核心功能。這三個層級是向下驗(yàn)證的,最后實(shí)現(xiàn)系統(tǒng)的集成和驗(yàn)證。

更為具體的,針對某種器件,嵌入式工程師的主要工作如下:

圖3 設(shè)計內(nèi)容

三、FPGA的幾種典型應(yīng)用

a)運(yùn)動控制。需要高性能的工業(yè)設(shè)計領(lǐng)域;

b)電視廣播。SDI接口已經(jīng)圖像流的優(yōu)化重構(gòu)和壓縮;

c)通信領(lǐng)域。處理通信過程中的海量并行數(shù)據(jù)流;

d)汽車輔助駕駛。屬于對圖像處理、圖形、控制的集大成應(yīng)用;

e)高性能計算。數(shù)據(jù)庫、金融市場加速、地震和醫(yī)學(xué)成像、矩陣數(shù)學(xué)、AI、云計算、機(jī)器學(xué)習(xí)應(yīng)用等;

f)高端服務(wù)器;

g)IO和總線擴(kuò)展、橋接。

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,器件的集成度越來越高,集成的硬核和功能塊也越來越豐富。FPGA各廠商面向不同層次的應(yīng)用也在不斷的拓展,F(xiàn)PGA必將褪下它貴族的臉孔走入尋常百姓家。

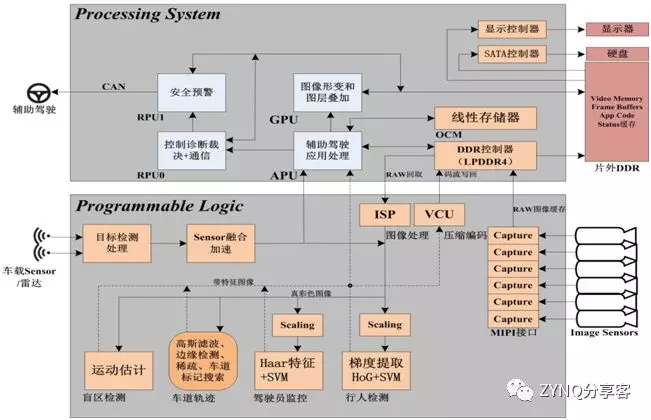

圖4 ADAS應(yīng)用

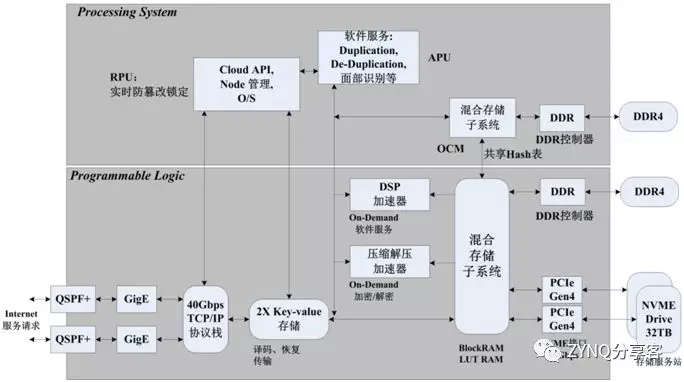

圖5 云計算應(yīng)用

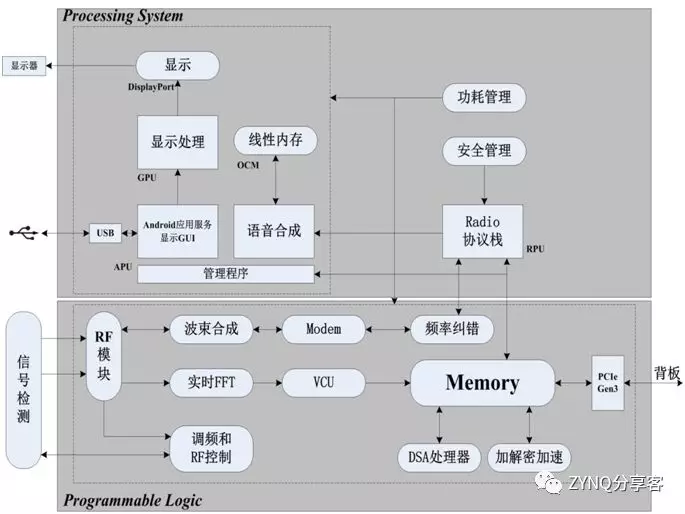

圖6 無線通信系統(tǒng)

圖7 控制系統(tǒng)與4G/5G通信

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614044 -

存儲器

+關(guān)注

關(guān)注

38文章

7634瀏覽量

166399

發(fā)布評論請先 登錄

國產(chǎn)FPGA往事

FPGA是什么?應(yīng)用領(lǐng)域、差分晶振作用及常用頻率全面解析

fpga和cpu的區(qū)別 芯片是gpu還是CPU

大多數(shù)FPGA的程序存儲器(FLASH)為什么都放在外面呢?FPGA的主要應(yīng)用

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

玩轉(zhuǎn)FPGA必備的基礎(chǔ)知識

FPGA復(fù)位的8種技巧

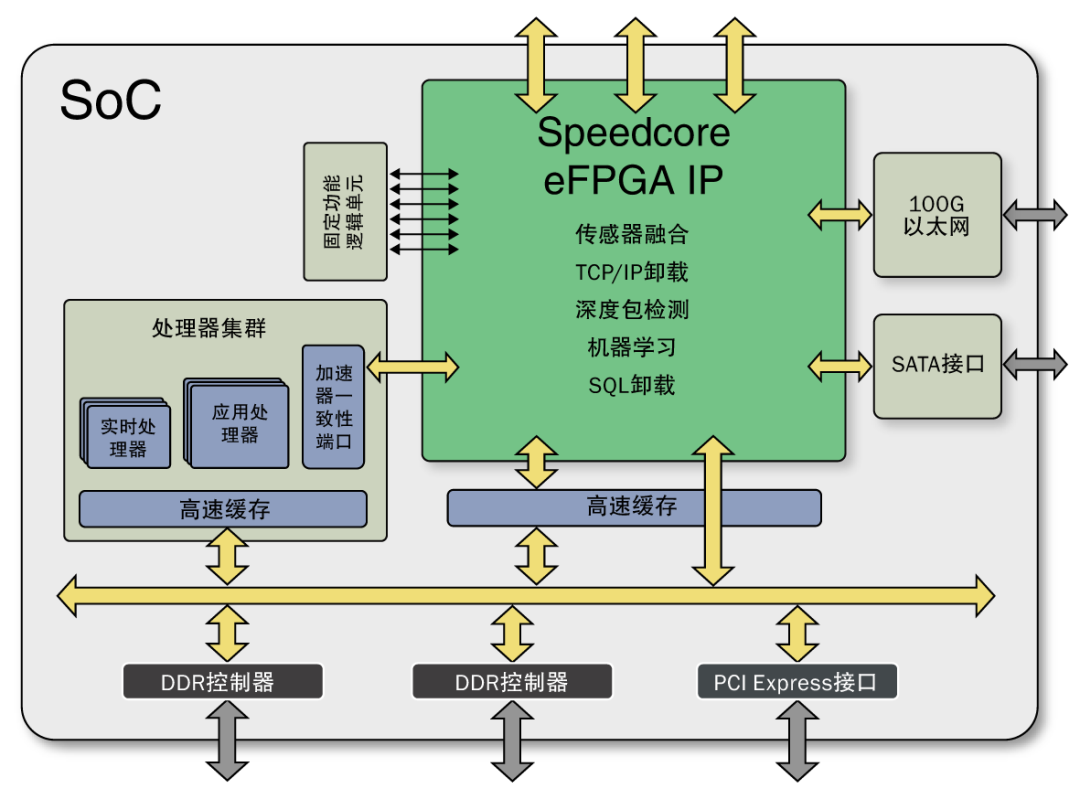

Achronix Speedcore eFPGA的特性和功能

FPGA基礎(chǔ)知識及設(shè)計和執(zhí)行FPGA應(yīng)用所需的工具

詳解FPGA的基本結(jié)構(gòu)

FPGA與ASIC的優(yōu)缺點(diǎn)比較

基于FPGA的CCD工業(yè)相機(jī)系統(tǒng)設(shè)計

中科億海微FPGA+ARM核心板在自動噴漆設(shè)備中的應(yīng)用

FPGA的幾種典型應(yīng)用 基于FPGA的小Tips設(shè)計

FPGA的幾種典型應(yīng)用 基于FPGA的小Tips設(shè)計

評論