作者:Wilson Qiu,Xilinx工程師

常用外設設計

ZYNQ學習過程中一個重要環節是進行調試,當然在SDK中進行調試時,設置斷點進行單步調試非常高效。但是ZYNQ中畢竟涉及到FPGA的硬件部分,于是如果可以通過UART與ZYNQ器件進行雙向的通信會使得調試非常方便。

Step1: 確認ZYBO板上硬件連接。

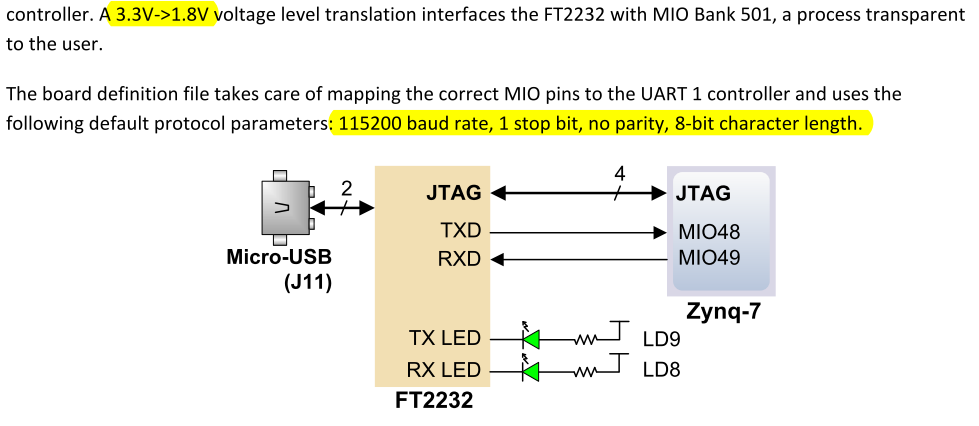

在ZYBO的用戶手冊中有以下描述,如圖 21所示。

圖 21

其ZYBO開發板的原理圖也可知MIO Bank的電壓為1.8V。

于是可以得到以下幾點:

1. 硬件上連接串口的IO為MIO48和MIO49。

2. IO的電壓為1.8V。

3. 默認使用的參數為:115200波特率以及其他對應參數,見圖 21。

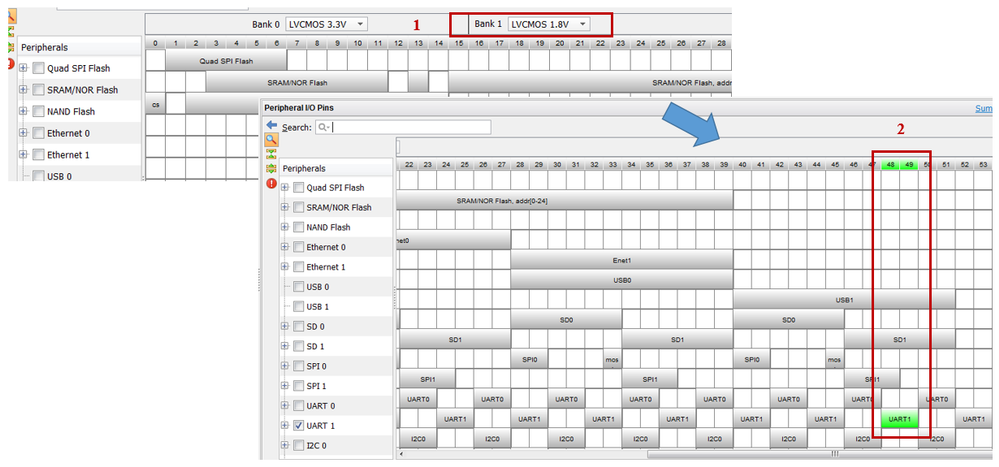

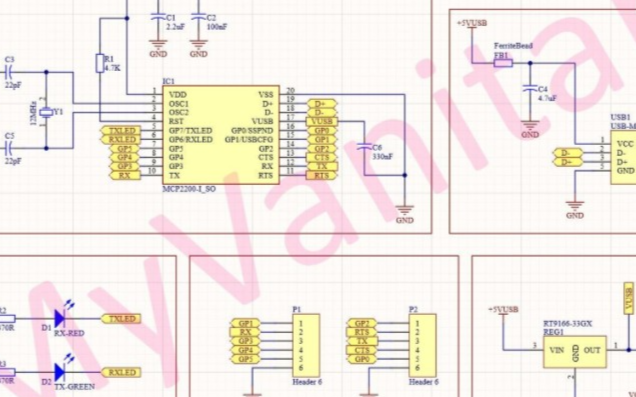

Step2: 在Vivado的Block Design中配置ZYNQ7 Processing System時,需要配置UART外設,如圖 22所示。

圖 22

Step3: 按照“Vivado中進行ZYNQ硬件部分設計”中介紹的,直到在SDK中編寫C代碼步驟。需要使用UART進行通行,分為通過UART向外發送數據和通過UART接收數據。

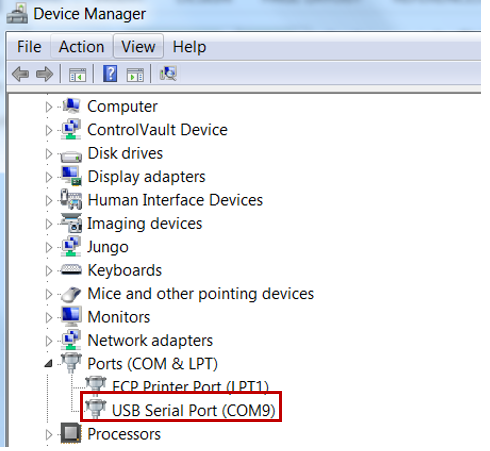

Step4: PC上安裝串口調試助手,硬件上連接串口線到PC。向ZYNQ中下載硬件配置后,在Windows Device Manager查看UART所使用的端口,如圖 23所示。

圖 23

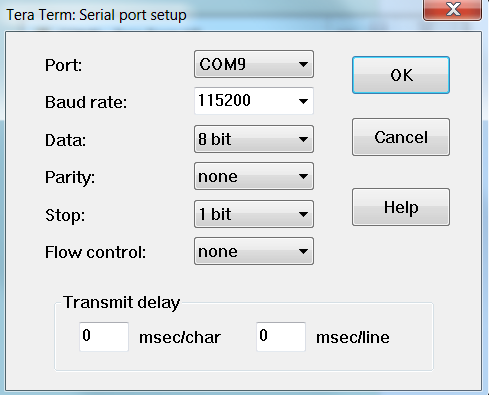

并將串口調試助手設置成相應的配置,如圖 24所示。

圖 24

Step5: 至此就可以在C代碼中發送或者讀取數據了,下面給出一段示例代碼。

圖 25

程序首先運行,輸出” Please enter any number from 0~9”。此后會停在等待輸入處,直到通過串口助手鍵入了數字之后,才會跳到下一行代碼,并將鍵入的數字輸出在串口調試助手中。

圖 26

至此可以通過串口輸出各種信息(因為可以輸出字符串),同時也可以通過串口輸入進行菜單選擇,因為雖然不能接收字符串,但可以鍵入10個數字以及26個英文字母,這也應該足夠了。

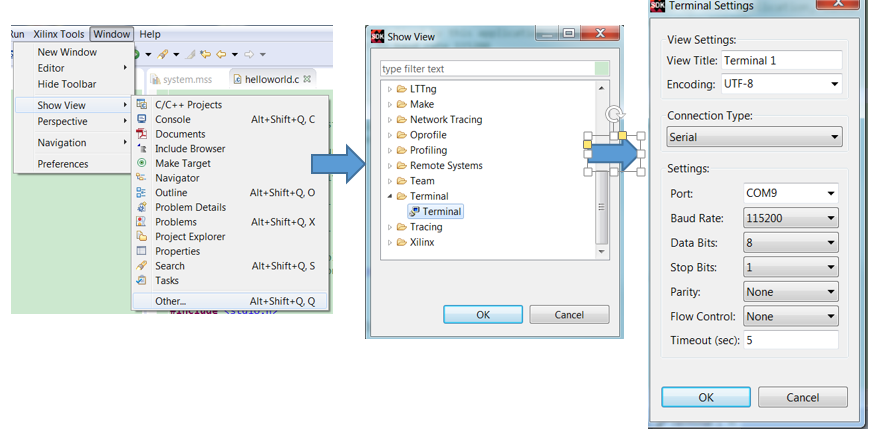

Step6: 除了使用外部的串口調試助手外,SDK內部也提供了Terminal工具。通過如下圖所示的方式顯示Terminal窗口且進行配置,同樣可以當作串口調試助手使用,如圖 28所示。

圖 27

圖 28

將用戶邏輯設計封裝成IP

參考工程見“ZYBO_demo_packageIP.xpr”。

ZYNQ中PS與PL的聯系主要有兩個,分別是GP端口和HP端口。其中HP端口可以理解為PS和PL可以訪問同一片存儲空間,于是可以以DDR空間為中介,進行大量的數據通信。而平時在純FPGA設計中的那些邏輯模塊與PS的通信方式就是依靠GP端口完成的。

純RTL邏輯模塊的控制或者輸出都是通過模塊的輸入輸出端口實現的。在ZYNQ的架構下,就是將這些輸入輸出端口改為寄存器,原來的輸入端口改為只寫的控制寄存器;原來的輸出端口改為只讀的狀態寄存器。于是每個邏輯模塊都有一個標準的AXI-Lite Slave接口,用于與PS相連接,使得PS可以控制讀寫邏輯模塊內的寄存器。于是每一個邏輯模塊就相當于PS的一個外設,與PS自帶的外設,如UART、I2C控制器控制器來是一樣的。這就是ZYNQ的硬件可擴展性,通俗的說就是當ARM需要各種要求的外設時,都可以通過在PL端進行邏輯設計實現。

下面就介紹如何一步一步的完成一個PL端的邏輯設計,并將其封裝成為IP,并在ZYNQ的Block Design中加入到硬件設計中,并在SDK中通過代碼來控制該外設。

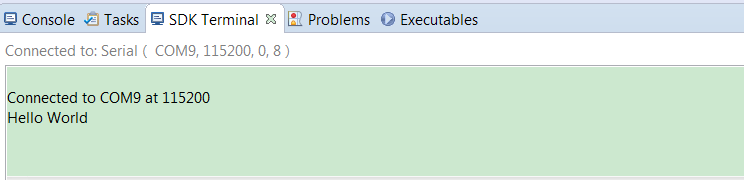

本例中所涉及的邏輯模塊功能為:IP的外部接口為4盞LED,內部寄存器有3個,分別是工作模式寄存器(MODE),使能寄存器(ENABLE)和狀態寄存器(STATUS),如圖 29所示。

圖 29

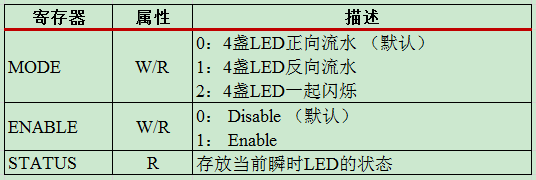

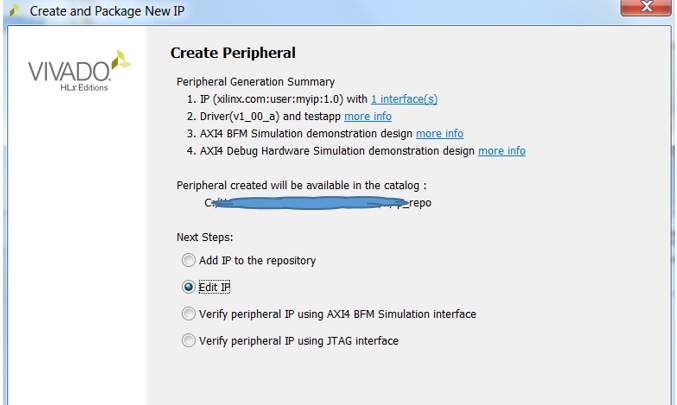

Step1: 在Vivado GUI中,選擇Tool?Create and Package New IP…。一般情況下,選擇“Create a new AXI4 Peripheral”,這種IP就是之前提到的,由PS讀寫寄存器進而控制的IP,在后面的菜單中選擇該IP的Interface接口以及內部需要多少寄存器,如圖 30所示。

圖 30

一般來說,IP首先需要一個AXI-Lite的Slave接口,用于與PS連接。除此以外還可以增加其他AXI接口,例如增加一個AXI4的Master接口,用于邏輯設計中訪問PS端的存儲器;又比如可以增加一個AXI-Lite的Master,用于讀寫其他邏輯模塊的寄存器等等。在這里選擇好接口后,工具在生成IP的時候會自動生成相應的AXI接口代碼,用戶可以直接使用或者稍作修改即可。

另外就是選擇寄存器的個數,因為稍后生成的代碼中會自動完成指定數量寄存器的讀寫控制代碼,于是如果設置少了,后面需要手工添加代碼,會比較麻煩,不如配置時將寄存器個數設置的多一些。

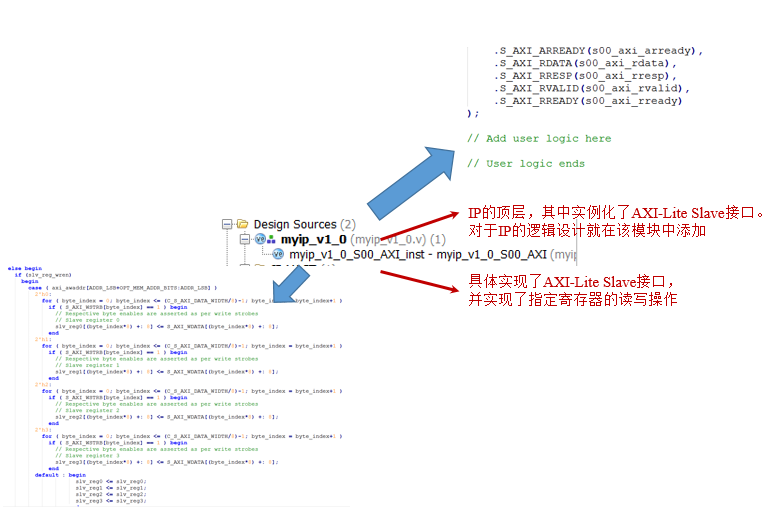

Step2: 完成配置后工具自動生成代碼,在生成的代碼中進行修改。

圖 31

在自動生成的代碼中,結構如下:

圖 32

需要注意的是自動生成的代碼只是簡單完成了指定數量寄存器的讀寫時序,至于每個寄存器的邏輯功能和含義是沒有的,需要用戶將這些寄存器引到S00_AXI模塊的上層,與用戶設計的邏輯進行通信。同時自動生成的代碼中所有的寄存器都是可讀可寫的,如果需要設置只讀或者只寫的寄存器,需要在S00_AXI模塊中自行修改代碼。

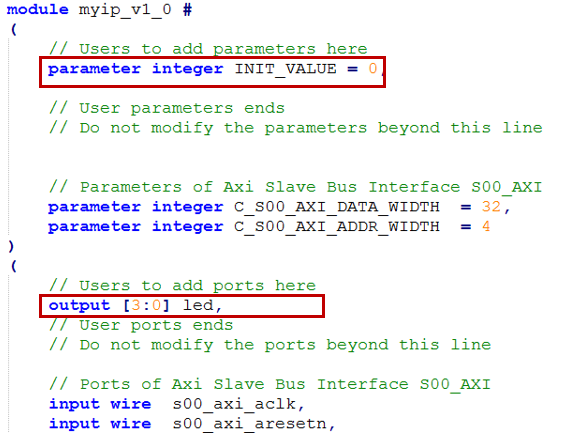

Step3: 為邏輯設計增加外部接口以及全局參數。

該例程中需要設置4個外部輸出管腳,控制外部LED。并且設置一個全局參數為4盞LED的初始狀態。首先在代碼中指定位置進行修改,如圖 33所示。

圖 33

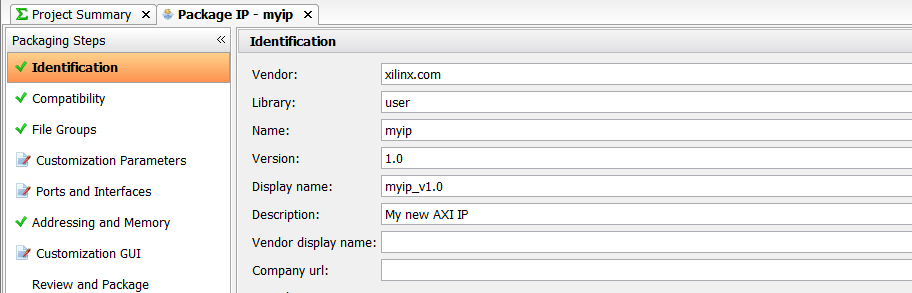

保存修改后,會在GUI界面中看到“Customization Parameter”、“Ports and Interfaces”以及“Customization GUI”的標識都變了,代表檢測到了代碼中的變化。

圖 34

點擊GUI中如下所示的指令后,工具自動完成更新。

圖 35

Step4: 在GUI如圖 34所示的界面中修改參數設置,對IP進行配置。

Step5: 完成IP的封裝,如圖 36所示,在Review and Package中點擊Re-Package IP。

圖 36

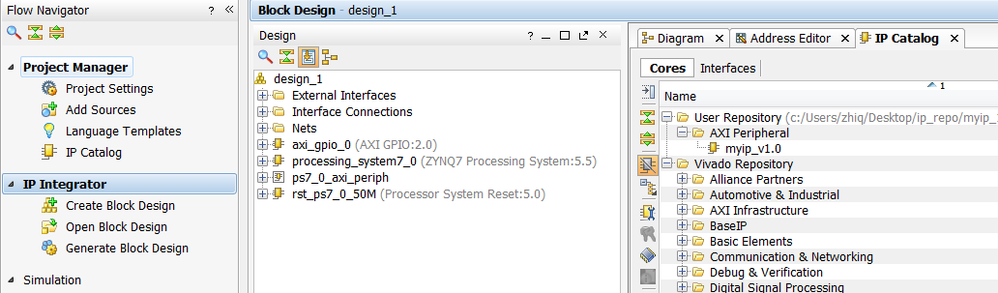

此時會關閉IP封裝界面,回到ZYNQ Block Design界面。在IP Catalog中會出現剛才封裝完成的IP。

圖 37

此后的操作就和“Vivado中進行ZYNQ硬件部分設計”中介紹的一樣,將該IP當成與其他IP一樣的外設,進行Block Design設計,同樣需要對于外接接口添加約束文件,之后生成Bit文件。

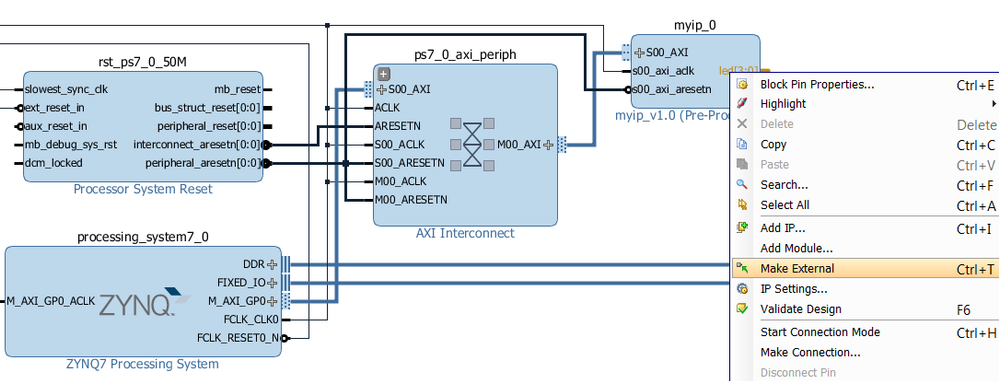

Step6: 在Block Design中需要將封裝的邏輯模塊IP需要引到外部的IO進行設置。

右擊需要引出的端口,點擊“Make External”。之后重新生成HDL Wrapper即可。

圖 38

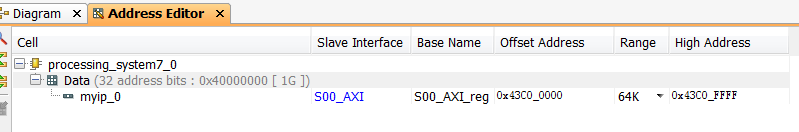

Step7: 在Block Design中的Address Editor中給IP分配總線地址。

圖 39

Step8: 封裝好的IP進行底層修改。

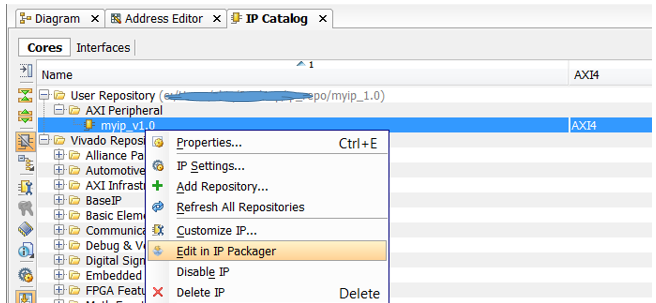

如果需要對已經設計好的IP進行底層修改,就在IP Catalog中顯示的該IP處右擊,選擇“Customize IP”。需要注意的是,工具會默認彈出一個路徑,作為修改IP的工作路徑,但是該路徑是一個臨時路徑,與之前存放IP的路徑不同。

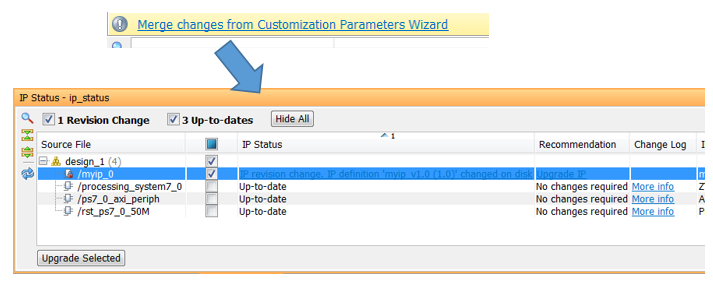

圖 40

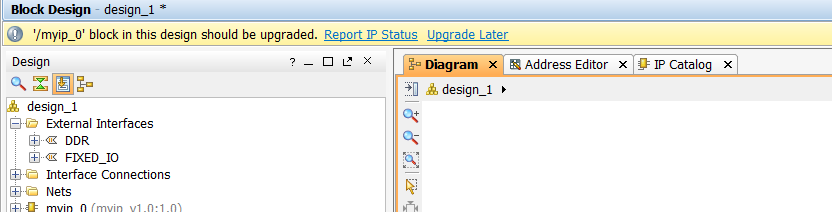

IP底層修改完成之后,重新Re-Package IP后,回到Block Design中工具自動檢測到IP有更新,只要通過工具的提示進行IP的更新即可。

圖 41

Step9: 封裝好的IP的BSP以及SDK程序的編寫。

首先封裝的IP有自己在AXI總線上的地址,于是IP內部的所有寄存器的地址就是IP的Base地址加上各個寄存器的偏移量。于是在SDK代碼中就可以通過唯一的地址訪問到這些寄存器。由于內部的寄存器都是用戶自己設計的,所以不需要BSP封裝太多的函數,BSP也無法知道用戶設計的邏輯,從而也無法自動封裝API。用戶直接通過底層調用Xil_Out32()和Xil_In32()完成對于封裝邏輯模塊IP的控制。如果需要,用戶可以自行封裝更上層的API函數。

使用Zynq processor仿真Customized IP

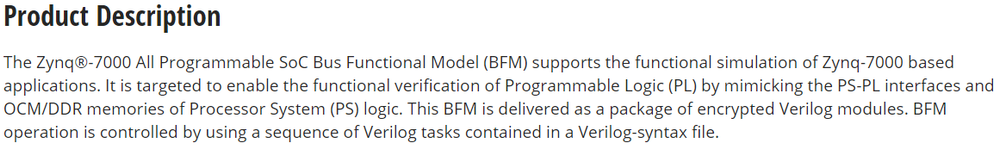

由于ZYNQ中除了常用的FPGA邏輯部分外還有ARM內核部分,所以在進行類似于FPGA設計仿真時會遇到問題,就是如果仿真ARM內核部分。Xilinx提供的一個方案是Zynq BFM(Bus Functional Model),其介紹如下。

圖 42

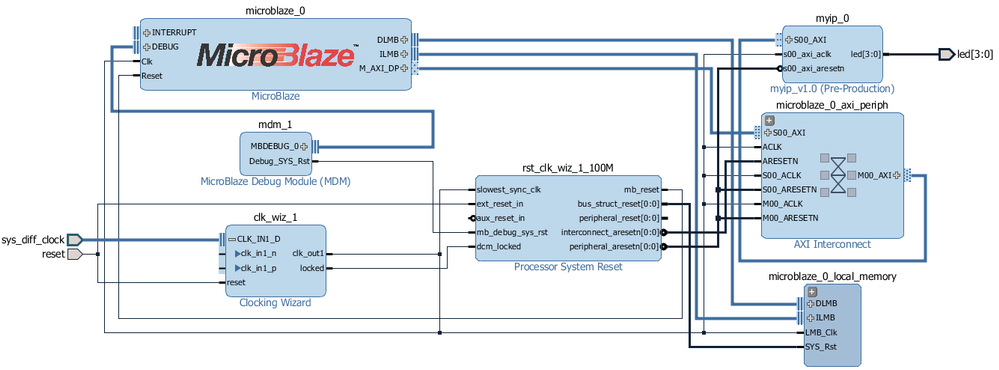

但是該Model是需要額外購買的,該章節介紹一種無需購買Zynq BFM就可以仿真Customized IP的方法。基本思路是對于PL端的Customized IP而言,控制端是ZYNQ中的ARM內核還是普通FPGA中的MicroBlaze都是一樣的,所以可以將Customized IP例化到以MicroBlaze為處理器的Block Design中,由于MicroBlaze的仿真無需額外的License,所以可以將SDK的程序導入到MicroBlaze的內核,進而仿真Customized IP。

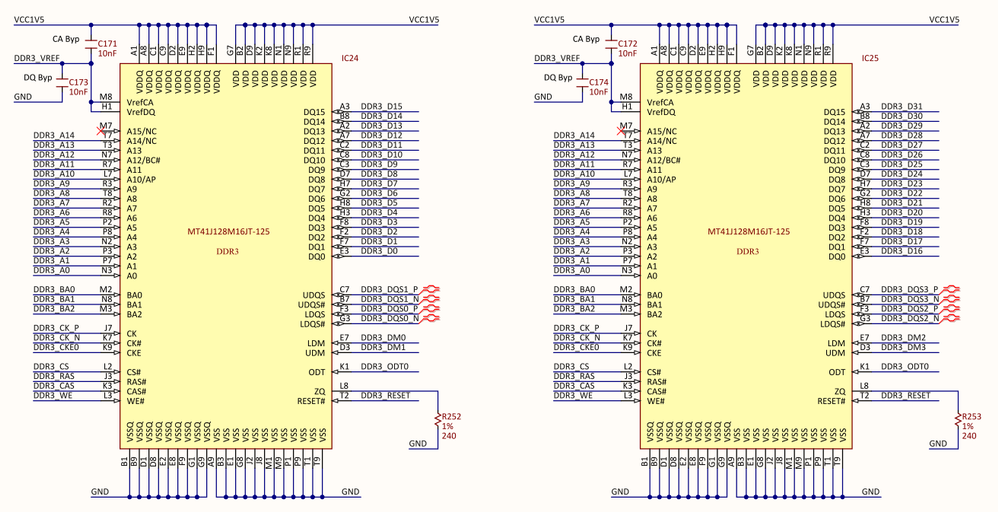

Step1: 按照“將用戶邏輯設計封裝成IP”中介紹的,完成Customized IP的設計和封裝;在Block Design中加入MicroBlaze和Customized IP,完成Block Design設計;完成硬件平臺的綜合、實現、生成Bit文件,并導入SDK;在SDK中完成軟件設計。綜上就是完成“將用戶邏輯設計封裝成IP”中的Step9,區別只是用MicroBlaze替代了ZYNQ Processing System。

圖 43

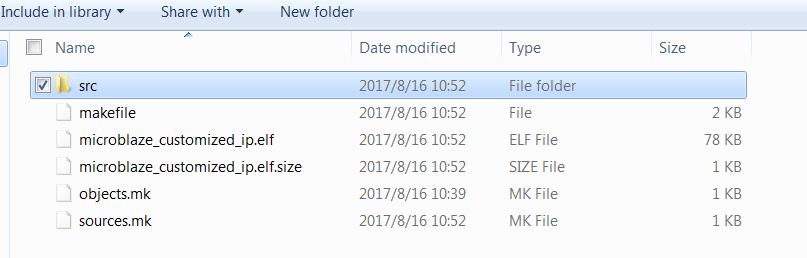

Step2:對SDK中設計的軟件程序完成編譯,工具自動生成elf文件。默認的存放地址為SDK project下Src文件夾中。例如:C:/***/A7_microblaze/A7_microblaze.sdk/microblaze_customized_ip/Debug

圖 44

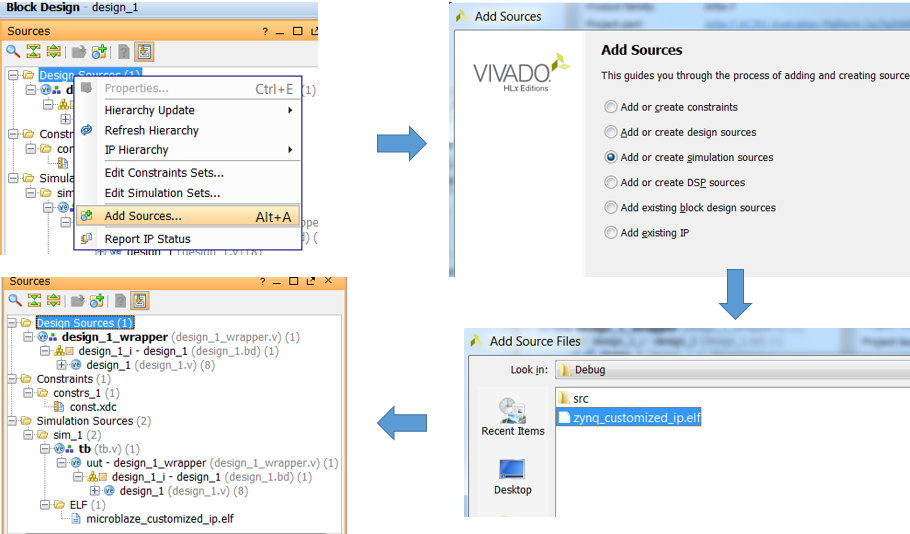

Step3:回到Vivado開發平臺,將elf文件導入至Simulation Source中。

圖 45

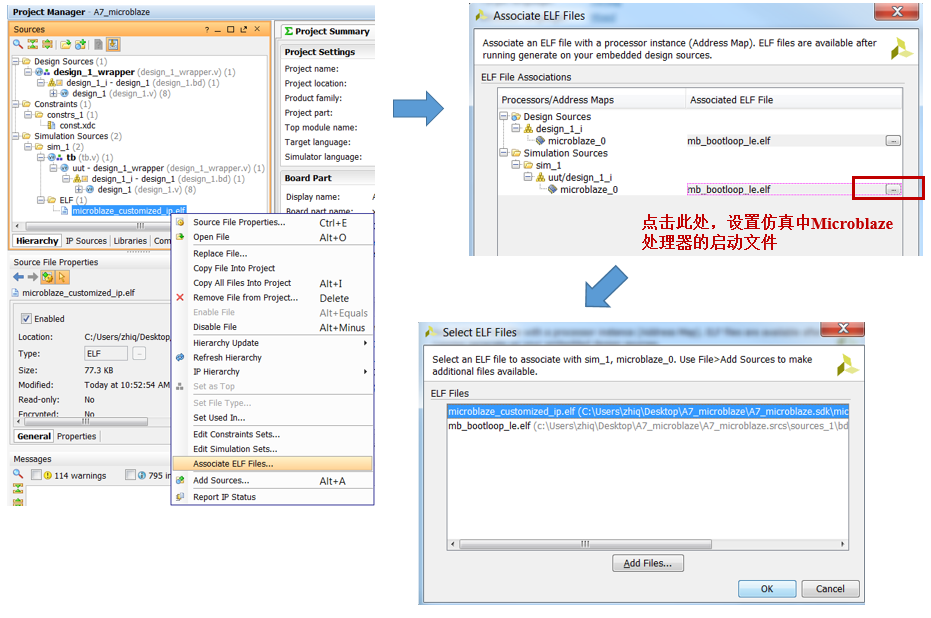

Step4:將導入的elf文件鏈接到對應的處理器,使其作為該處理器的啟動程序。注意,elf文件只允許associate至Microblaze,工具不支持鏈接到ZYNQ。

圖 46

Step5:正常啟動仿真。

可以看到MicroBlaze核發出的AXI通信協議,如圖 47所示。

圖 47

于是對應的IP的輸出可以看到如“將用戶邏輯設計封裝成IP”中模式2設計的一樣,輸出的4路LED不斷反轉。

圖 48

編輯:hfy

-

uart

+關注

關注

22文章

1267瀏覽量

103239 -

Zynq

+關注

關注

10文章

614瀏覽量

48015

發布評論請先 登錄

ZYNQ常用外設設計:malloc與memcpy的使用方法

uart通信的詳細講解

入門Zybo和linuX資料分享

分享一篇關于衛星通信中星地鏈路特性的模擬系統設計方案

單片機uart串口通信程序

ch582m低功耗藍牙一個中心設備怎么自動匹配到附近的外設設備?

基于Verilog的UART串行通信接口電路設計

基于FTDI芯片進行USB到UART的轉換設計方案實現

UART串口通信協議是什么?

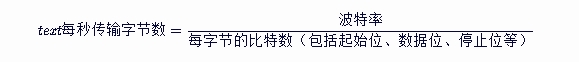

uart波特率和傳輸頻率的關系 UART串口的常用波特率為多少

TI mmWave Radar sensor硬件外設設計參考

使用UART與ZYBO進行通信常用外設設計方案

使用UART與ZYBO進行通信常用外設設計方案

評論