要想理解和管理FPGA設(shè)計師如何在設(shè)計周期早期在FPGA上實現(xiàn)高處理狀態(tài)和低處理狀態(tài)之間的轉(zhuǎn)換,將顯著影響電源設(shè)計師優(yōu)化電源設(shè)計和滿足系統(tǒng)功耗要求的可選方法。FPGA中的每個電源軌沒有要求也沒有必要采用獨(dú)立的電源,因為這樣會增加成本,占用太多寶貴的電路板空間。相反,電源設(shè)計師可以使用分布式電源網(wǎng)絡(luò),由降壓穩(wěn)壓器將系統(tǒng)電源降下來,然后分配給各個負(fù)載點(diǎn)穩(wěn)壓器再提供每個電壓軌。每個穩(wěn)壓器設(shè)計提供恒定的輸出電壓,只要確保輸入電壓和輸出負(fù)載電流在設(shè)計范圍內(nèi)。

如果設(shè)計師可以在開發(fā)過程早期就滿足基于FPGA的設(shè)計,提出的功耗要求和約束條件,那么在系統(tǒng)的最終實現(xiàn)階段就能形成極具競爭力的優(yōu)勢。然而,根據(jù)整個技術(shù)文獻(xiàn)中這種自我暗示式的反復(fù)禱告,今天基于FPGA的系統(tǒng)中還有什么會使得完全遵循這個建議變得不切實際或過于困難呢?盡管能夠使用各種開發(fā)工具,如專門針對FPGA項目開發(fā)的早期功耗預(yù)估器和功耗分析器,但對電源設(shè)計師來說,在設(shè)計過程早期就考慮最壞情況而不是最佳情況的電源系統(tǒng)是有好處的,因為在許多方面仍有太多的不確定性,比如在硬件設(shè)計完成和功耗可以測量之前,靜態(tài)小電流狀態(tài)與全速工作狀態(tài)之間的動態(tài)負(fù)載要求將如何波動。

采用并行工程(CE)技術(shù),可以為在項目中使用FPGA器件的開發(fā)團(tuán)隊,提供一種快速方便地在當(dāng)前設(shè)計的處理性能、材料清單(BOM)成本和效率之間尋找和實現(xiàn)最有效平衡的方法嗎?理解并行工程如何影響一個團(tuán)隊的設(shè)計工作,以及它如何影響開發(fā)團(tuán)隊從項目一開始就解決FPGA及系統(tǒng)其余部分的電源要求的能力,都有助于回答這個問題(參考副標(biāo)題“并行工程”)。

并行工程,是一種有助于設(shè)計團(tuán)隊更加快速地發(fā)現(xiàn)和解決一起協(xié)作產(chǎn)生最終設(shè)計的各門科目之間假設(shè)脫節(jié)問題的機(jī)制。任何開發(fā)團(tuán)隊在設(shè)計開始就完全正確地獲得一個復(fù)雜系統(tǒng)的全部要求基本上是不可能的——因此盡可能早地發(fā)現(xiàn)、判斷和放棄假設(shè)與設(shè)計決策的脫節(jié)、并用能夠以可能最低的成本指導(dǎo)項目更接近理想結(jié)果的條件與決策來代替是更加高效的一種方法。

后期設(shè)計階段和最壞情況下,F(xiàn)PGA電源系統(tǒng)設(shè)計的復(fù)雜性和潛在后果足以證明采用并行工程方法的合理性嗎?為了回答這個問題,我們需要理解:FPGA電源系統(tǒng)設(shè)計師面臨的設(shè)計復(fù)雜性和不確定性根源是什么,這些原因如何影響他們在設(shè)計電源時必須做出的權(quán)衡決策?

復(fù)雜性和不確定性

設(shè)計團(tuán)隊中的每位成員都在經(jīng)歷復(fù)雜性和不確定性的增加——幸運(yùn)的是,提高集成度和抽象水平多少可以降低一些復(fù)雜性和不確定性,并有助于將整體復(fù)雜性保持在人類設(shè)計師能夠理解和應(yīng)付的范圍內(nèi)。正如任何會在設(shè)計后期增加其影響力的科目一樣,上游設(shè)計假設(shè)與決策可能會形成額外的復(fù)雜性與不確定性來源,如果能夠較早地協(xié)調(diào)與交流,可以最大程度地減小這些復(fù)雜性與不確定性。

電源設(shè)計是在復(fù)雜性日益增加的系統(tǒng)中這些潛在的下游科目之一。在本例中,讓我們從電源設(shè)計師的角度看一下復(fù)雜性和不確定性的來源。影響電源設(shè)計的兩個關(guān)鍵FPGA因素是電壓和電流要求。

FPGA電壓要求趨勢正在推升復(fù)雜性,因為它們要求日益增多的電源軌。今天的高端FPGA不再只是需要兩個電源軌用于內(nèi)核和I/O單元以及可能第三個電源軌用于輔助功能,而是要求十個以上的外部驅(qū)動電源軌。

為什么需要的電源軌數(shù)量增加得如此顯著呢?SRAM單元可能要求比內(nèi)部邏輯門稍微高一點(diǎn)的電壓,以確保可靠的全速工作,同時還需較低的電壓用于待機(jī)模式。工業(yè)標(biāo)準(zhǔn)會防止不同的I/O單元共享相同的電源軌,從而增加所需的電源軌數(shù)量,因為它們可能將不同的I/O單元和物理收發(fā)接口鎖定到具有不同電源噪聲極限和電壓值的不同電源。舉例來說,以太網(wǎng)工作時的I/O電壓可能不同于I2C總線。一種是板上總線,另一種是外部總線,但兩者都可以用FPGA實現(xiàn)。減少抖動或提高敏感電路(如低噪聲放大器、鎖相環(huán)、收發(fā)器和精密模擬電路)的噪聲余量,也可能增加對更多電源軌的需求,因為它們無法與較高噪聲元件共享相同的電源軌,即使它們工作在相同的電壓。

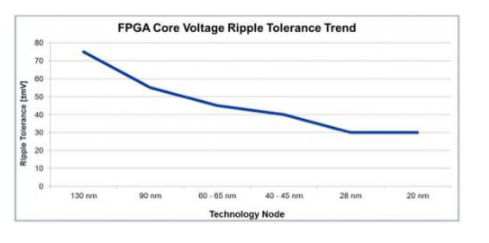

除了要求日益增多的電源軌外,當(dāng)前FPGA的工作電壓也要比以前的FPGA低,因為這有助于降低功耗,提高集成度,但也增加了復(fù)雜性,因為電源必須能夠保持越來越嚴(yán)格的電壓容差要求(見圖1)。舉個例子,自從用130nm工藝生產(chǎn)FPGA以來,基于28nm技術(shù)節(jié)點(diǎn)的FPGA的內(nèi)核電壓紋波容差的公開幅度已經(jīng)降低了一半還多。誤差預(yù)算百分比已經(jīng)從5%下降到3%,并正在向2%邁進(jìn)。保持電壓容差要求與理解并滿足FPGA電流要求有關(guān)。

經(jīng)過4代工藝技術(shù)節(jié)點(diǎn)的發(fā)展,平均電壓紋波容差下降了一半還多,對電源設(shè)計師來說這就是增加復(fù)雜性的原因。

FPGA電流特征趨勢正在推動復(fù)雜性的提高,因為FPGA中更高的密度和包含的外設(shè)/功能/IP模塊的數(shù)量正在呈摩爾定律增長——每兩代工藝節(jié)點(diǎn)相比,相同面積的硅片所容納的模塊數(shù)量基本要翻倍。雖然提供給FPGA的電壓是固定的,但每個電壓的工作電流不是固定的,會根據(jù)FPGA邏輯的實現(xiàn)方法變化而發(fā)生波動。

當(dāng)內(nèi)部邏輯門塊或I/O單元在高利用率和低利用率之間轉(zhuǎn)換時,電流波動異常劇烈。隨著FPGA切換到更高的處理速率,消耗電流將增加,電壓將趨于下降。一個好的電源設(shè)計要防止壓降超過電壓瞬時門限。同樣,當(dāng)FPGA切換到較低處理速率時,電流消耗將下降,電壓將趨于提高,電源設(shè)計應(yīng)防止其超過相應(yīng)的門限。總之,可能會實質(zhì)影響電源設(shè)計的大量不確定性源自FPGA設(shè)計師如何在FPGA上實現(xiàn)系統(tǒng)。

這類不確定性特別影響FPGA系統(tǒng),部分原因是因為使用FPGA的關(guān)鍵特性之一是,設(shè)計師可以創(chuàng)建任何大小的處理資源和任意數(shù)量的冗余處理資源,以便與軟件可編程處理器相比能用較短的時間和/或較低的功耗解決他們的問題。因此,雖然軟件可編程處理器擁有可以同時操作的有限處理資源,但FPGA提供了創(chuàng)建專門的、最優(yōu)的和定制的處理資源的機(jī)會,不過要求定制的電源設(shè)計。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618423

發(fā)布評論請先 登錄

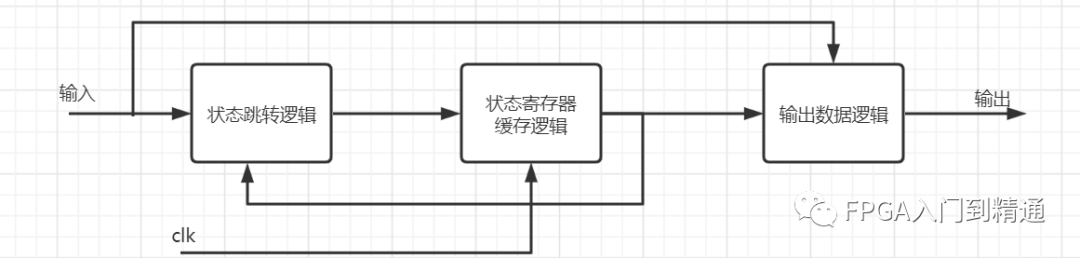

FPGA工程師:如何在FPGA中實現(xiàn)狀態(tài)機(jī)?

【FPGA干貨分享六】基于FPGA協(xié)處理器的算法加速的實現(xiàn)

FPGA電源設(shè)計適合并行工程嗎?

利用FPGA怎么實現(xiàn)數(shù)字信號處理?

在FPGA電源設(shè)計中并行工程是否適用?

在Spark Streaming中實現(xiàn)快速狀態(tài)流處理

基于DSP+FPGA的并行信號處理模塊設(shè)計

詳細(xì)介紹FPGA狀態(tài)機(jī)的設(shè)計和應(yīng)用

如何在FPGA中實現(xiàn)狀態(tài)機(jī)

基于FPGA的狀態(tài)機(jī)設(shè)計

并行工程(CE)技術(shù)能否實現(xiàn)FPGA高處理狀態(tài)和低處理狀態(tài)轉(zhuǎn)換

并行工程(CE)技術(shù)能否實現(xiàn)FPGA高處理狀態(tài)和低處理狀態(tài)轉(zhuǎn)換

評論