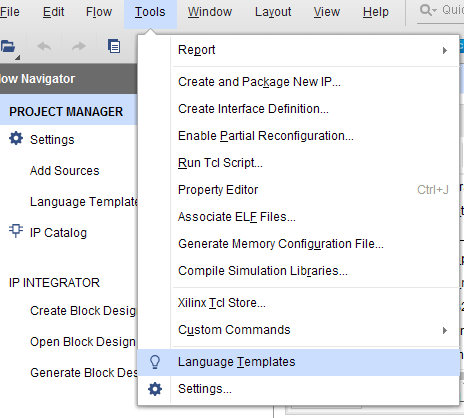

首先,什么是XPM?可能很多人沒聽過也沒用過,它的全稱是Xilinx Parameterized Macros,也就是Xilinx的參數(shù)化的宏,跟原語的例化和使用方式一樣。可以在Vivado中的Tools- > Language Templates中查看都有哪些XPM可以例化。

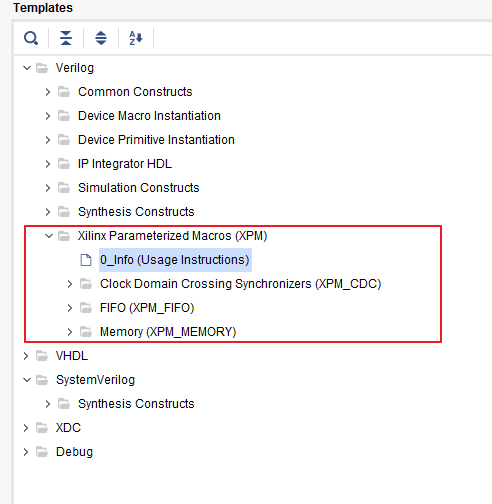

從上圖中可以看出,目前可以例化的XPM主要有三種:跨時鐘域處理、FIFO和MEMORY。

我們以MEMORY為例,在Vivado中可以通過下面四種方式調(diào)用FPGA中的存儲單元,均可以選擇是Block RAM還是Distributed RAM.

1. RTL代碼

我們在定義一個memory變量后,可以在前面指定其資源類型:

(* ram_style = "block" *)reg [3:0] mem_bram [15:0] ; (* ram_style = "distributed" *)reg [3:0] mem_dram [15:0] ;

使用RTL代碼的方式非常靈活,但由于少了很多的控制項,綜合后的結(jié)果可能不是最優(yōu)的。

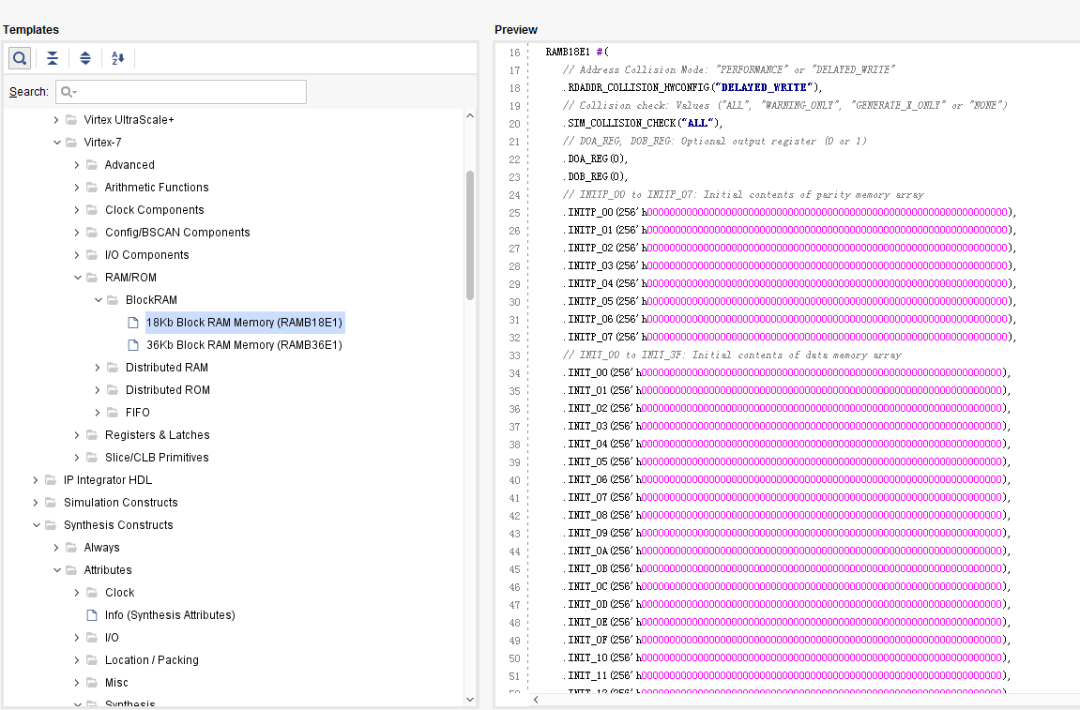

2. 原語(Primitive)

使用原語也可以例化MEMORY,但沒見幾個工程師這么用過,因為接口實在太多了,所以實用性不高。

3. IP Core

這種方式應(yīng)該是使用最多的,但缺點也很明顯:

當(dāng)修改參數(shù)時需要重新打開IP,然后Generate;

不同版本的Vivado之間還需要進行Update;

有時沒注意到IP中的參數(shù),導(dǎo)致結(jié)果并不是自己想要的;

最近在調(diào)試中就碰到這樣一個問題,F(xiàn)IFO中的默認(rèn)輸出延遲是1,即輸出數(shù)據(jù)比讀使能晚一拍,而且Output Registers默認(rèn)是不勾選的。但這個選項不知道什么時候被改了,導(dǎo)致程序最終的輸出結(jié)果一直有問題,在debug時一直檢查的是RTL代碼,直到定位到FIFO模塊時才發(fā)現(xiàn)了這個問題。如果此時我們使用的是XPM,那從代碼中很容易就能看出來

錯誤。

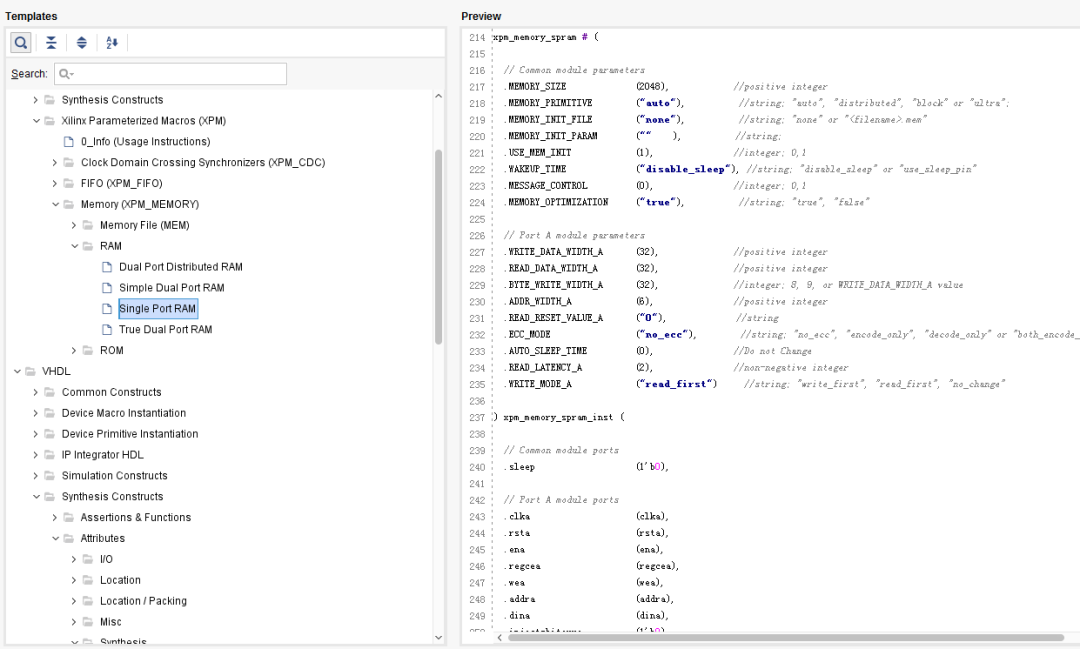

4. XPM_MEMORY

相對而言,XPM的缺點就不是很明顯,純代碼例化的方式更加靈活、簡單。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614038 -

Xilinx

+關(guān)注

關(guān)注

73文章

2182瀏覽量

124336 -

XPM

+關(guān)注

關(guān)注

0文章

12瀏覽量

8786

發(fā)布評論請先 登錄

基于瑞薩電子RA8T2 sensorless方案的樣例工程 可對電流環(huán)進行TCM化設(shè)置

基于網(wǎng)關(guān)的污水泵站PLC數(shù)據(jù)對接水務(wù)平臺方案

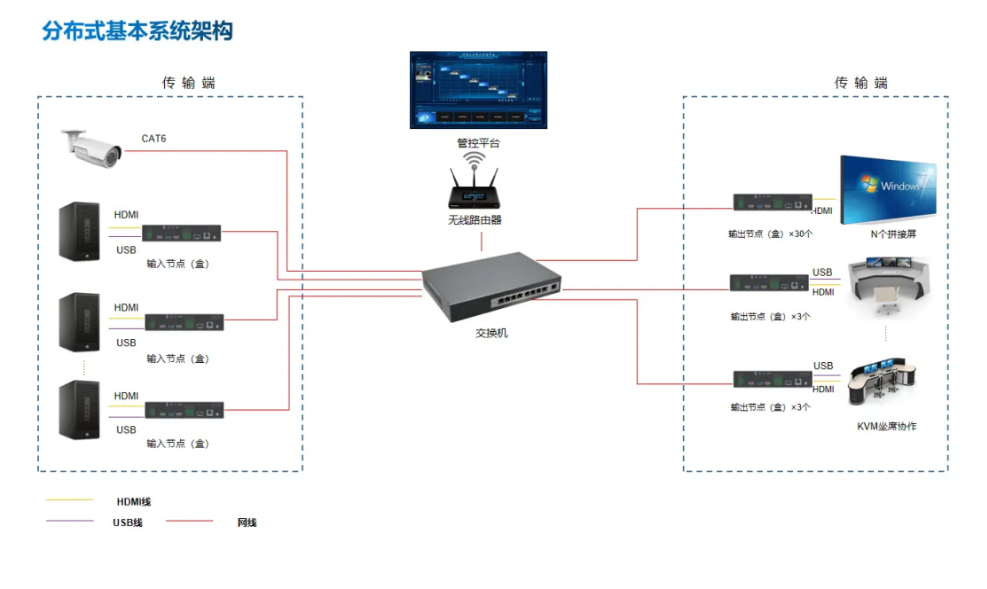

深蕾半導(dǎo)體IP-KVM產(chǎn)品方案解析

直流充電安全測試負載方案解析

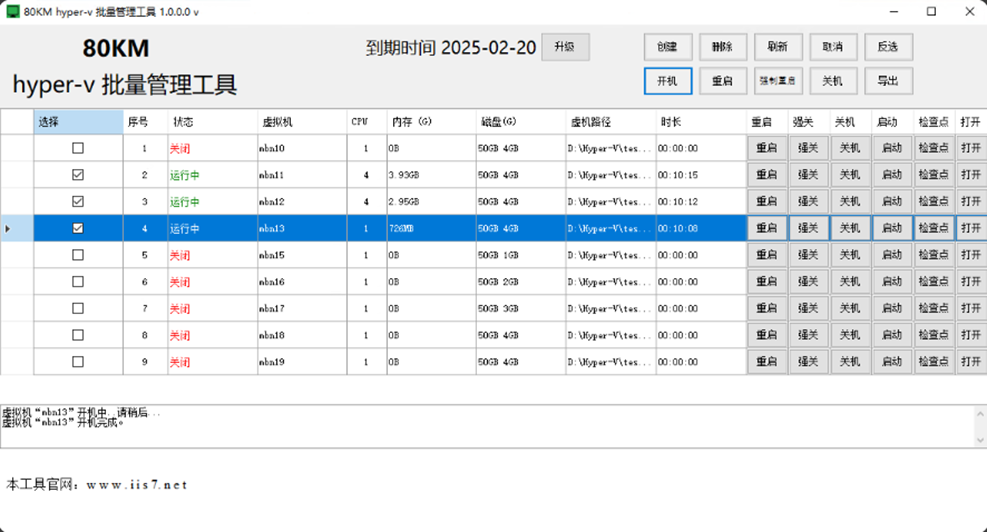

hyper v 虛擬化,hyper-v虛擬化:企業(yè)級虛擬化解決方案的全面解析

解析AMR設(shè)計關(guān)鍵要素:照明方案、通信方案

M12連接器技術(shù)規(guī)格解析:工業(yè)自動化的優(yōu)選方案

自動化創(chuàng)建UI并解析數(shù)據(jù)

自動化創(chuàng)建UI并解析數(shù)據(jù)

PLC遠程監(jiān)控物聯(lián)網(wǎng)方案解析

XPM6329 富滿推出22.5W移動電源芯片

求助各位關(guān)于Verilog當(dāng)中模塊例化、端口與引腳 的問題

ZWS云平臺應(yīng)用(5)-raw數(shù)據(jù)解析

可例化的XPM方案解析

可例化的XPM方案解析

評論