我們很多時候會將目光放在最新和最先進的技術節點上,因為它們被用來制造最密集,最快,最節能的處理器。但是正如我們在英特爾最近的2020年架構日期間提醒我們的那樣,需要一系列晶體管設計來構建異構系統。

“沒有一個晶體管在所有設計點上都是最佳的,”英特爾首席架構師Raja Koduri說。“要達到超高頻率,高性能臺式機CPU需要的晶體管與高性能集成GPU所需的晶體管完全不同。”

問題是,把處理內核,特定功能加速器,圖形資源和I / O聚合到一起,然后將它們全部蝕刻到10nm的單片芯片上,這將使制造非常非常困難。但是,替代方案(將它們分開并連接在一起)則提出了自己的挑戰。那么就需要封裝方面的創新,通過改善密集電路與其所裝電路板之間的接口來克服這些障礙。

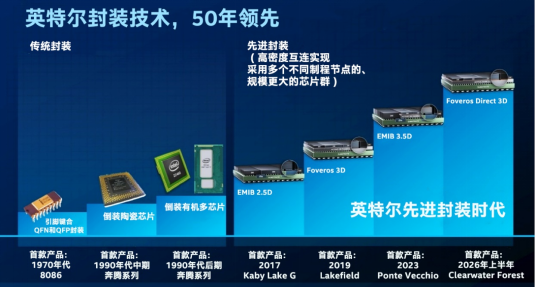

早在2018年,英特爾就制定了一項計劃,希望在不犧牲速度的情況下使小型設備協同工作。Koduri繼續說道:“我們說,我們需要開發一種技術來將芯片(chip)和小芯片(chiplet)連接到一個封裝中,以使其與單片SoC的性能,能效和成本相匹配”,“我們還說過,我們需要一個高密度互連路線圖,以低功耗實現高帶寬。”Koduri接著說。

在一個基于制程工藝技術來確定贏家和輸家的行業中,創新的封裝方法將成為計算霸主之爭的力量倍增器。

關鍵點:

EMIB(Embedded Multi-die Interconnect Bridge )使用嵌入在封裝基板中的微小硅橋( silicon bridges)來促進die到die的連接

高級接口總線(Advanced Interface Bus:AIB)是一種開源互連標準,用于在小芯片之間創建高帶寬/低功耗連接

Foveros通過堆疊die將封裝帶到三維。其第一款基于Foveros的產品將面向筆記本電腦和智能手機之間的市場。

Co-EMIB和Omni-Directional Interface通過促進更大的靈活性,有望超越英特爾現有的封裝技術進行擴展。

用EMIB克服單片芯片的成長煩惱

直到最近,如果你希望將異構die放在單個封裝上以實現最佳性能,則可以將這些die放置在一塊稱為中介層的硅片上,并通過中介層進行布線以進行通信。硅通孔(TSV)(電連接)穿過中介層并進入基板,該基板形成了封裝的底部。

業界將其稱為2.5D封裝。臺積電(TSMC)早在2016年就用它制造了NVIDIA的Tesla P100加速器。一年之前,AMD在硅中介板上結合了大型GPU和4GB的高帶寬內存(HBM)來創建Radeon R9 FuryX。。但這增加了固有的復雜性,降低了產量并增加了成本。

英特爾的EMIB旨在通過放棄interpose,而采用嵌入襯底層的微型硅橋來減輕2.5D封裝的限制。橋上裝有微型凸塊,有助于die之間的連接。

英特爾工藝和產品集成總監Ramune Nagisetty表示:“當前一代的EMIB提供55微米的微型凸點間距,并且路線圖可以達到36微米。” 將其與典型有機封裝的100微米凸點間距進行比較,EMIB可以實現更高的凸點密度。

小型硅橋還比中介層便宜很多。Tesla P100和Radeon R9 Fury X是高價旗艦產品,而英特爾首款帶有嵌入式橋的產品之一是Kaby Lake G,這是一個結合了第八代Core CPU和AMD Radeon RX Vega M圖形的移動平臺。基于Kaby Lake G的筆記本電腦無論如何都不算便宜。但是,他們證明了EMIB能夠將異類芯片集成到一個封裝中,從而鞏固了寶貴的電路板空間,增強了性能并與分立組件相比降低了成本。

英特爾的Stratix 10 FPGA還采用EMIB將來自三個不同代工廠的I / O小芯片和HBM連接在一起,這些代工廠使用六個不同的技術節點制造,并封裝在一個封裝中。通過將收發器,I / O和內存與核心結構分離,英特爾可以為每個die選擇晶體管設計。添加對CXL,更快的收發器或以太網的支持,就像換掉那些通過EMIB連接的模塊化磚一樣容易。

使用高級接口總線標準化芯片對芯片的集成

在小芯片可以混合和匹配之前,可重用的IP塊必須知道如何通過標準化接口相互通信。對于Stratix 10 FPGA,英特爾的嵌入式橋接器在其核心結構和每個圖塊之間都帶有高級接口總線(AIB)。

AIB旨在用類似主板通過PCI Express集成元件相似的方式在封裝上實現模塊化集成。但是,盡管PCIe通過很少的電線驅動非常高的速度,AIB利用EMIB的密度來創建一個寬的并行接口,該接口以較低的時鐘速率運行,從而簡化了發送和接收電路,同時仍然實現了非常低的延遲。

第一代AIB提供2 Gb / s有線信號傳輸,從而使英特爾能夠實現異構集成以及單片SoC一樣的性能。預計將于2021年推出的第二代版本將支持每條導線高達6.4 Gb / s的傳輸速度,凸點間距小至36微米,每位傳輸的功率更低以及與現有AIB實現的向后兼容性。

值得注意的是,AIB在封裝方面是不可知的。盡管英特爾使用EMIB來連接,但臺積電的晶圓上晶圓上芯片(CoWoS)技術也可以搭載AIB。

今年早些時候,英特爾成為由Linux基金會托管的接口,處理器和系統通用硬件聯盟(CHIPS)聯盟的成員,以貢獻AIB許可證作為開源標準。當然,這個想法是為了鼓勵行業采用,并促進配備AIB的小芯片庫。

英特爾的Nagisetty說:“我們目前有10個來自多家供應商的基于AIB的設計正在生產中或正在點亮” “在不久的將來,生態系統合作伙伴(包括初創公司和大學研究小組)還會再提供10張圖塊。”

Foveros在第三維上提高密度

將SoC分解為可重用的IP塊并將其與高密度橋接器水平集成是Intel計劃利用制造效率并繼續擴展性能的方法之一。根據公司的封裝技術路線圖,下一步要進行的工作涉及使用細間距的微型凸臺將die彼此面對面地堆疊在一起。英特爾稱之為Foveros的這種三維方法可縮短die之間的距離,并使用較少的功率移動數據。英特爾的EMIB技術的額定值為大約0.50 pJ /位,而Foveros的額定值為0.15 pJ /位。

與EMIB一樣,Foveros允許英特爾為其堆棧的每一層選擇最佳的處理技術。Foveros的第一個實現(代號為Lakefield)將處理核心,內存控制和圖形塞入以10nm制造的芯片中。該小芯片位于基本芯片的頂部,該芯片包含您通常在平臺控制器中樞中找到的功能(音頻,存儲,PCIe等),該功能以14nm低功耗工藝制造。

完整的Lakefield封裝尺寸僅為12x12x1mm,可在筆記本電腦和智能手機之間實現新型設備。但是我們不希望Foveros僅服務于低功耗應用。在2019年HotChips問答環節中,英特爾研究員Wilfred Gomes 預測了該技術的未來普及性。他說:“我們設計Foveros的方式,它涵蓋了整個計算范圍,從最低端的設備到最高端的設備。”

微縮為我們提供了另一個需要考慮的變量

英特爾2020年架構日期間制定的封裝路線圖按互連密度(每平方毫米的微凸起數量)和功率效率(每傳輸的數據比特消耗的能量pJ)繪制了每種技術。除Foveros之外,英特爾還追求芯片上混合鍵合,以進一步推動這兩個指標。期望達到超過10,000個凸塊/mm2和小于0.05 pJ / bit。

但是先進的封裝技術可以提供更高帶寬和更低功耗之外的實用性。EMIB和Foveros的組合-被稱為Co-EMIB-有望提供超越任何一種方法的擴展機會。尚無Co-EMIB的實際示例。但是,您可以想象大型有機程序包具有連接Fovoros堆棧的嵌入式橋,這些橋結合了加速器和內存以進行高性能計算。

英特爾的全向接口(ODI)通過彼此相鄰地連接小芯片,連接垂直堆疊的小芯片并直接通過銅柱為堆疊中的頂部芯片供電,從而提供了更大的靈活性。這些支柱比Foveros堆疊中穿過基本芯片的TSV大,從而最大程度地降低了電阻并改善了功率輸出。可以任意方向連接管芯并在較小的頂部堆疊較大的瓦片的自由度為Intel提供了迫切需要的布局靈活性。當然,在Foveros的功能基礎上,這看起來是一項很有前途的技術。

責任編輯:tzh

-

處理器

+關注

關注

68文章

19837瀏覽量

234006 -

芯片

+關注

關注

459文章

52323瀏覽量

438207 -

英特爾

+關注

關注

61文章

10185瀏覽量

174218 -

晶體管

+關注

關注

77文章

9996瀏覽量

141047

發布評論請先 登錄

世紀大并購!傳高通有意整體收購英特爾,英特爾最新回應

英特爾先進封裝,新突破

英特爾先進封裝:助力AI芯片高效集成的技術力量

英特爾計劃分拆RealSense深度攝像頭業務

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

英特爾展示互連微縮技術突破性進展

英特爾推出全新英特爾銳炫B系列顯卡

英特爾封裝技術方面的規劃

英特爾封裝技術方面的規劃

評論