時至今日,不管從國際形勢還是國家對于“中國芯”的扶持,“國產化”這一話題越來越要付出實踐,對于FPGA這一“萬能芯”也是很多企業會優先考慮的。

從華為被“卡脖子”到集成電路正式成為國家學科,都能看出國家對于國產芯的迫切發展,今天就來簡單總結下國產FPGA這一“萬能芯”的發展概況。

下面排名不分先后:

西安智多晶微電子有限公司

1.1 公司簡介 西安智多晶微電子有限公司,成立于2012年,總部位于西安,北京設立有EDA軟件研究中心。創始團隊擁有三十多年豐富的FPGA設計制造經驗,曾就職于海外該領域領先企業,并擔任多個專業方向技術帶頭人。核心團隊來自于國內各知名院校和優秀的FPGA研發團隊,是國內目前集硬軟件設計、生產、銷售最具競爭力的高科技企業。 公司專注可編程邏輯電路器件技術的研發,并為系統制造商提供高集成度、高性價比的可編程邏輯器件、可編程邏輯器件IP核、相關軟件設計工具以及系統解決方案。賦能產業,“芯”系未來,是智多晶的奮斗愿景,團隊致力于在LED驅動、視頻監控、圖像處理、工業控制、4G/5G通信網絡、數據中心等各行業應用充分發揮FPGA的方案優勢,以市場和客戶為導向,幫助合作伙伴提升其核心競爭力。 公司目前已實現55nm、40nm工藝中密度FPGA的量產,并針對性推出了內嵌Flash、SDRAM等集成化方案產品,截至2018年已批量發貨2KK片。通過嚴謹科學的設計,360度圍繞客戶的技術支持及服務,以及貫穿全流程的高標準測試管理,我們正在為更多的行業合作伙伴提供最符合需求的高性價比FPGA整體解決方案。 官網:http://www.isilicontech.com/page29

1.2 FPGA系列

| 種類 | 工藝 | 概述 |

| Seagull 1000 系列CPLD | 0.162um | 見1.2.1 |

| Sealion 2000 系列FPGA | 55nm | 見1.2.2 |

| Seal 5000系列FPGA | 28nm | 見1.2.3 |

1.2.1 Seagull1000系列CPLD產品特性 ●采用0.162um的低功耗技術工藝,正向自主研發的構架設計,提供64-256宏單元陣列產品 ●采用先進的嵌入式閃存(eFlash)的低功耗存儲單元,具備數據加密功能 ●最大頻率Fmax=322MHz,3.5ns快速輸入輸出(I/O)引腳延遲 ●每個輸出可高達80 PTs,高達四個總體OE控制,四個專用總體時鐘輸入接口,每個宏單元都具備時鐘、輸出、使能設置/復位智能控制組合及在功能模塊間共享 ●豐富輸入資源(36輸入邏輯塊),提供狀態機及計數器設計,個別地方OE控制每個I/O引腳 ●核心操作電源為3.3V和1.8V,使用符合IEEE 1532接口的3.3V/1.8V在系統可編程(In-System Programmable,ISP) ●低功耗:靜態電流1.0mA @1.8V,是功耗敏感的應用的最佳解決器件 ●多功能可編程輸入輸出接口 ,支持3.3V, 2.5V or 1.8V I/O電源

1.2.2 Sealion 2000系列FPGA產品特性 ●采用55nm的低功耗技術工藝,正向自主研發,先進的低成本、低功耗FPGA架構 提供4K到25K的查找表邏輯單元,單一封裝集成了2M*32 bit Synchronous DRAM(SDRAM) 嵌入式高速雙接口存儲器(dual port SRAM/FIFOBlock )(真雙端/偽雙端) 內置多個18×18/9×9可串行乘法器以及算術邏輯單元(ALU),可做兩層疊加實現DSP處理的應用 ●內置2個鎖相環(PLL)和2個延時鎖相環(DLL),提供倍頻、分頻、相位轉移等系統時鐘功能 ●通用輸入輸出端口支持高速存儲器界面,DDR、DDR2 支持400Mbps DDR2界面,DQS輸入端90度相位轉換 DQS輸入端到系統時鐘接軌(clock domain transfer),1:4 and 4:1串行并行轉換(Serializer / Deserializer) ●通用輸入輸出端口,支持800Mbps LVDS 支持低壓差分信號傳輸接口(LVDS)800Mbps 時鐘延遲匹配電路,7:1 LVDS界面 ●芯片性能能夠與Spartan-6/Cyclone-4系列的FPGA芯片相匹配

1.2.3 Seal 5000系列 FPGA概述 Seal 5000FPGA同樣采用正向設計,芯片軟件設計流程和ISE/Quartus II/Diamond 類似,包括綜合、約束、布局布線、下載編程等。智多晶的芯片使用自主研發的FPGA開發軟件“HqFpga”, 完成綜合、布局布線、時序分析、配置編程和片內邏輯分析。智多晶的Seal 5000系列FPGA芯片,在性能上能夠與Virtex-7系列的FPGA芯片對標。 Seal 5000系列FPGA為高性能邏輯設計人員、高性能DSP設計人員和高性能嵌入式系統設計人員提供了滿足邏輯、DSP、軟/硬微處理器和連接功能的需求的最佳解決方案。 Seal 5000 FPGA器件系列特性 ●自主研發,先進的低成本、低功耗的FPGA架構 基于28納米技術工藝(28nm),20K到200K的查找表邏輯單元 嵌入式高速雙接口存儲器(dualport SRAM/FIFOBlock)(真雙端/偽雙端) 內置多個with pre-adder18×18/9×9可串行乘法器以及算術邏輯單元(ALU),可做兩層疊加實現DSP處理的應用,頻率高達500MHZ。 ●內置鎖相環(PLL)提供倍頻、分頻、相位轉移、spreadspectrum等系統時鐘功能 ●通用輸入輸出端口支持高速存儲器界面,SDR、DDR2、DDR3、LPDDR2、LPDDR3 支持1.2GbpsDDR3界面,DQS輸入端90度相位轉換 DQS輸入端到系統時鐘接軌(clock domain transfer),1:4 and 4:1串行并行轉換(Serializer / Deserializer) ●通用輸入輸出端口,支持1.2GbpsLVDS 支持低壓差分信號傳輸接口(LVDS)1.2Gbps ●高速串行并行接口(SERDES): 4個通道的嵌入式SERDES 支持6Gbps全雙工串行(full-duplex)協議 內置物理編碼子層(Physical Coding Sublayer、PCS) 支持常用的數據協議,包括PCIExpress、千兆以太網(GbE, SGMII)、XAUI、SRIO、CPRI、OBSAI、SD-SDI和HD-SDI. ●支持商業與工業溫度等級 1.3 EDA軟件與License

我在官網沒找到相關的EDA軟件和License介紹,但是在

北京飄石科技有限公司(http://www.uptops-dt.com/nd.jsp?id=46#_np=2_302)(兩家公司關系下面會介紹)提供了下載鏈接和評估版本,但是不清楚為什么不在自己官網集成或者添加鏈接。

下面開始使用一下HqFPGA。

轉自:https://zhuanlan.zhihu.com/p/32061948

有了自家的FPGA,沒有自己的綜合工具怎么辦,那也沒人愿意使用啊。智多晶找到了國內一家專業做FPGA綜合工具的公司---北京飄石科技有限公司(北京飄石官網),然后建立合作。在我實習期間,該公司已和智多晶商洽并購事宜,目前從飄石官網來看,產品沒有更新了,估計已經被智多晶拿下了,成為智多晶不可分割的一部分。智多晶FPGA綜合工具名為HqFpgaXIST,我們自己稱為HQ。

國內外大多數FPGA軟件是單點工具的堆集,雖然這些單點工具也“集成”在一個軟件系統中,但工具之間只能通過文件接口來傳遞設計信息,造成工作重復、運行時間長、一致性差、無法全局優化等問題。HqFpga在單一的可執行文件中集成了RTL-to-FPGA的所有功能。各功能模塊共享統一的數據模型、器件模型及時序分析引擎,從而得以完成簡單、快速、高效及優化的FPGA開發。

具體有哪些特色呢? 1.FPGA 資源感知綜合(Resource Aware Synthesis) ●表達式優化 ●資源共享 ●FSM優化 ●MUX優化 ●片上專用資源推斷與映射 2.時序驅動(TimingDriven)優化 ●組合邏輯優化、寄存器優化 ●映射、組裝、布局、布線 3.邏輯與物理優化 ●時鐘感知布局(Clockaware placement) ●次級時鐘網絡優化 ●物理綜合 4.RTL級別調試 ●直接在RTL源代碼上選取信號 ●“所見即所得” ●更用戶友好 5.豐富的調試手段 ●多種觸發條件 ●多種采樣深度 ●不同采樣位置 ●波形顯示 6.基于標準JTAG接口 7.支持遠程調試 8.與開發環境無縫集成

當然有些功能是剛做出來,只能達到功能實現,還沒有很好的交互,比如Insight(該功能類似于邏輯分析儀,完全自主開發,不是像quartus的signaltap是從綜合網表級抓取信號,而是直接在RTL級抓取信號)目前用于簡單調試可行,太龐大的工程還不能很好的支持。

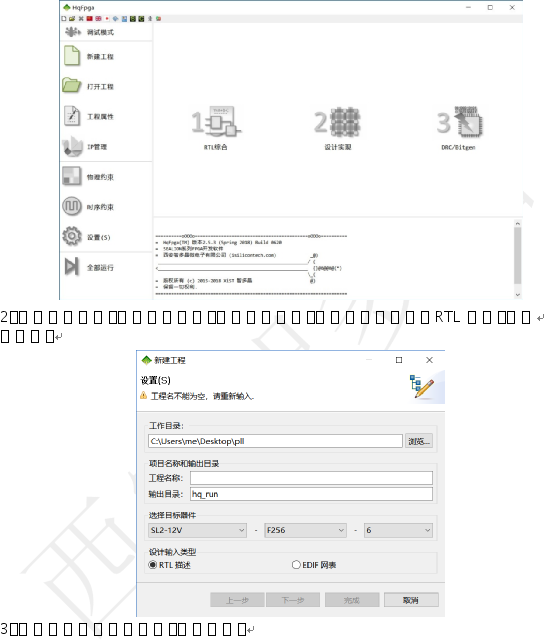

HQ風格是這樣的。

還可以是這樣的。HQ支持兩種界面,前圖為標準界面,也就是默認界面,你點擊左上方“C”按鈕即可切換為后圖傳統視圖風格,你喜歡怎樣就怎樣,個人比較喜歡第一種標準視圖風格,簡潔干凈,主視圖區三個大大的標志從左往右走完,即可完成從RTL--->bitstream(下載文件)的全過程。同時支持腳本操作,是標準的tcl,這個在FPGA開發的時候真是良心設計(給贊了)。

說到綜合器,必然會考慮其性能,尤其是編譯速度,畢竟像vivado這樣的巨無霸等起來都可以來局王者農藥了。我這里拿我做過的一個攝像頭+VGA+LCD的工程來測試一下。具體軟件操作這里不做詳細介紹,可以從下圖所示位置查看用戶手冊,比較全面,尤其是命令方式操作。

先上幾幅圖來感受一下軟件的風格,您肯定會覺得和市面上各大佬的風格完全不同。

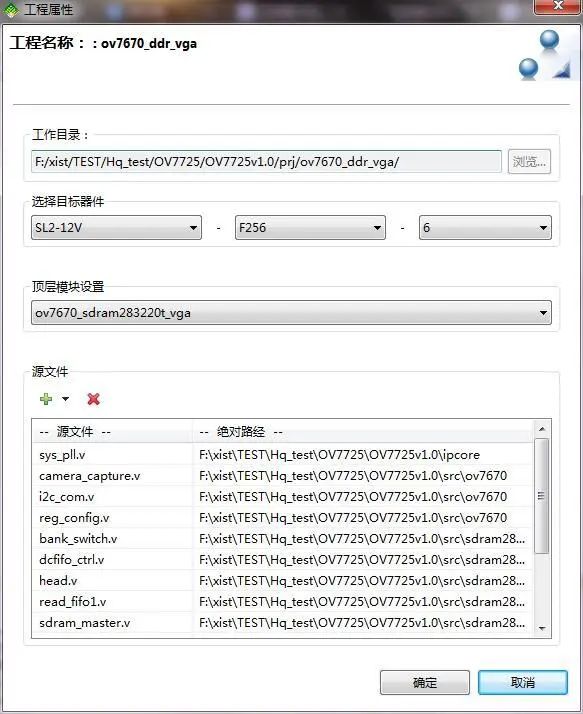

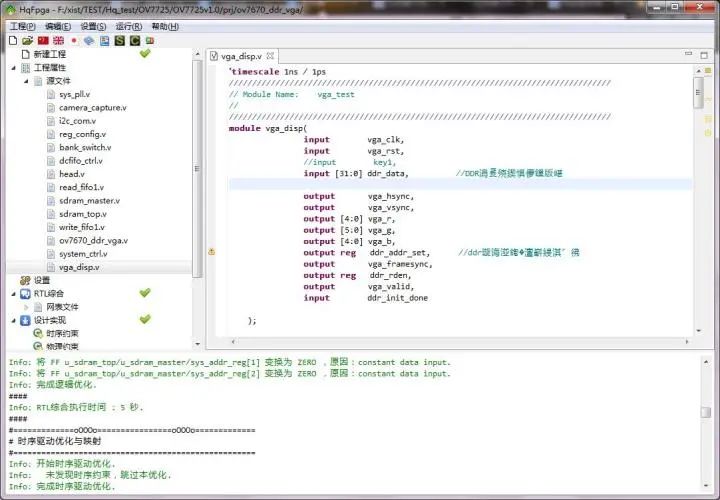

新建工程后,是這樣添加源文件的。新建工程的時候需要選擇具體哪一款FPGA。

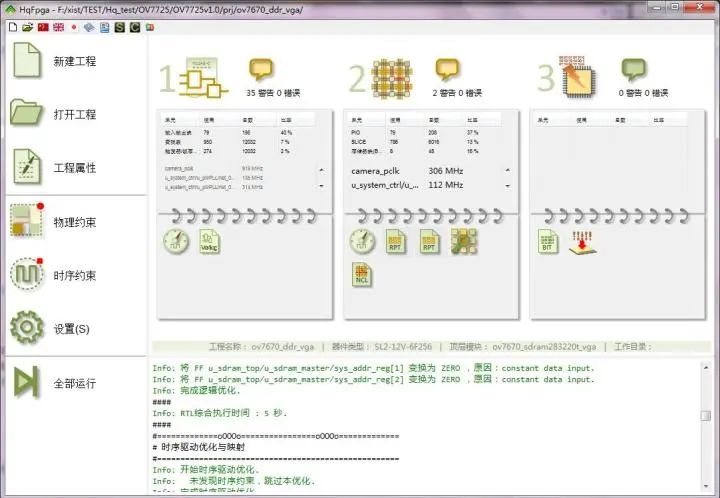

工程文件添加好以后,以此點擊點擊工作區的那三個大按鈕,就可以完成編譯和綜合工作。在主視圖去下方可以看到編譯信息。如果有錯誤同樣會提示,只不過目前不是很完善,無法雙擊錯誤提示信息進行定位,但是提供了行號,也比較方便。可以通過點擊主視圖區中小按鈕進行信息查看。

比如綜合信息查看,還可以在工程文件夾下找到該記錄文件。

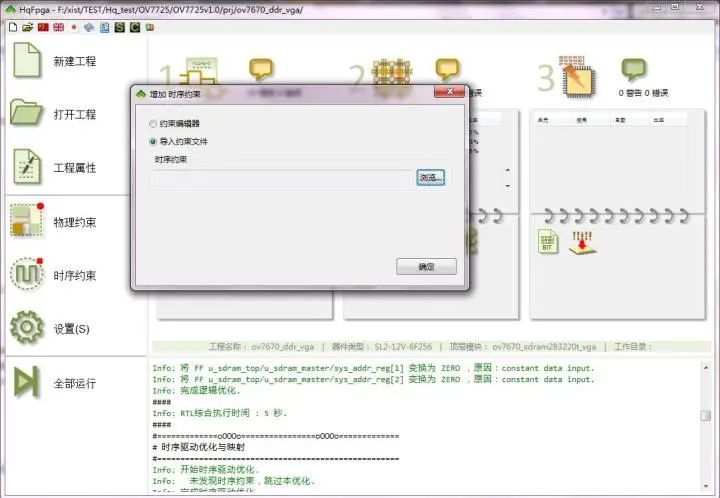

比如時序約束文件的建立或導入,時序約束文件是標準的.sdc文件。

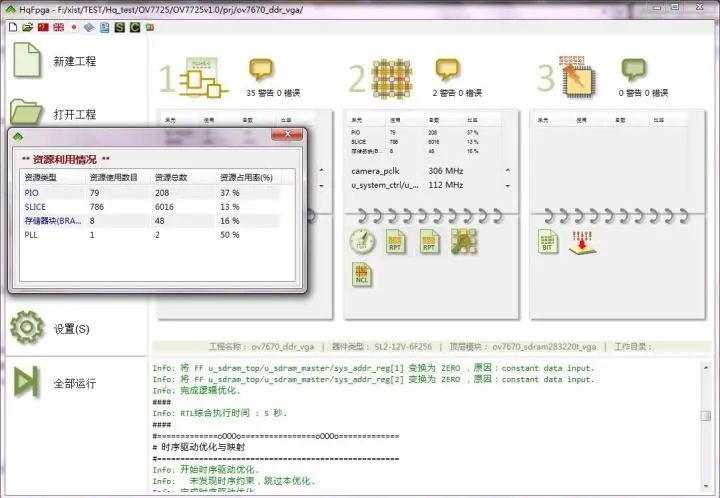

比如資源利用查看。

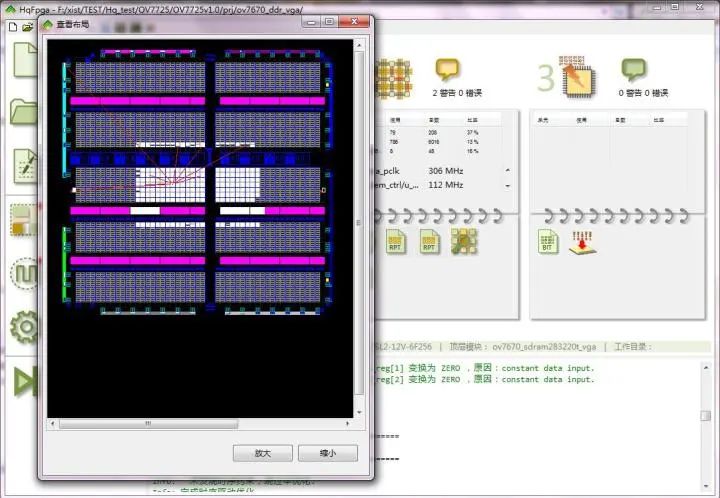

比如布局情況查看,可放大縮小,使用和quartus的差不多,不過HQ更簡潔,也意味著功能還不是能強大,比如沒有邏輯鎖定功能。

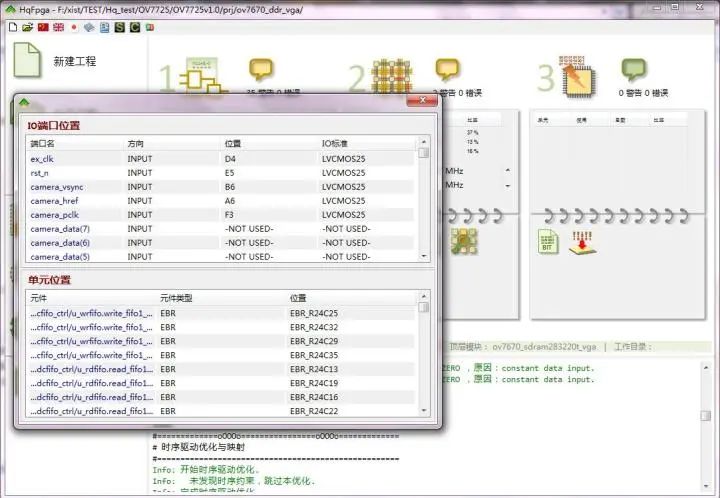

比如綜合后個單元位置信息。

比如資源利用統計簡報。

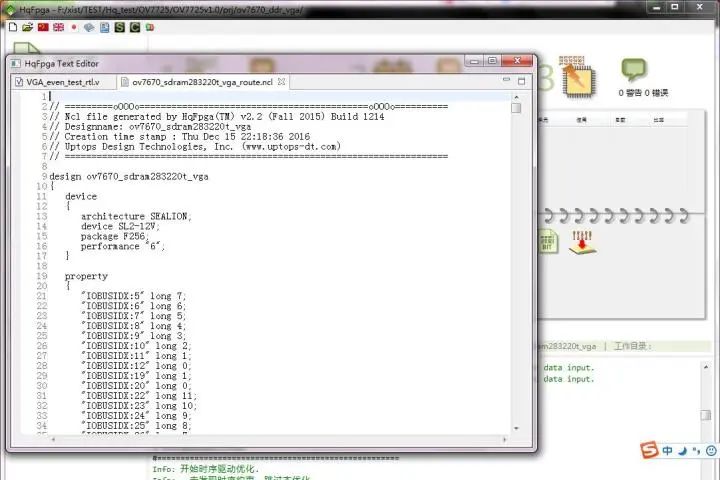

比如綜合后生成的ncl網表文件,直接可以查看,尤其是在時序過不去的時候,需要手動布局可以用這個文件。最后就是生產比特流,作為下載文件。目前下載文件格式是.svf。該版本HQ還不能支持下載,需要ispLEVER中的SVFdebug插件進行文件下載。

這是在傳統視圖模式下的情況,和普通工具類軟件差不多,左邊工程目錄,右邊編輯區。標準和傳統兩種視圖可以任意切換,溜溜的。

看了這么多圖片,相信您已經感覺到了HQ和別家綜合器的不同之處了,那么HQ性能如何呢?我們可以查看綜合信息來一探究竟。

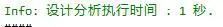

從上圖可以看到這個過程只花費了67s就生成了比特流下載文件,我的筆記本是i3處理器,用了5年了,反正很卡。那么這個表現到底怎么樣呢?由于HQ還不是很完善,尤其是調試部分的功能,所以在做這個工程之前是用altera的cyclone4進行實現,然后移植到智多晶的FPGA上,幸好這個工程還沒有刪除,所以我用quartus進行綜合,看看二者的差別。

不知道圖片右下角的時間您能不能看清,我專門標注了,4分31秒。HQ用的時間67秒,是quartus的1/4,這個數據可能和電腦有很大關系,但是我是在同一臺機子上做的測試,所以比較可信。

這或許是因為HQ現在還有一些功能不具備,導致其綜合速度完勝quartus。但是也有一些必然因素。我在實習期有幸和飄石公司的技術大拿因為項目交流過,他主要負責HQ中bitstream的生成,從他那里了解到HQ所用的布局布線的算法以及下載文件生成的算法和ISE、vivado、quartus、diamond以及synplify(綜合部分算法)不同,具體有哪些不同我也不清楚,畢竟綜合器里面全是算法密集區,但是可以通過HQ綜合過程的打印信息可以大概知道RTL到bitstream這個過程經歷了哪些環節,十分詳細,如果您有興趣可以仔細研究,包括HQ綜合后的時序報告,個人覺得比Timequest好用很多,并且時序報告很直觀。

紫光同創

2.1 公司簡介

深圳市紫光同創電子有限公司,系紫光集團下屬公司,專業從事可編程邏輯器件(FPGA、CPLD等)研發與生產銷售,是中國FPGA領導廠商,致力于為客戶提供完善的、具有自主知識產權的可編程邏輯器件平臺和系統解決方案。 紫光同創注冊資本4億元,總投資超過15億元,是國家高新技術企業,擁有高中低端全系列產品,產品覆蓋通信、網絡安全、工業控制、視頻監控、汽車電子、消費電子、數據中心等應用領域。 紫光同創立足中國大陸,總部設在深圳,擁有上海、北京、成都等分公司,公司人數超過450人、研發人員占比超過85%,擁有專利近200項、核心專利占比超過85%。 官網:https://www.pangomicro.com/about/introduction/index.html

2.2 FPGA系列

| 種類 | 工藝 | 概述 |

| Titan系列系列FPGA | 40nm | 見2.2.1 |

| Logos系列FPGA | 40nm | 見2.2.2 |

| Compact系列CPLD | 55nm | 見2.2.3 |

2.2.1 Titan系列FPGA產品特性

Titan系列是中國第一款國產自主產權千萬門級高性能FPGA產品,采用40nm CMOS工藝和自主產權的體系結構,廣泛適用于通信網絡、信息安全、數據中心、工業控制等領域。 ·高達174K等效LUT4邏輯單元 ·40nm工藝;自主的LUT5架構;創新的軟硬件一體化開發流程 ·系統最高頻率500MHz,塊存儲器資源高達9Mbit ·支持多種高速IO接口:SERDES速率5.0Gbps; ·DDR3速率800Mbps; ·LVDS速率800Mbps; ·PCIE Gen2x4

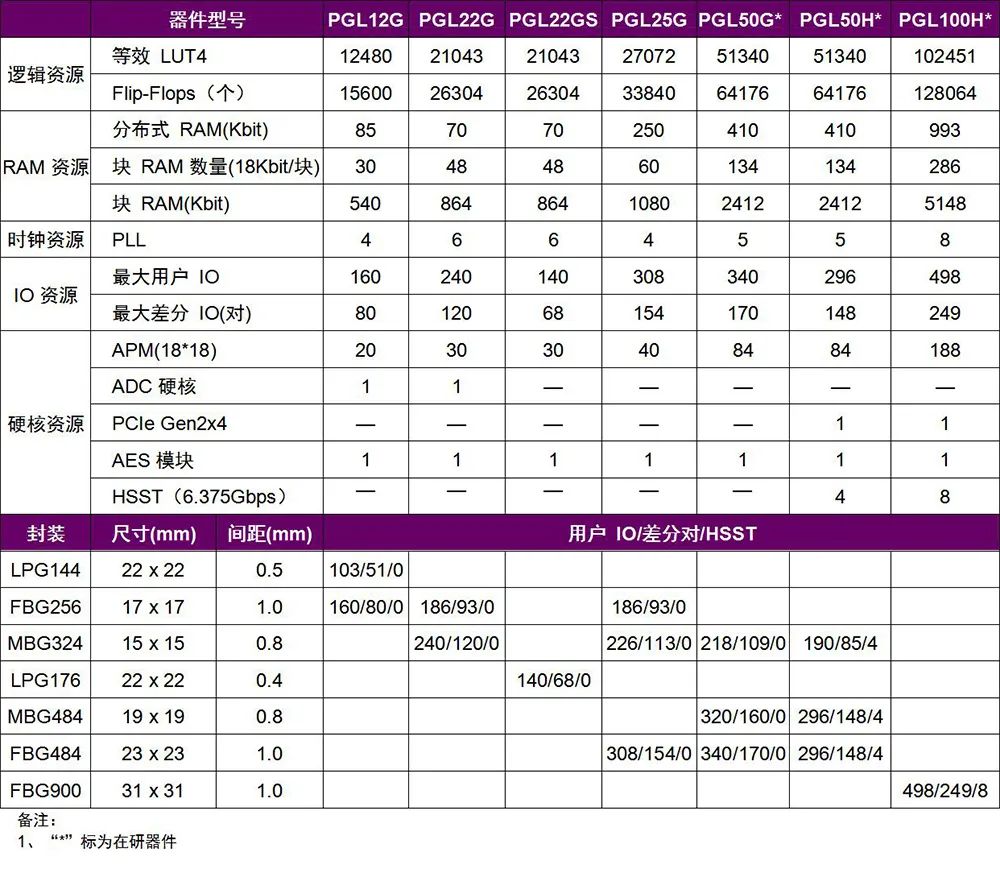

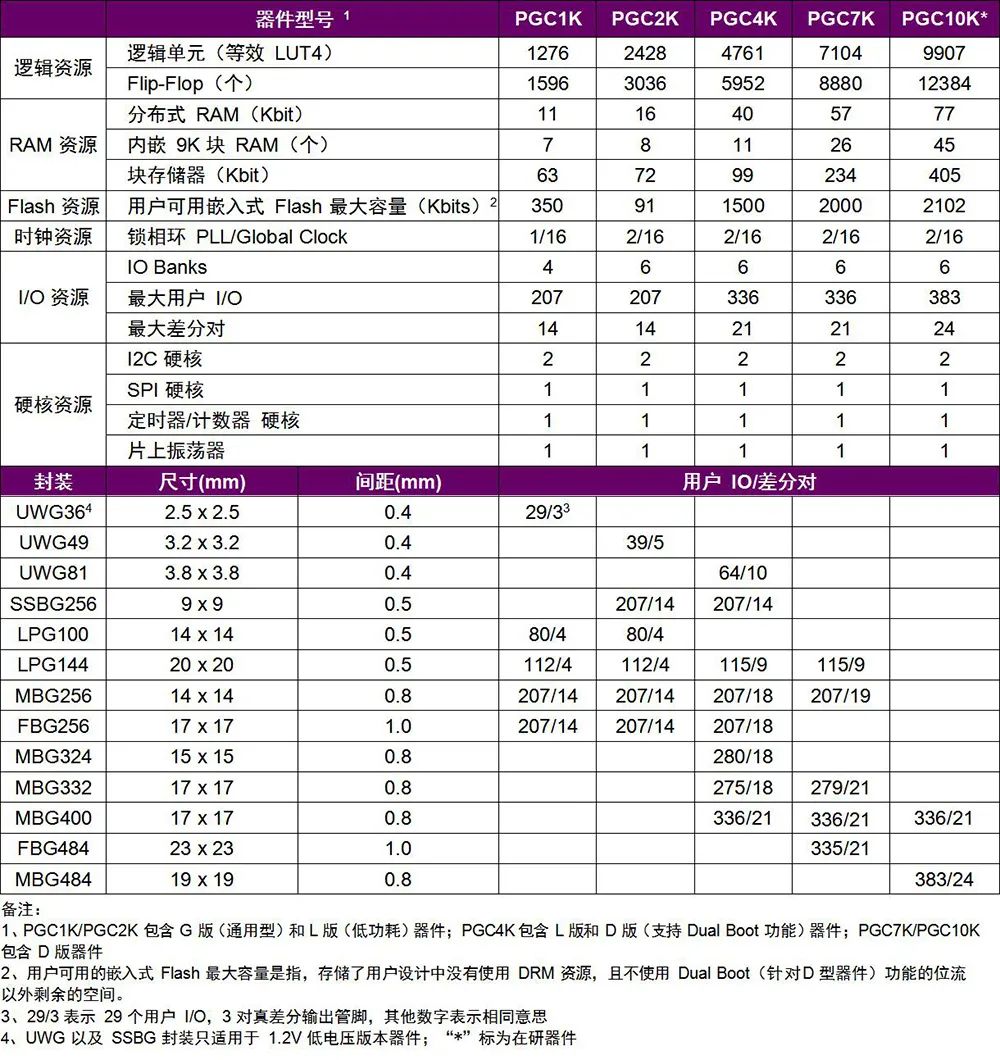

2.2.2 Logos系列FPGA產品特性

Logos系列FPGA采用40nm CMOS工藝和全新LUT5結構,集成RAM、DSP、ADC、Serdes、DDR3等豐富的片上資源和IO接口,具備低功耗、低成本和豐富的功能,為客戶提供高性價比的解決方案,廣泛應用于工業控制、通信、消費類等領域,是客戶大批量、成本敏感型項目的理想選擇。 ·40nm工藝,低成本、低功耗 ·12K~100K LUTs ·靈活可編程的CLM,每個CLM包含4個LUT5和6個寄存器 ·支持RAM軟錯誤檢測與糾錯功能 ·提供DDR3 800Mbps ·支持多種標準IO,LVDS、MIPI接口 ·LVDS最高速率800Mbps ·SERDES速率高達6.375Gbps ·集成ADC硬核 ·先進的256-bit AES加密

2.2.3 Compact系列CPLD產品特性

Compact系列CPLD產品,采用55nm eFlash工藝和自主產權體系結構,滿足低功耗、低成本、小尺寸的設計要求,適用于系統配置、接口擴展和橋接、板級電源管理、上電時序管理、傳感器融合等應用需求,廣泛應用于通信、消費電子、無人機、工業控制等領域。 ·55nm eFlash工藝,非易失可編程器件 ·1K~10K LUT4邏輯單元,支持3.3/2.5V內核、或1.2V低電壓內核 ·支持MIPI、LVDS、I2C、SPI、OSC、RAM、PLL等 ·支持RAM軟錯誤檢測與糾錯功能 ·支持Dual Boot功能,勿需外掛Flash ·支持后臺更新,禁止回讀等功能,安全性高 ·用戶IO高達383個 ·封裝小至2.5mm x 2.5mm

1.3 EDA軟件與License

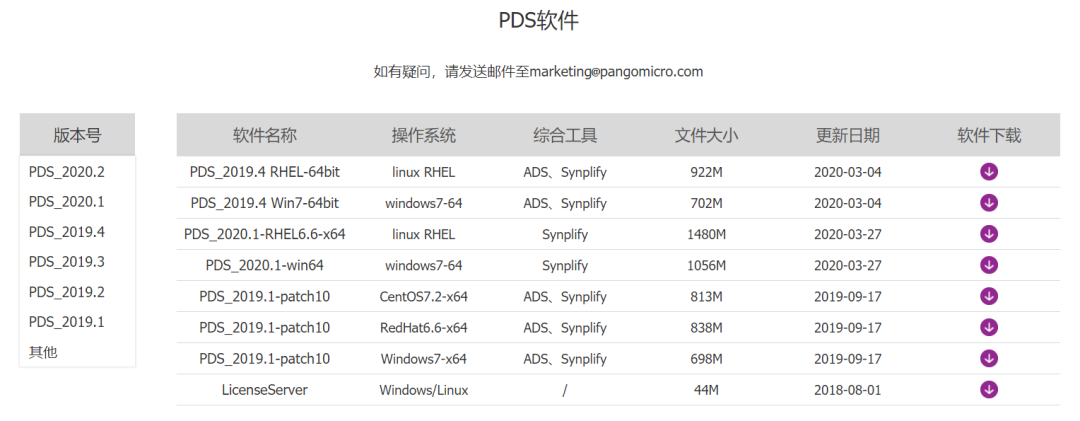

Pango Design Suite是紫光同創基于多年FPGA開發軟件技術攻關與工程實踐經驗而研發的一款擁有國產自主知識產權的大規模FPGA開發軟件,可以支持千萬門級FPGA器件的設計開發。該軟件支持工業界標準的開發流程,可實現從RTL綜合到配置數據流生成下載的全套操作。

官方可以下載相關的軟件和申請license,這一點比較友好。 轉自:https://zhuanlan.zhihu.com/p/31918794

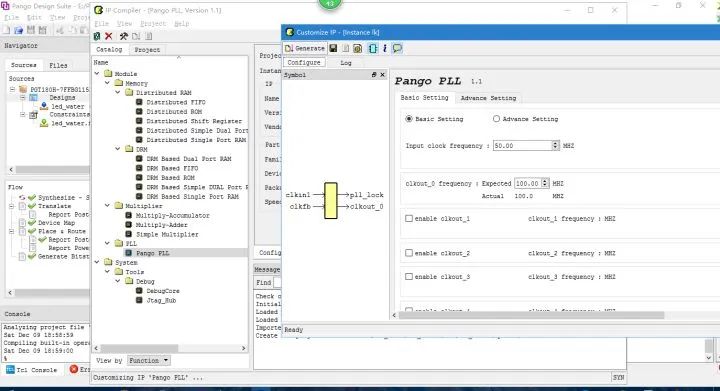

PDS軟件如下圖。

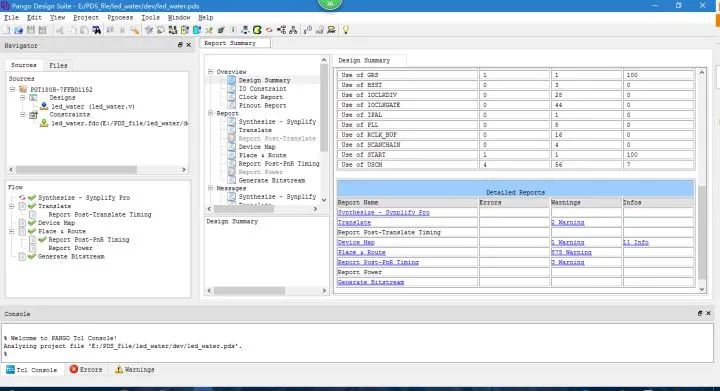

這是PDS 2017.1的界面

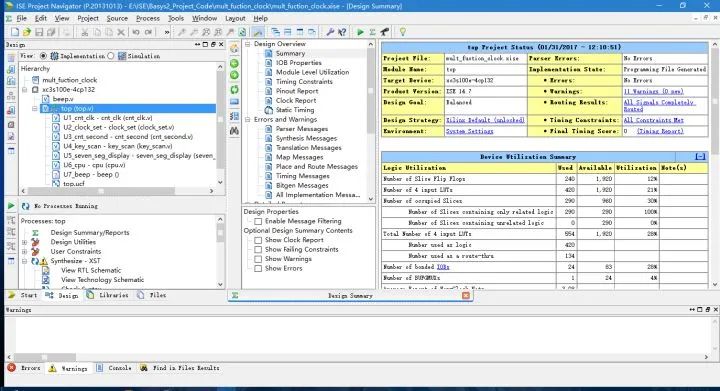

這是ISE14.7的界面

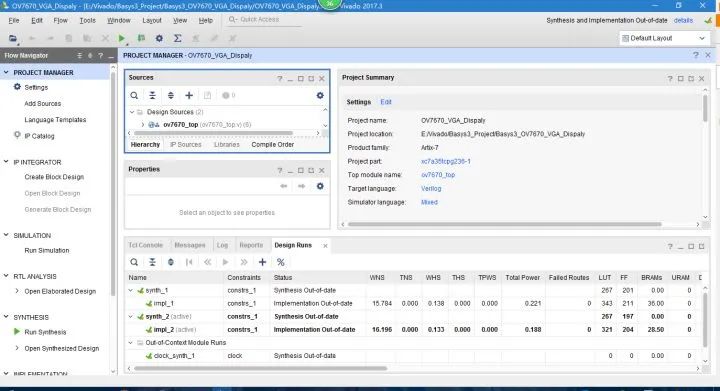

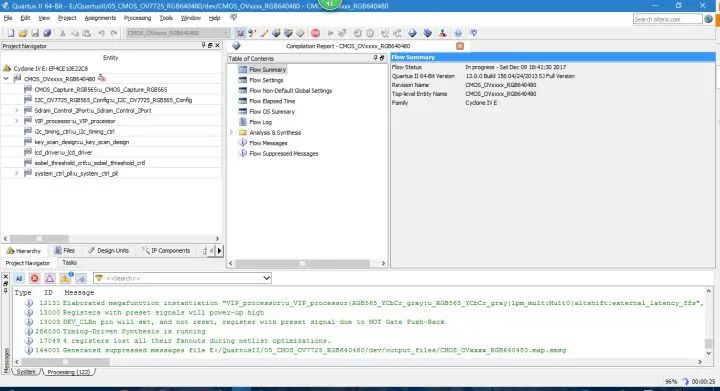

這是Vivado 2017.3的界面

這是Quartus II 13.0的界面 恩,相信已經有朋友看出來了,PDS這個界面還真和ISE有點神似,不過相似沒關系,看著還算簡潔,而且PDS的軟件安裝包只有三百多兆,比起其他幾款都小了很多,可能是紫光的產品還比較少吧,據我所知,目前紫光只有兩款FPGA,X家和A家多的都數不過來了。PDS在編譯速度上還是比較慢的,我用我的i3低功耗筆記本實測幾款主流綜合工具,對于一個流水燈來說。ISE14.7和QuartusII13.0可能不到一分鐘就編譯完成,Vivado可能是由于內部算法的不同,會有2-3分鐘的時間,PDS我沒有掐表,目測五分鐘是有了。不過對于工程量大的設計,PDS的速度也沒有很明顯的降下來,我們比賽做的項目最后的大工程,我電腦用ISE14.7跑了有二十分鐘吧,PDS用的時間少了一點。綜合來說PDS在編譯速度上基本與ISE14.7持平,小工程ISE14.7完勝,大工程PDS略占便宜。畢竟ISE已經停更了么。當然在人性化設計和美觀上評價,我認為ISE還是好,也可能是我用習慣了吧。 對于軟件還有很多地方需要說說,比如我們要看自己寫的代碼的原理圖的話,ISE上直接點擊Synthesize-XST下的View RTL Schematic便可直接打開,那么PDS呢,需要重新打開一個新的界面(貌似是一個軟件),然后才能查看。

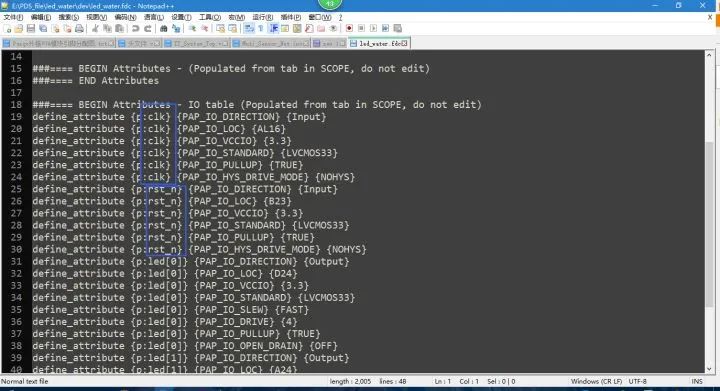

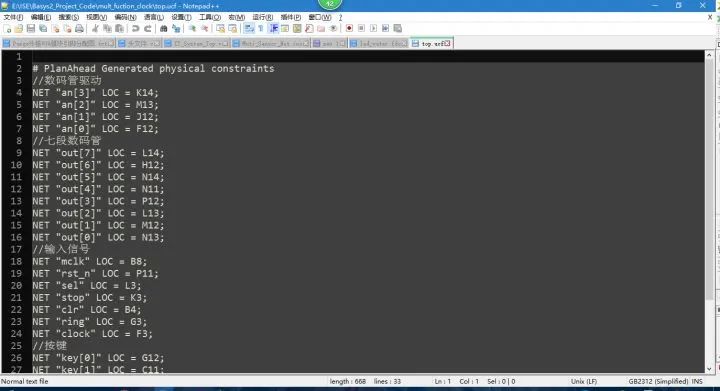

引腳分配文件的話,PDS后綴為fdc,打開文件里面是這樣的。

ISE是這樣的,恩還是ISE的好修改,好看。

IP調用界面的話,恩都差不多,都不怎么好看。

但是紫光的IP使用的話,我是必須要吐槽一下了,首先來說說PLL IP Core的調用,我對于X家和A家的軟件的話,我使用的時候感覺很便捷,填寫輸入時鐘,直接填寫輸出時鐘,然后直接輸出,至于相位偏移和占空比也是可以直接調的。PDS來了。

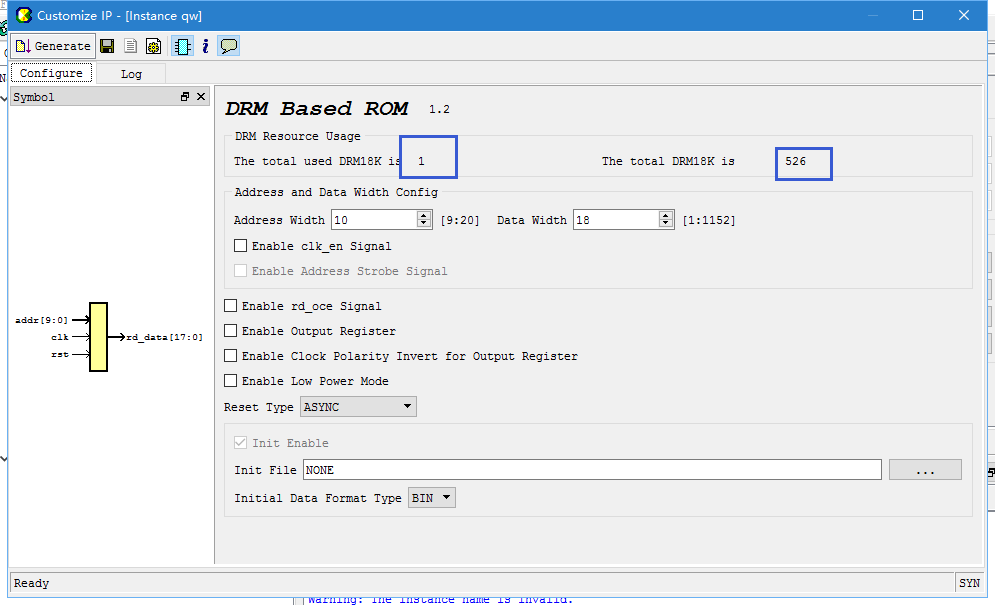

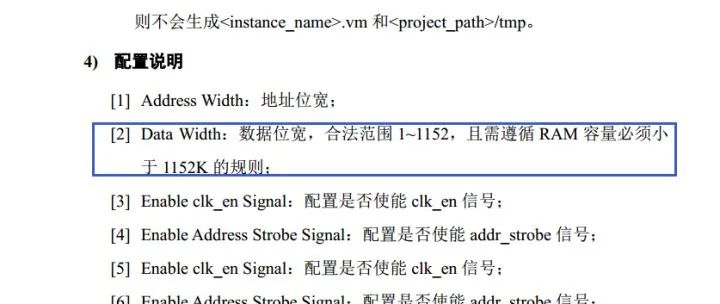

上圖中的1部分是輸入時鐘的,2部分是輸出時鐘的,那么下面第3部分就是用2部分倍頻的時鐘再分頻出來,輸出你要的時鐘,也就是說,比如你需要75Mhz,那么保證是整數分頻的話,你需要首先最少需要倍頻到150Mhz然后對150Mhz的時鐘進行3分頻,最后才是輸出你需要的時鐘,那如果我需要一個99Mhz的時鐘呢,對不起支持不了,當然我們實際使用的過程中也不需要那么奇葩的時鐘了。 接下來時RAM IP Core了,PGT180H的資源很多,芯片里面的存儲是一塊一塊的,一塊是18kbit,一共有526個,這算是很大的容量了,你需要的多的時候,它會自動拼接。

但是里面還有限制,比如下圖

最多只能用這么多了,再多的話生成兩塊拼起來也可以,不過一般情況也不會一次用這么多,除非一樣顯示很大的圖片,對,我顯示了。最后就是PDS自帶的編輯器了,說實話很不好用,雖然ISE也一樣很不好用,但是至少軟件支持和第三方編輯器級聯,但是PDS不支持,所以我這也有一點小建議了,就是希望PDS后面的版本可以支持第三方編輯器級聯,記住這是我建議的,后面如果紫光真的支持了,那肯定是聽了我的建議。至于軟件其他的一些功能使用,我使用時間也不長,就暫且不談。 安路科技

3.1 公司簡介 上海安路信息科技有限公司成立于2011年,總部位于浦東新區張江高科技園區。安路科技專注于為客戶提供高性價比的可編程邏輯器件(FPGA)、可編程系統級芯片、定制化嵌入式eFPGA IP、及相關軟件設計工具和創新系統解決方案。 專家團隊 公司創始團隊由具有國內外集成電路產業界豐富經驗的高級管理人才、工程技術人才和學術界資深科研人員組成。 公司研發人員70%以上具有碩士或博士學位,畢業于復旦、交大、清華、北大、中科院、UCLA、UIUC、UCSD等國內外高校。 資本歷程 2014年獲得中信資本投資 / 2015年獲得杭州士蘭微集團和深圳創維集團聯合投資 / 2017年獲得中國電子信息產業集團華大半導體有限公司和上海科技創業投資有限公司戰略投資。/2019年獲得深圳市創新投資集團有限公司、蘇州厚載成長投資管理合伙企業(有限合伙)等戰略投資。 業務范圍 安路科技量產和在研產品分為三個系列:高端PHOENIX(鳳凰)、中端EAGLE(獵鷹)、低端ELF(精靈)。產品在核心架構、軟件算法和系統集成等方面擁有多項技術專利。自主開發的全流程TD軟件系統和硬件芯片完美地結合在一起,提供了用戶從前端綜合到位流生成的完全開發平臺。目標市場為通訊設備、工業控制、視頻監控、人工智能、數據中心等應用領域。

安路科技根植中國,面向世界,積極參與國際競爭,努力成為中國可編程邏輯器件產業的主導企業和世界可編程邏輯器件解決方案的主要供應商。

官網:http://www.anlogic.com/pro.aspx?FId=n33

3.2 FPGA系列

| 種類 | 工藝 | 概述 |

| EAGLE系列 | 55nm | 見3.2.1 |

| ELF系列 | 55nm | 見3.2.2和3.2.3 |

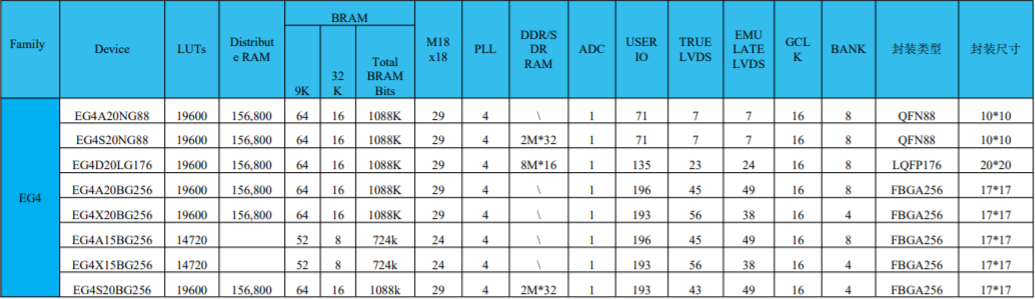

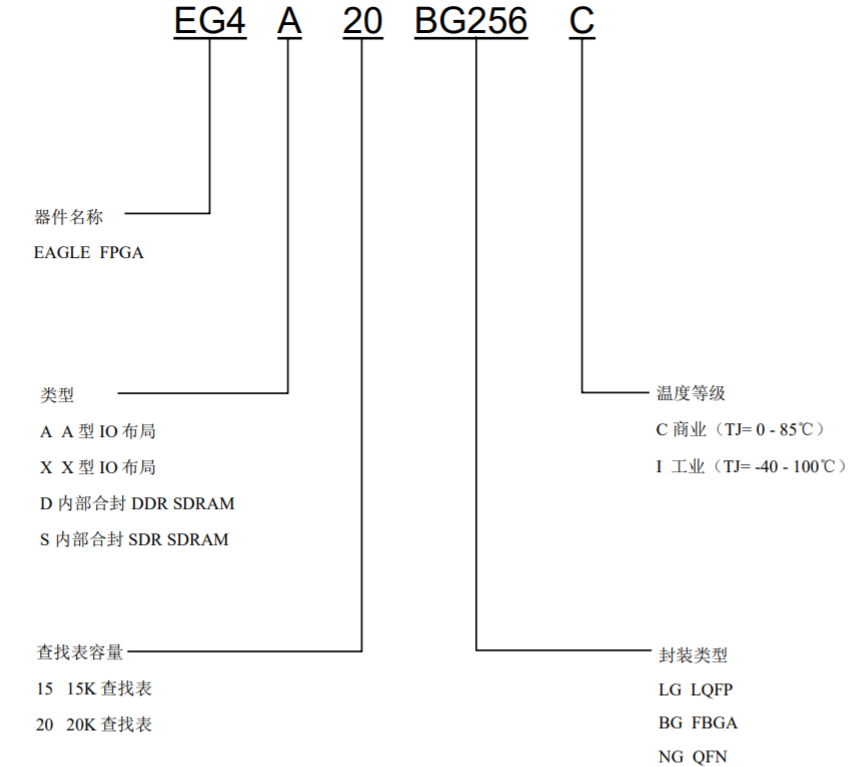

3.2.1 EAGLE系列FPGA產品特性 EAGLE 器件系列建立在一個優化的低功耗工藝基礎之上,并通過最低的成本實現較高的性能。適當的邏輯和乘法器,豐富多樣的片內存儲器,高達 1Gbps 的 IO 速率,使得 EAGLE 器件非常適合于圖像預處理,伺服控制和高速圖像接口轉換等領域。 器件特性 ? 靈活的邏輯結構 ? 共有 8 種器件,邏輯規模從 14720 到 19600 LUTs,用戶 IO 數量從 71 到 196 個 ? 低功耗器件 ? 先進的 55nm 低功耗工藝 ? 靜態功耗低至 5mA ? 支持分布式和嵌入式存儲器 ? 最大支持 156,800 Kbits 分布存儲器 ? 最大支持 1088Kbits 嵌入塊存儲器 ? 嵌入塊存儲器容量 9 Kbits,可配置為真雙口,8Kx1 到 512x18 模式 ? 專用 FIFO 控制邏輯 ? 嵌入塊存儲器容量 32 Kbits,可配置為真雙口,可設置為 2K*16 或 4K*8 ? 內置大容量存儲器 ? 部分封裝內置 2MX32b SDR SDRAM 存儲器 ? 部分封裝內置 8MX16b DDR SDRAM 存儲器 ? 可配置邏輯模塊(PLBs) ? 優化的 LUT4/LUT5 組合設計 ? 雙端口分布式存儲器 ? 支持算數邏輯運算 ? 快速進位鏈邏輯 ? 單一 Slice 支持 2 個 M18x18 或 4 個 M9x9 ? 源同步輸入/輸出接口 ? 輸入//輸出單元包含 DDR 寄存器 ? Generic DDRx1 ? Generic DDRx2 ? 高性能,靈活的輸入/輸出緩沖器 ? 可配置支持以下單端標準 ? LVTTL ? LVCMOS (3.3/2.5/1.8V/1.5/1.2V) ? PCI ? SSTL 3.3V (Class I and II) ? SSTL 1.8V and 1.5V (Class I and II) ? HSTL 1.8V and 1.5V (Class I and II) ? 通過配置支持以下差分標準 ? LVDS,Bus-LVDS, MLVDS, RSDS, LVPECL ? 支持熱插拔 ? 可配置上拉/下拉模式 ? 片內 100 歐姆差分電阻 ? 時鐘資源 ? 優化全局時鐘的 2 路快速時鐘 ? 針對高速 I/O 接口設計的 2 路 IOCLK ? 16 路全局時鐘 ? 最多支持 4 個 PLLs 用于頻率綜合 ? 5 路時鐘輸出 ? 分頻系數 1 到 128 ? 支持 5 路時鐘輸出級聯 ? 動態相位選擇 ? 配置模式 ? 主模式串行 SPI (MSPI) ? 從模式串行 (SS) ? 主模式并行 x8 (MP) ? 從模式并行 x8 (SP) ? JTAG 模式 (IEEE-1532) ? 每個芯片擁有唯一的 64 位 DNA ? BSCAN ? 兼容 IEEE-1149.1 ? 嵌入式硬核 IP ? ADC ? 12 比特逐次逼近寄存器型(SAR) ? 8 個模擬輸入 ? 1MHz 采樣速率(MSPS) ? 集成電壓監控模塊 ? 內置環形振蕩器 ? 封裝 ? LQFP/QFN/FBGA

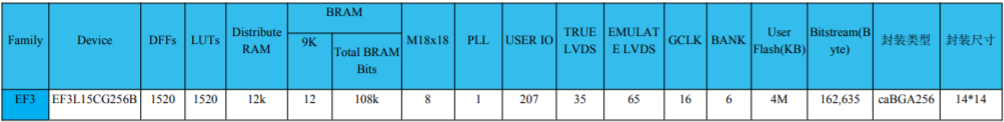

3.2.2 EF3L15 FPGA產品特性 安路 EF3L15 FPGA,定位低成本、低功耗可編程市場。無需外部配置器件、低密度邏輯容量、豐富的存儲器、高達 1Gbps 的 IO 速率等特性,使得 EF3 FPGA 非常適用于高速接口擴展與轉換,高速總線擴展,高速存儲器控制等應用場景。 器件特性 ? 靈活的邏輯結構 ? 1,520 LUTs ? 最大用戶 IO 數量達 207 個 ? 低功耗器件 ? 先進的 55nm 低功耗工藝 ? 內置 Flash ? 內置 4Mb flash,無需外部配置器件 ? 支持快速上電啟動 ? 支持分布式和嵌入式存儲器 ? 最大支持 12 Kbits 分布存儲器 ? 最大支持 108Kbits 嵌入塊存儲器 ? 內置嵌入式存儲模塊(9K),多種組合模式,可配置為真雙口 ? 專用 FIFO 控制邏輯 ? 可配置邏輯模塊(PLBs) ? 優化的 LUT4/LUT5 組合設計 ? 雙端口分布式存儲器 ? 支持算數邏輯運算 ? 快速進位鏈邏輯 ? 源同步輸入/輸出接口 ? 輸入/輸出單元包含 DDR 寄存器支持 DDRx1、DDRx2 模式 ? 高性能,靈活的輸入/輸出緩沖器 ? 可配置支持以下單端標準 ? LVTTL,LVCMOS(3.3/2.5/1.8V/1.5/1.2V) ? PCI ? 通過配置支持以下差分標準 ? LVDS,Bus-LVDS,MLVDS,RSDS, LVPECL ? 支持熱插拔 ? 可配置上拉/下拉模式 ? 片內 100 歐姆差分電阻 ? 兼容 5V 輸入 時鐘資源 ? 16 路全局時鐘 ? 針對高速 I/O 接口設計的 2 路 IOCLK ? 優化全局時鐘的 2 路快速時鐘 ? 多功能 PLLs 用于頻率綜合 ? 7 路時鐘輸出 ? 分頻系數 1 到 128 ? 支持 5 路時鐘輸出級聯 ? 動態相位選擇 ? 配置模式 ? 主模式串行 SPI (MSPI) ? 從模式串行 (SS) ? 從模式并行 x8 (SP) ? 主模式并行 x8 (MP) ? JTAG 模式 (IEEE-1532) ? BSCAN ? 兼容 IEEE-1149.1 ? 增強安全設計保護 ? 每個芯片擁有唯一的 64 位 DNA ? 位流支持 AES 加密 ? 嵌入式硬核 IP ? 內置環形振蕩器 ? 封裝形式 標準尺寸:caBGA256

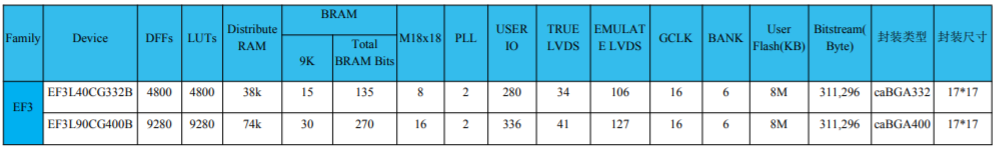

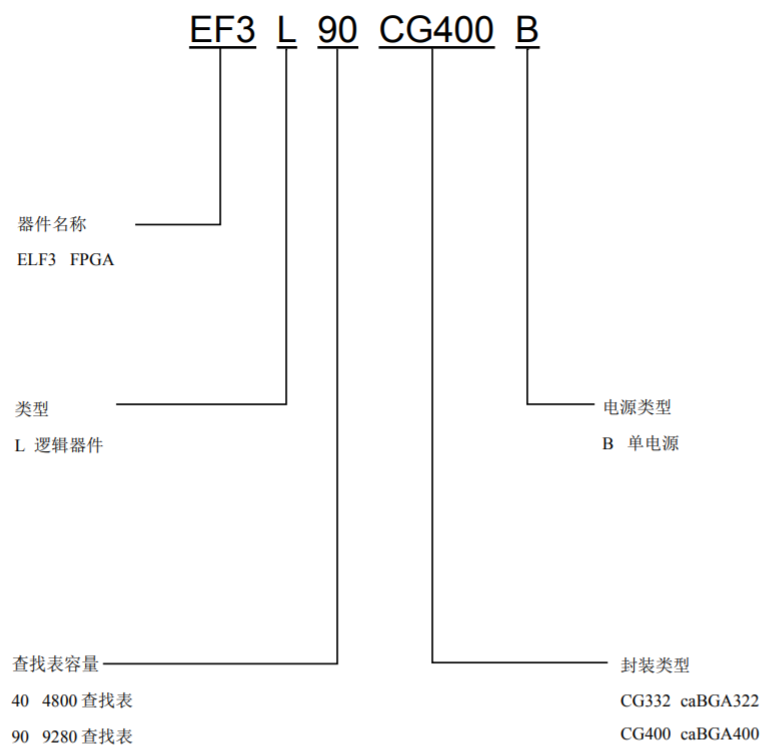

3.2.3 EF3系列FPGA產品特性 EF3 器件是安路科技的第三代 FPGA 產品,定位通信、工業控制和服務器市場,最多支持 336 個 I/O,滿足客戶板級 IO 擴展應用需求。EF3 器件采用先進的 55nm 低功耗工藝,優化功耗與性能,并可以通過低成本實現較高的功能。器件旨在用于大批量、成本敏感的應用,使系統設計師在降低成本的同時又能夠滿足不斷增長的帶寬要求。 器件特性 ? 靈活的邏輯結構 ? 共 2 種器件,規模從 4800 到 9280 LUTs ? 最大用戶 IO 數量達 336 個 ? 低功耗工藝 ? 先進的 55nm 低功耗工藝 ? 內置 Flash ? 內置 8Mb flash,無需外部配置器件 ? 支持分布式和嵌入式存儲器 ? 最大支持 74Kbits 分布存儲器 ? 最大支持 270Kbits 嵌入塊存儲器 ? 內置嵌入式存儲模塊,多種組合模式,可配置為真雙口 ? 專用 FIFO 控制邏輯 ? 可配置邏輯模塊(PLBs) ? 優化的 LUT4/LUT5 組合設計 ? 雙端口分布式存儲器 ? 支持算數邏輯運算 ? 快速進位鏈邏輯 ? 源同步輸入/輸出接口 ? 輸入/輸出單元包含 DDR 寄存器支持 DDRx1、DDRx2 模式 ? 高性能,靈活的輸入/輸出緩沖器 ? 可配置支持以下單端標準 ? LVTTL,LVCMOS(3.3/2.5/1.8V/1.5/1.2V) ? PCI ? 可配置支持以下差分標準 ? LVD,Bus-LVDS,MLVDS,RSDS,LVPECL ? BANK 0 和 2 支持 True LVDS 輸出,所有 BANK 均支持單端和差分輸入 ? LVDS 接口高達 1Gbps ? 支持熱插拔 ? 片內 100 歐姆差分電阻 時鐘資源 ? 16 路全局時鐘 ? 針對高速 I/O 接口設計的 2 路 IOCLK ? 優化全局時鐘的 2 路快速時鐘 ? 多功能 PLLs 用于頻率綜合 ? 支持 7 路時鐘輸出 ? 分頻系數 1 到 128 ? 支持 5 路時鐘輸出級聯 ? 動態相位調節 ? 配置模式 ? MSPI 模式 ? 從模式串行 (SS) ? 從模式并行 x8 (SP) ? 主模式并行 x8 (MP) ? JTAG 模式 (IEEE-1532) ? 增強安全設計保護 ? 每個芯片擁有唯一的 64 位 DNA ? 支持位流 AES 加密 ? 嵌入式硬核 IP ? 內置環形振蕩器 ? 豐富封裝形式 ? caBGA332 ? caBGA400

3.3 EDA軟件與License Tang Dynasty (TD) 軟件是安路科技自主開發的從HDL描述到最終位流下載和片上調試的完整系統,為安路科技所有FPGA芯片產品系列提供簡潔可靠的應用設計開發環境。TD軟件系統采用基于統一數據庫的層次化設計,核心優化引擎采用創新的設計自動化技術,主體流程是性能驅動的逐步精確迭代優化進程。TD軟件系統支持工業界標準的設計輸入描述,提供良好的第三方設計驗證工具接口。 官網有軟件可以直接下載,因為使用人數較少,網上很少能找到使用教程。 特點 ·一切從用戶考慮:界面簡潔、性能可靠、運行速度快 ·創新的軟件算法有效支持ELF、EAGLE、PHOENIX等系列各個規模的器件 ·可擴充的軟件架構快速支持包括單芯片、SIP、IP核在內的多品種產品系列 ·結構化的軟件開發平臺支持對硬件新結構的快速準確模擬和評估 ·用戶設計IP保護和位流加密保護

京微齊力

4.1 公司簡介 京微齊力(北京)科技有限公司注冊在北京經濟技術開發區,總部設于亦莊,在中關村設有研發中心;在上海,深圳有技術支持,市場銷售團隊。 京微齊力是除美國外最早進入自主研發、規模生產、批量銷售通用FPGA芯片及新一代異構可編程計算芯片的企業之一。公司團隊申請了近200件專利和專有技術(含近50件PCT/美國專利),具備獨立完整的自主知識產權。其產品將FPGA與CPU、MCU、Memory、ASIC、AI等多種異構單元集成在同一芯片上,實現了可編程、自重構、易擴展、廣適用、多集成、高可靠、強算力、長周期等特點。產品所服務的市場將迅速超過幾百億,而隨之衍生的終端模組、應用方案的市場規模將達數千億。得益于混合架構,這類芯片硬件結構可通過軟件來定義,產品能跟隨市場的需求發展而相應變化。相比傳統專用芯片平均2年的生命周期,應用于多個產業鏈的新型異構可編程計算芯片的生命周期可長達10年。 公司技術與產品將涵蓋可編程FPGA內核,異構計算與存儲架構、芯片設計、軟件開發、系統IP應用等相關技術領域。公司提供核心關鍵芯片和相關市場應用系統解決方案。 基于先進的創新可編程技術,研發新一代面向人工智能/智能制造等應用領域的AiPGA芯片(AI in FPGA)、異構計算HPA芯片(Heterogeneous Programmable Accelerator)、嵌入式可編程eFPGA IP核(embedded FPGA)三大系列產品,產品市場將涵蓋云端服務器、消費類智能終端以及國家通信/工業/醫療等核心基礎設施。 官網:http://www.hercules-micro.com/about/index.html

4.2 FPGA系列

| 種類 | 工藝 | 概述 |

| HME-R(河)系列FPGA | 40nm | 詳見官網介紹:http://www.hercules-micro.com/product/index86.html |

| HME - M7(華山)系列FPGA | - | |

| HME - M5(金山)系列FPGA | - | |

| HME - M1(衡山)系列產品 | - | |

| HME - P(飛馬)系列 | 40nm | |

| HME-H1D03(大力神)系列產品 | - |

4.3 EDA軟件與License FX - 伏羲軟件簡介 FX是自主研發的一款EDA設計工具,您可以使用它快速、高效地進行FPGA和SoC應用設計。用戶通過使用FX完整的EDA工具鏈與豐富的IP資源,可以有效的進行快速應用研發,縮短產品開發周期。同時FX友好的交互式集成開發環境可以支持多種廣泛使用的第三方設計工具進行協同設計,從而進一步加速用戶的設計與驗證過程。 官網提供下載鏈接及License申請。

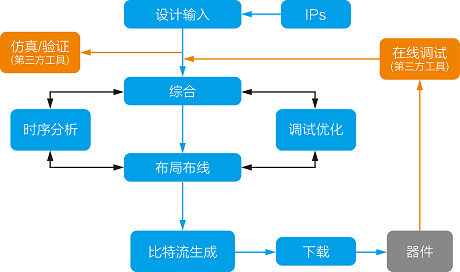

主要功能 ·友好易用的圖形化用戶界面 ·支持Verilog和VHDL混合編程 ·與第三方工具無縫連接 (Prime Time和ModelSim等) ·提供豐富的IP(基于IP Wizard) ·支持命令行操作界面 ·支持遠程下載編程 ·比特流加密 ·片上調試功能 設計流程圖 FX是自主研發的一款EDA設計工具,您可以使用它快速、高效地進行FPGA和SoC應用設計。用戶通過使用FX完整的EDA工具鏈與豐富的IP資源,可以有效的進行快速應用研發,縮短產品開發周期。同時FX友好的交互式集成開發環境可以支持多種廣泛使用的第三方設計工具進行協同設計,從而進一步加速用戶的設計與驗證過程。

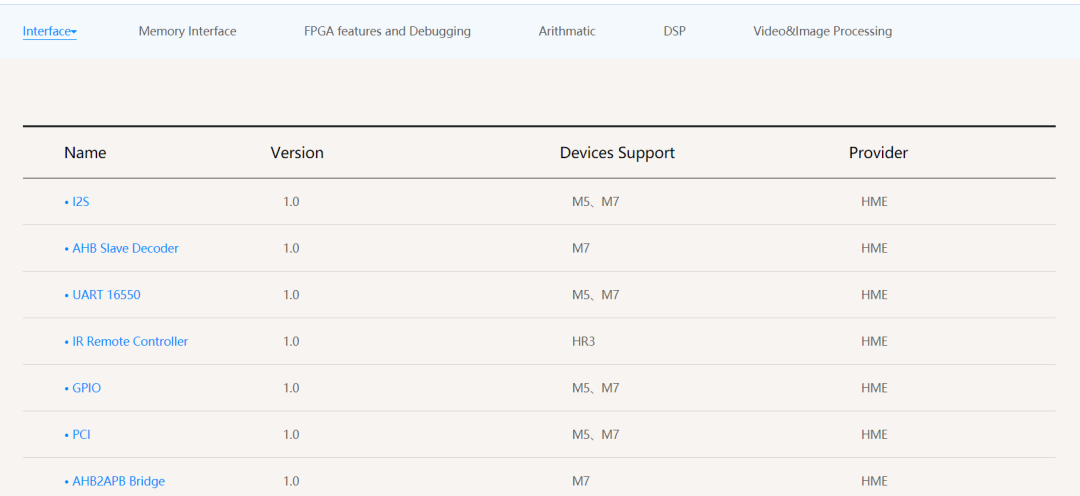

官網提供了一些常見IP

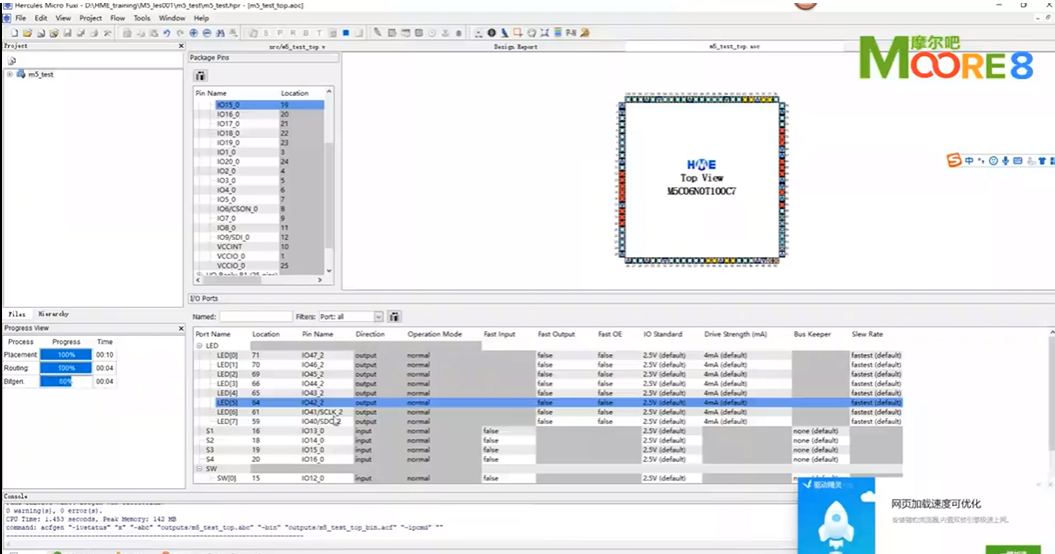

軟件截圖:

有沒有很熟悉? 軟件使用視頻鏈接:http://www.hercules-micro.com/content/details30_797.html

復旦微電子

5.1 公司簡介 上海復旦微電子集團股份有限公司是從事超大規模集成電路的設計、開發和提供系統解決方案的專業公司。 因為復旦微電子FPGA只對軍工、研究院所供貨,所以這方面信息不方便透漏太多,網上也基本上無此相關信息和使用教程,這里也不多說了,如果你是這兩方面應用應該很好聯系到官方,相關的信息也會獲得,如果不是拿到信息也沒有什么用,因為你買不到芯片。 5.2 FPGA系列

K7、V7 325、690系列都有,大容量彰顯實力,并兼有抗輻射產品、ZYNQ產品(復旦微電子的FMQL系列,該FMQL系列中兩款芯片中FMQL10S400對標的Xilinx的7010,FMQL45T900對標的是Xilinx的7045。)

5.3 EDA軟件與License

可惜或只軍工可用,雖對外售賣,但得是軍品、研究院所項目。

旅行的意義-總結

毫無疑問,中國FPGA產業與同行的領先廠商相比是有差距的:

按照京微齊力王海力的說法,從芯片角度看,國內的FPGA與國際廠商有兩代半的工藝線。現在國際廠商已經在16nm產品上量產了,而國內廠商目前只做到40nm,28nm產品還在推進階段,他強調。

如果從軟件和生態方面看,國內FPGA企業與國際領先廠商之間更是有八到十年的差距。如果想追上,尤其是在中高密度產品上追上國際領先者,國內FPGA廠商還需要很長的一段路要走。

高云半導體工程副總裁王添平先生也表示,目前活躍在市場的國產FPGA產品中,多以中低密度產品為主。這些產品從定義、芯片設計、生產工藝、芯片封裝、應用軟件、乃至實際銷售,都有不錯的表現,高云的低密度產品在某些細分領域正在全面取代國外廠商。但在他看來,對于國內大部分的中高低密度的FPGA,其架構都逃不開LUT+布線的概念,具體到產品,各自側重的技術、IP乃至相應的應用市場也都是各有針對性。如果從這個角度看來,國產廠商在中高密度FPGA的技術水平與國際領先廠商相比,在硬件設計和軟件方面還有一定的差距。

雖然差距很明顯,但對于國內廠商來說,負重前行是一種必然的使命。盡管FPGA全球市場銷售額近年來的年增長率一直徘徊在個位數,但其進入各類新興市場如大數據、人工智能、云計算、硬件加速、汽車自動駕駛以及消費等領域的速度卻非常吸引眼球,乃至人們對FPGA特別是國產FPGA的未來發展充滿期待,資本進入該領域也日趨活躍。

-

FPGA

+關注

關注

1643文章

21968瀏覽量

614291 -

計數器

+關注

關注

32文章

2284瀏覽量

96046 -

工業控制

+關注

關注

38文章

1527瀏覽量

86725

原文標題:國產FPGA概況

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

效率大升!AI賦能鴻蒙萬能卡片開發

國產FPGA這一“萬能芯”的發展概況

國產FPGA這一“萬能芯”的發展概況

評論