隨著時代的不斷發展,科技的不斷創新,軟硬件設備的功能逐漸增多,數字電路變得越來越復雜、越來越集成化,大規模集成電路在芯片設計、數據儲存中被大量應用,傳統的設計規則與經驗已經無法滿足信息時代的要求。為了保障系統設計的可靠性與通用性,可以從以下3方面對數字電路進行優化改進:一是大規模使用現場可重構器件,使硬件電路的實現載體和評價方式變得更加優化,以推進數字電路的優化。二是優化算法,從而全面優化搜索性能。例如使用代入遺傳算法的過程中,可以采用新的結構來提高數字電路的設計模型,并將下載的最好染色體保留在可重構器件上,用染色體算法進行運算,進而使運算和操作變得更加優化。三是利用軟件模型,將期望的數值和電路優化設計所得到的結果與當前的實際情況進行對比,方便優化過程中直觀明確地了解優化方案的效果,進而提出更加完善的優化設計。

1模塊化數字電路簡介

1.1模塊化的設計理念

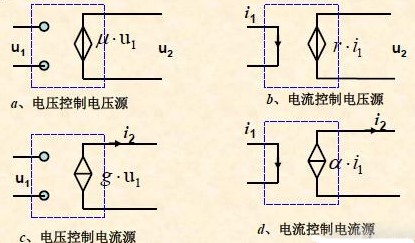

本文提出的自頂向下的模塊設計理念,將復雜的數字電路設計分解、細化為一系列相對簡單的子電路,將復雜、繁瑣的電路設計變為簡單、容易的設計,這種將復雜難懂的問題轉換為簡單易懂的問題的方式在于思維的轉變。在本文中,具體描述數字電路功能時,可在數字電路設計上搭建一個真值表,對于那些可以優化的過程,需把真值表看成一個完整的數字電路系統,對數字電路的輸入變量和輸出變量進行模塊化設計,讓整個過程變得更加簡單方便。把輸入部分的位數看作子功能輸入信號,把其余位數看作通信信號,這樣就可使整個算法變得簡單。通俗說就是利用優化電子電路的輸入和輸出來改變傳統的電路算法,使用模塊化設計,優化計算系統的獨立性。

與傳統電路算法相比,模塊化進化算法具有兩個優勢,一是可以讓功能電路的選擇更加準確;二是能夠縮小子系統輸入和輸出的位數占比,降低算法復雜程度,提高算法的成功概率,減少算法計算時間。

1.2數字電路優化設計

數字電路設計劃分為許多個小模塊,為了快速、高效地尋找出一種最優的電路設計目標,引入遺傳算法,遺傳算法的過程如下。

1.2.1染色體編碼

在對染色體定向編碼過程中,首先要進行遺傳算法的運算時間規劃,對電路模塊化結構的染色體進行優化,以提升運算時間。進行染色體編碼時,可將染色體分成更為獨立的邏輯段,每個獨立的邏輯段都表示一個小的子系統,在子系統當中采用更加精準的門級電路進化方式,讓每個子系統都包含編碼、通信信號和聯線編碼,這樣就可以讓整個染色體變化的過程變得更為簡單快捷。遺傳算法的染色編碼為實數編碼,把所有的子系統整合為一個大的染色體,每個子系統既可以獨立進行并排凈化,又可以降低大范圍的電路資源浪費,而且每個子系統之間既相互獨立又相互聯系。

1.2.2適應度函數設計

在數字電路設計中,適應度函數有著非常重要的作用,適應度函數設計的優劣可以對最終目標產生直接影響。可對適應度函數的輸入值與期望值進行更為科學的對比研究,讓整個評價系統變得更加準確,評價過程采用的標準就是操作結果;數字電路中遺傳算法的使用公式可以表示電路功能的正確度。

1.2.3選擇操作

在進行遺傳算法的過程中,需選擇很多操作,其中包括競爭選擇方法和輪盤法。本文采用模塊化原則,故而傾向選用競爭選擇方法。競爭選擇方法就是從父代的種族當中挑選多個遺傳個體,然后將這些個體采用適應度函數進行比較,最終選擇最好的個體來進行交叉算法,不斷地進行重復,直到整個過程操作完畢。

1.2.4交叉算法

如果使用交叉算法進行操作,就需要從父代當中隨便選擇兩個染色體進行雜交,以便把優秀基因保留下來,并且較大程度地保留特別優秀的基因。采用交叉算法可以使種族的基因更加優化,讓整個種族變得更加發達。在進行交叉算法的過程中,一般采用均勻交叉方式或兩點交叉方式及單點交叉方式。均勻交叉方式就是將染色體的很多優點進行交換,讓它們更加有利于種族延續,本文采用的是均勻交叉操作方式。

1.2.5變異算子

變異算子是把染色體中的一些基因按照相應的概率進行變異操作,所選取的概率值越大,遺傳過程中的多樣性就會越大。變異操作僅在父代上進行就可改變某一個基因,使種族發生整體改變。本文中變異算子的具體操作是選擇一條染色體,根據變異概率決定是否變異,如果取值為零,那么就不進行變異;如果取值不為零,那么就進行文件的變異操作。

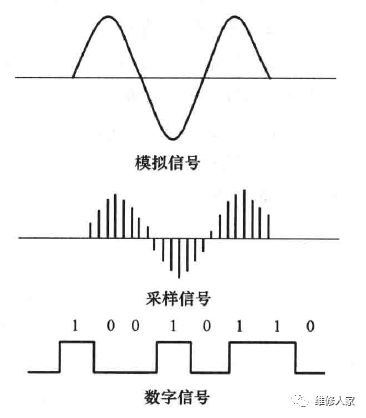

2降低功耗的具體措施

1)優化方向。使用組合邏輯+時序邏輯+存儲的方法。時序電路的特點:輸出與當時的輸入值和電路之前的狀態有關系;組合電路功能的特點:任意一個時刻的輸出僅僅與該時刻的輸入有關系,和電路原來的狀態沒有關系,可以采用結合的方式來減小功耗。

2)組合邏輯。通過算法優化來減少門電路,復用模塊,優化算法。

3)時序邏輯。盡量降低采用沒有用的register和非功能性的register,最好不要采用帶復位reg,數據打拍。

3存儲模塊及不同規格

RAM的選擇存儲模塊選擇RAM還是register,應根據需求綜合考慮。規模小的存儲結構可以采用寄存器實現(規模小于8×32的FIFO);規模較大的存儲模塊可采用RAM實現(規模大于8×32的FIFO)。同等容量下,register比RAM功耗大,所以大容量存儲采用register會造成更大的功耗。如果是小規模存儲,采用register面積開銷比較少,且相對于RAM功耗增加不明顯。

拆分RAM能夠減少功耗;采用低主頻高密度的RAM,減小使用面積能夠加大位寬降低訪問頻率;把多端口的RAM換成單端口的RAM或采用共享RAM的方式都能夠減小使用面積與功耗。

4減小面積的措施及電路時序的優化

1)減小面積的措施。在組合邏輯方面,除了采取優化算法減小門電路,還可以采用共享資源、復用模塊等方法減小面積。采取組合邏輯+時序邏輯+存儲的方式同樣可以減小面積。

2)電路時序的優化。通過優化算法可以降低組合邏輯的層數;邏輯復制可以改善路徑延時的情況。在流水設計的過程中插入寄存器可以更好地減少延時情況。除此之外,優化關鍵信號可以將信號轉變為控制器的控制信號,從而將關鍵路徑信號調整到離輸出很近的位置,使得信號更快地被接收。如果想對晚到的信號進行優化,通常會采取兩種方式,一種是把數據信號變為慢信號(優化ifelse嵌套);另一種是把控制信號變為慢信號(優化ifelse嵌套)。

5系統速度和資源的優化

5.1速度優化

通常而言,優化速度相比于優化資源更為重

要,需優先考慮。速度優化包括FPGA的結構特性、HDL綜合器性能、PCB制版情況等,也包括Verilog的編程風格。下面探討4種電路結構方面的速度優化方式。

1)流水線是一種在成組的邏輯之間添加寄存器的方法,它在很大程度上提升了設計電路運行的速度。在使用了兩級流水線之后,組合邏輯塊的延時大大減少,兩級組合邏輯塊的延時分別為T1,T2,設置T1≈T2,且Ta=T1+T2,Tclk可接近T1,其最高工作頻率為fmax≈fmax1≈fmax2≈1/T1≈1/T2,使用流水線的最高工作頻率比沒有使用流水線的速度提升了將近一倍。

2)使用流水線加法器實現八位加法器。用3個4bit加法器以及多個鎖存器實現。

3)乒乓操作法。乒乓操作法是一種數據緩沖優化設計技術,可以將其看作是不同的流水線技術,通過輸入數據流選擇單元和輸出數據流的單元,按照不同的方式進行切換,將緩沖數據流中的數據無接縫地傳遞到處理模塊,進而進行接下來的操作。

4)加法樹法。想要實現A+B+C的結構,可先實現A+B,再將A+B的和鎖存一個時鐘周期之后再與C相加。

5.2資源優化

5.2.1資源共享

資源共享采取選擇、復用來共享使用該模塊,達到降低使用資源、優化減小面積的目的。可以選用規模更小的可編程器件對資源進行優化,以降低成本,提升性價比,為后續技術升級保留可編程的資源。這樣做可以減少資源的耗用,減輕器件的耗費。

5.2.2優化組合邏輯

在優化過程中可以進行組合邏輯的優化,以最大程度減少資源浪費。首先在流水線設計過程中進行優化,在不同的組合邏輯之間插入寄存器,以盡可能減少出現延時的可能。其次可以采用模塊復用、資源共享的方式,減少邏輯運算過程中占用的面積。此外,還可以采用邏輯復制的方式,減少延遲情況的產生;將關鍵路徑信息轉變為控制器的控制信號,再將信號調到離輸出很近的位置也是減少路徑運輸時間的方法。

5.2.3串行化

串行化可以將巨大的邏輯塊分割成小的邏輯塊,并在運送過程中尋找相同的邏輯塊,用多個時鐘周期完成相同的功能。可以使用并行邏輯設計,或者采用串行化設計,只需要用一個八位的乘法器和一個十六位的加法器及一個附加信號start即可。

6結束語

通過對電路的優化設計可以讓整個電路變得更加模塊化,在進行數據儲存及芯片設計過程中降低設計復雜度,使設計變得更為方便。數字電路采用模塊化設計方式可以使遺傳算法得到更多的優化,提高了數字電路的準確性和可靠性;這種方法在現階段適應于比較精密的儀器,可整體提高機器設備的自動化和智能化水平。

-

數字電路

+關注

關注

193文章

1637瀏覽量

81605 -

優化設計

+關注

關注

0文章

7瀏覽量

7214

發布評論請先 登錄

模擬電路與數字電路的區別詳解

如何對數字電路進行優化設計

如何對數字電路進行優化設計

評論