美國AI初創企業CerebrasSystems旗下的明星產品WES(Wafer Scale Engine)芯片即將進入新一代,在日前舉辦的Hotchips 32會議上,CerebrasSystems公布了WES 2代芯片的相關信息。

據悉,WES 2代芯片核心數翻倍到了85萬個,晶體管數量翻倍到2.6萬億個,最關鍵的是,將從16nm工藝進入7nm工藝。

造出世界最大芯片,Cerebras Systems是家什么樣的公司?

作為一家在2016年才創立的公司,CerebrasSystems的資歷并不算長,但是卻經歷了三輪融資,分別是2016年5月份的2700萬美元的A輪融資,2017年1月2500萬美元的B輪融資,隨后不到一年時間里,CerebrasSystems再次融資6000萬美元,彼時估值達到8.6億美元。

恰好人工智能產業也是在那個時候開始盛行,CerebrasSystems也因此被許多人看好。而這家公司造AI芯片就是奉行一個路子:“簡單,粗暴”。

在去年CerebrasSystems推出巨型芯片WES的時候,就引起了業界轟動。在關于WSE介紹的白皮書中,有這么一句話——“通過加速人工智能計算,WSE清除了阻礙人工智能進步的最大路障——時間。將訓練時間從幾個月縮減為幾分鐘,從幾周減少到基瞄。讓深度學習實踐者更快的驗證自己的假設,從而不用去擔心一些體系機構導致無法測試或者太大風險。WSE降低了好奇心的成本,加速了人工智能新思想和新技術的到來。”

在WES這顆采用臺積電16nm工藝,面積46000平方毫米,擁有1.2 萬億個晶體管40萬個核心,片上18G內存的芯片上,性能之強大讓當時的芯片“大塊頭”甘拜下風。

比如英偉達的GV100芯片也不過用上了211億晶體管,核心面積815mm2,所以WSE芯片晶體管數量是最強GPU芯片的60倍,面積則是它的56倍多。WSE與當時的CPU芯片相比同樣震撼,AMD的64核EPYC二代處理器才320億晶體管,封裝總面積也不過4410平方毫米,光是核心面積WSE就是EPYC二代處理器的10倍有余。

從性能上來看,WES芯片帶寬超過100Pb/s,一般的計算芯片以Tb/s級別的單位都難以跟起比較。總之,WES芯片的出現堪稱芯片工藝史上的一大“奇跡”。不出預料的話,WES 2代芯片性能跟價格都會大幅提升。

雖然CerebrasSystems造出芯片的芯片性能確實強大,但是投入的成本也十分高昂,不是哪個公司都有這個實力“燒錢”玩的。據悉一塊WES芯片的價格約在200萬美元(約合人民幣1384萬元)左右,在當時也只有美國國家科學基金會(NSF)為了打造超算CS-1而購買了WES芯片。

性能為先,芯片是不是越大就越好?

目前,象CerebrasSystems一樣專門走巨型芯片路線的企業少之又少,這可能除了是他們的企業特色以外,也涉及大整個芯片產業對于芯片大小的共同認知。

之前就有人提出過這么一個問題,現在廠家都專注與縮小晶體管尺寸,目的就是為了在芯片內部打造更大規模的集成電路,那為什么不通過增大芯片的面積來提高性能?

首先從構造上來說,如果是將芯片面積越大來保證刻畫更多的電路,實際上不會減少電路布線的復雜程度,反而還更難。大芯片也也意味著片內器件之間的傳輸要走更長的互連線進行傳輸,造成信號傳輸延遲,可能有人會覺得都是在一塊芯片上,能延遲多少?可是當你將不同芯片內部放大一百、一千倍來看就會發現延遲快慢的差距了。而更長、更多、更復雜的互連線也意味著在芯片設計的過程中,工程師要更周全地考慮阻抗匹配、信號中斷等問題。

二是功耗成本問題,現在的芯片廠商為什么想把芯片做小?就是為了降低功耗,芯片的功耗直接和金屬的寄生電容成正比,更寬的線寬會導致更大的功耗。同樣,晶體管體積縮小也是為了降低功耗,可是同時卻增加了翻倍的數量,還怎么談降耗?同時還需要提供更大的供電輸入,更強的散熱處理,都會讓成本增加。

最后一個也是最重要的一個問題,良品率。很多公司都會提到良品率問題,一般來說芯片良品率隨核心面積指數降低,成本指數上升。芯片的設計和生產過程極度復雜,尤其是芯片面積越大,在晶圓片上刻畫的電路也越多越復雜,越容易失敗。當然有些失敗不會影響整個芯片的大體性能,只是說會讓其產生“瑕疵”,而這種有瑕疵的芯片也刻意正常使用,但就是廠商可能會把有瑕疵的模塊直接關閉,芯片也就缺失某些功能。

總的來說,巨型芯片的買家少之又少,更多的人還是以考慮芯片功能、成本、性價比為首選。為了提高專用性能而付出昂貴的價格和更多的功耗,確實不劃算。

-

芯片

+關注

關注

459文章

52137瀏覽量

435723 -

晶體管

+關注

關注

77文章

9976瀏覽量

140582 -

AI

+關注

關注

87文章

34129瀏覽量

275229

發布評論請先 登錄

精密幾何測量技術在電子芯片制造中的重要性

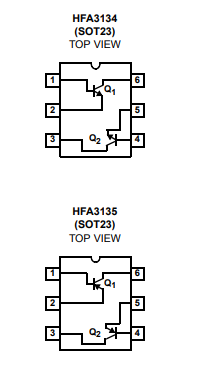

HFA3134超高頻晶體管應用筆記

7納米工藝面臨的各種挑戰與解決方案

IBM與Rapidus在多閾值電壓GAA晶體管技術的新突破

今日看點丨 傳蘋果2025年采用自研Wi-Fi芯片 臺積電7nm制造;富士膠片開始銷售用于半導體EUV光刻的材料

所謂的7nm芯片上沒有一個圖形是7nm的

世界最大的AI芯片升級,芯片核心數和晶體管翻倍,將采用7nm工藝

世界最大的AI芯片升級,芯片核心數和晶體管翻倍,將采用7nm工藝

評論